利用FPGA设计软件开放性性能优化MAX+PLUS II仿真软件性能

描述

随着数字技术的飞速发展,电子工程师在设计中越来越多地采用FPGA来实现复杂的数字功能,不仅仅是简单的时序逻辑,更多的是诸如数字滤波器、信号处理算法的实现等。这样我们就必须要对FPGA设计进行全面的性能分析,而不仅仅是时序的验证,这就对FPGA设计软件的仿真功能提出了更高的要求。而现有的一些流行的FPGA设计工具并不能满足这一要求。

MAX+PLUS II是ALTERA公司为自己的系列EPLD、FPGA提供的功能强大的设计及仿真软件。在该软件中,提供了从多种方法输入、编译一直到仿真的一系列配套功能,对于那些不是很复杂的时序逻辑设计来说,可以在一个软件内方便地完成所有的设计及仿真工作。而对于那些复杂的设计则显得力不从心了。

举一个例子:对一个基于FPGA设计的雷达信号处理机,我们关心其在给定发现概率和虚警率的前提下的最小可检测信噪比,或者在某一给定信噪比条件下其Pd、Pf是否能满足要求。虽然在设计之前肯定已经做了诸如可行性分析、性能分析等一系列的工作,但是由于数字实现必须考虑的一些问题,如字长效应、算法简化等,有可能使具体实现的性能比之理论分析有所下降,这个下降到底有多大?另外,采用的信号处理算法还有哪些没有发现的缺陷?对设计者来说,能够完全在软件环境中通过仿真来解决这些问题远比在不成熟的硬件环境中反复地调试、修改来的有效率,且有更大的弹性,更容易进行。

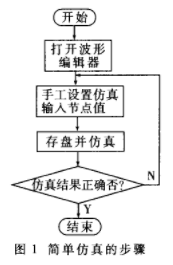

然而,当我们想通过MAX+PLUSII软件自带的仿真工具对复杂设计的性能作一个评估时,就会碰到许多困难。一般来说简单仿真的步骤如图1所示。其中,手工设置仿真输入节点值只适用于输入信号比较简单的情况,而对于复杂的输入信号就无能为力了。如上述雷达信号处理机的输入信号,应该是许多个周期的雷达同步信号、雷达回波信号加上取决于接收信道的带限噪声构成的(后两者应有给定的信噪比关系)。这类输入信号不仅必须经严格计算得到,而且数量巨大,很难由手工输入。

另外,一般我们对仿真结果的分析也仅限于直接观察,只能对相对较简单的结果作出判断。而雷达信号处理机则必须做蒙特卡洛实验(海量实验)来统计其性能(如统计给定信噪比下的Pd、Pf),或对处理结果进行各种分析(如时频分析)来判断处理器是否最佳等。这样,对仿真结果的分析也不能简单地判断,必须经专门的数学计算才能给出结论。

由此看来,MAX+PLUSII的仿真功能已经不能满足对复杂设计进行仿真的要求,我们必须另找方法。当然,如果有像COSSAP这样的软件的话,就不存在上述问题了。但对于大多数设计者来说,他们一般很难有机会接触到这些工作站上的大型软件,更普及的是像MAX+PLUS II、MATLAB这样的通用工具软件。

我们知道,MATLAB是MathWorks公司推出的一种面向科学与工程计算的高级(语言)软件,它集科学计算、自动控制、信号处理、神经网络、图像处理等于一体,具有极高的编程效率。它可以极方便地产生各种信号,进行各种变换、统计,另外它的绘图功能也极为强大。它的这些特点正好可以弥补MAX+PLUSII在仿真功能上的缺陷。因此,本人在这里介绍一种利用MATLAB来产生复杂的仿真输入信号,并对仿真输出信号进行分析的方法。

1 联合仿真方法介绍

1.1 联合仿真流程

我们先介绍MATLAB与MAX+PLUSII联合仿真的流程,以使大家心中有一个概念。然后再分别介绍各部分的实现。联合仿真流程为:

(1)先在MATLAB中产生原始信号,并转换为2/16进制序列;

(2)利用自己编写的MATLAB函数按一定格式生成向量文件(*.vec,纯文本文件);

(3)在MAX+PLUS II中,打开你要仿真的FPGA源文件,设置为“当前工程”并作编译;

(4)打开simulator,选“FileInputs/Outputs”,输入在MATLAB中生成的向量文件名,按:“确定”按钮生成*.scf文件;

(5)进行仿真;

(6)选菜单“FileCreate Table Files”,生成相应的*.tbl文件(纯文本文件);

(7)回到MATLAB下,运行自己编写的函数,自动从Table文件提取需要的输出数据、进制转换(变为十进制),生成仿真结果序列;

(8)对结果序列进行进一步分析、处理。

1.2 仿真输入文件

在MAX+PLUS II的仿真输入文件中有一种文本形式的向量文件(VectorFile),其后缀名为“*.vec。这种文件是用一定格式的文本来描述仿真信号的。我们可以很方便地使用任何纯文本编辑器来书写文件,定义仿真时间长度,以相对/绝对时间单位来定义周期重复的输入信号(如时钟)和其它复杂输入信号。下面给出一个该文件的简单例子:

%时间单位缺省为以%

START 0; %定义仿真开始、结束时间%

STOP1000;

INTERVAL 100; %定义时间步长:100ns%

INPUTS CLOCK;

PATTERN

01; %相对向量值定义:CLOCK %

%每100ns翻转一次%

INPUTS DATAINX DATAINY;

PATTERN %定义两个输入信号%

%DATAINX和DATAINY%

0> 00

220> 10

320> 11 %绝对时间描述%

570> 01 %大于号前为绝对时间值%

720> 11 %大于号后为两个输入值%

;

INPUTS CLEAR;

PATTERN

0> 1 %产生宽度100ns的清零信号%

100> 0 %100ns后CLEAR信号保持高电平%

在这个例子中,定义了一个周期为200ns的时钟信号、一个100ns以前起作用的清零信号(高电平有效)以及两个输入信号DATAINX、DATAINY。在实际使用时,我们可以用同样的方法方便地产生时钟、复位等常用信号。而对于复杂的输入信号,可以先用MATLAB来产生,然后以相对时间的方式写入向量文件。

在产生复杂输入信号之前,必须注意以下几点:

第一,MATLAB产生的是浮点或整数信号,而数字模块的输入为N位二进制数,这之间有一个进制转换的问题。因此,我们先要根据要采用的A/D位数对原始信号进行量化。

第二,在MAX+PLUS II的仿真器中,数据可以采用2/8/10/16进制显示格式,但其十进制显示用的是无符号数的方式,在表示那些补码形式的2/8/16进制数时会发生错误,因此必须把输入信号转换为2/16进制数。

第三,进制转换程序必须自己编制。因为MATLAB是用字符串来表示2/8/16进制数的,虽然有一些进制变换的函数(如HEX2DEC、DEC2HEX等),但尚不能满足需要,必须在此基础上自己编制新的函数。

1.3 仿真输出文件

向量文件产生后,就可以进行仿真了,仿真结果转换成Table文件输出。Table 文件示例如下。

INPUTS clk reset din;

OUTPUTS y;

UNIT ns; %定义时间单位%

RADIX HEX; %定义显示进制%

PATTERN

% r %

% e %

% csd %

% lei %

% ktn y %

0.0>X 0 0000=0000

40.0>X 1 0000=0000

50.0>0 1 0000=0000

……

1475.0>1 1 0000=0000

1500.0>X X XXXX=XXXX

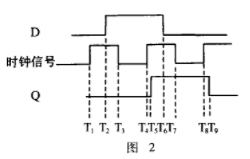

Table文件的构成与向量文件大致相同。它的开始部分是注释(同样是以%…%标注的文字),接着是对输入/输出信号、时间单位、显示采用进制的定义,第三部分就是对输入/输出信号在仿真后的列表。其中,“>”号以前的是时间值,“=”号后面则是我们关心的仿真输出结果了。根据Table文件的这些特点,我们可以编制MATLAB函数将关心的东西(如时间值、某输出结果)提取出来形成数据序列,以便后续处理。在这里要注意一个问题,就是Table文件中会对每一个信号的变化时刻都进行记录,我们用图2的一个简单的D触发器的部分仿真时序来作说明,图中示出了D触发器的输入信号D、时钟,以及其输出信号Q,在这一段仿真中,Table文件会记录从T1~T9的9个信号变化的时刻,这使得输出信号的每一个值被记录了多次。如果我们对此不加甄别就照单全收的话,就会对此后的分析工作带来麻烦。因此,对于同步数字系统,我们只应提取那些我们关心的时钟上沿/下沿时刻的输出值。

2 应用实例

本人在自己的设计工作中使用了以上介绍的这种方法。我设计的是一个单脉冲雷达回波信号处理机,基本原理是信号的能量积累后检测,其中采用了较复杂的信号处理算法,在原理验证阶段采用的是固定门限检测。在用MAX+PLUSII设计完该信号处理机后,现实的问题就是要在给定Pd、Pf的条件下,根据具体的算法确定检测门限。我们先在接收机上对接收机噪声用示波器进行了测量并存储了大量数据,然后将测量结果读入MATLAB,形成一维数组。然后按以上介绍的方法对噪声数据进行两种处理:一是产生模拟回波信号(或采用真实回波信号采样序列)、信号噪声按一定信噪比混合、加上同步脉冲后形成多个周期的“有信号回波”,二是完全是噪声的“无信号回波”;再结合其它必要的输入信号(如时钟信号、复位信号等)生成向量文件,在MAX+PLUSII中仿真后,分别提取仿真结果中的“有/无信号”的两种能量积累结果进行分析,初步确定检测门限,并由此结合理论分析对其检测性能进行评估。

当然,这种完全在软件环境中进行性能分析的方法并不是万能的,它只能也只应起到辅助的作用,我们采用它的目的是为了使我们的设计变得更经济、更省时、更可靠。毕竟,一个设计最终是要形成硬件,并在实际应用中去真正检验它的品质的。

总之,由于FPGA方便灵活的特点,使得这种器件在数字设计领域的应用越来越广泛。而作为一个设计者,必须利用FPGA设计软件的开放性,充分利用其它各种手段来保证我们的设计的可靠性,提高设计的品质。

责任编辑:gt

-

第二章MAX+Plus II应用简介2022-07-13 507

-

MAX+Plus ii 软件2013-11-19 2315

-

MAX+PLUS II软件下载入口2012-09-14 2186

-

max+plus问题2012-08-18 3665

-

谁有max+plus的软件的 急急!!!!!!谢谢2012-03-09 2245

-

MAX PLUS II软件的学习2009-10-24 3041

-

MAX+Plus II应用介绍及系统特点2009-10-09 5079

-

利用MATLAB增强MAX+PLUS II的仿真功能2009-06-20 1141

-

MAX+PLUSⅡ的设计处理2009-03-13 1427

-

Altera MAX+plus II 介绍2008-09-24 8393

-

Max+Plus II简易用户使用入门指南2008-09-11 2781

-

基于MAX+plusⅡ开发平台的EDA设计方法2008-06-16 5018

全部0条评论

快来发表一下你的评论吧 !