一文读懂算术逻辑单元ALU

可编程逻辑

描述

算术逻辑单元

1.算术逻辑单元ALU,CPU是由运算器和控制器构成的,这里讲的是运算器。运算器既能完成算术运算也能完成逻辑运算。ALU是能完成一系列算术运算和逻辑运算的电路,是计算机的核心。实际上来讲,输入到计算机里的数据,ALU控制其进行算术运算还是逻辑运算,包括具体是哪种算术,哪种逻辑,最后将计算好的数据输出。

2.一位的ALU是指操作数都是一位的二进制数,ALU中S的位数决定着能够进行计算的种类,如果S为两位,那么它只能提供四种操作码。S的不同码,代表着不同的计算,就是对不同的计算进行了编码。如果S为三位的操作码,那么三位二进制的编码有八种情况,如果算术操作和逻辑操作各有四个,那么我们就必须对S2S1S0进行详细的划分,S2为0时,后续的四种编码均用来代替算术运算,S2为1时,后续的四种编码均用来代替逻辑运算。ALU存在一个功能表,输入为n位的S变量,输出为相应的具体运算。计算机整体运算器的真值表和S是不一样,着眼点更大,输入是操作数,经过S的选择控制,输出结果。

3.貌似需要将S,A,B,F的位数统一起来,S是几位的设定,那么输入A,B,输出F也同样是几位的设定,如果计算结果超过了,就采用进位的办法。

4.算术逻辑单元的讲解,是从一位的ALU入手,后续的n位的ALU是由很多一位的ALU集成在一起。这里运用前面的概念,一位的ALU是指S,A,B,F的位数均为1位么?

设计ALU本质上是设计一位的ALU单位,然后级联起来就够了。

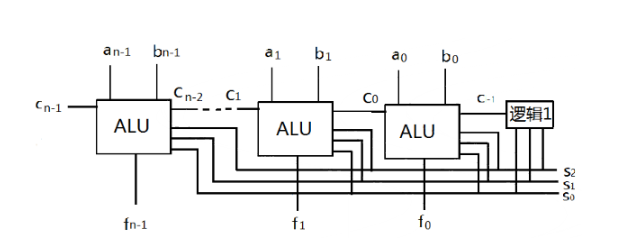

以上述的这张ALU的逻辑图看,我们对于S,A,B,F的位数是否统一的理解应该是这样的,n个一位的ALU算术逻辑单元中,每一个算术逻辑单元均有两个操作数且是一位的ai,bi,输出数fi,i从0到(n-1),这样n位的ALU中有两个输入数A和B,一个输出数F,均为n位,只是这n位是从不同的一位算术逻辑单元输入的。那对于操作码,它的位数我觉着没什么要求,你想,具体要经过多少运算其实是无所谓的,和输入,输出数据的位数没有任何关系。

5.我们先来仔细分解一位的ALU算术逻辑单位的内部逻辑图,最后寻求n位的ALU,只要将它们级联起来即可。

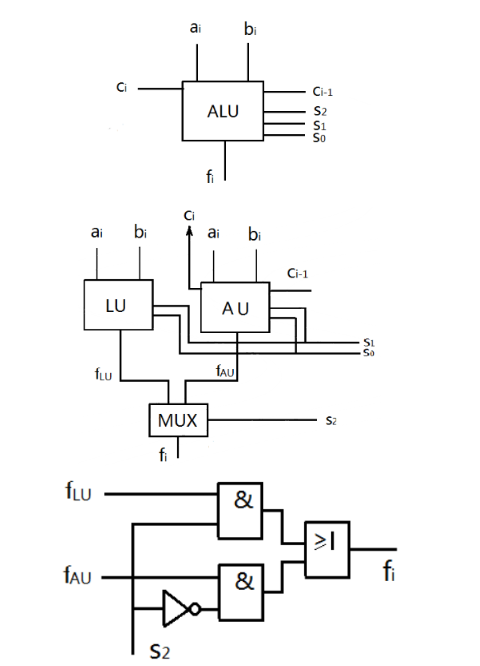

由于ALU是算术逻辑运算器,是算术,逻辑两者集成的,那么在一位的ALU中,实际上还分成了算术单元和逻辑单元,具体进行算术还是逻辑运算,由S2来起控制作用,S的最高位起到一个分流的作用。MUX是个二选一数据选择器,显示在上图最右侧,S2是决定了输出为算术运算的结果还是逻辑运算的结果。

我们从n位的ALU到一位的ALU,再到LU,AU,这是一个自顶向下的思路。从宏观到到微观。

6.接着讲解AU和LU,这两个单元。在这两个单元里,仍然是要有输入,输出数据和控制器,控制其进行哪种运算的的地址端,如果我们假定算术和逻辑运算都是四种。那么这里可以是由四选一数据选择器来构成,如下图所示,S1,S0.以及左边的四个数据均为输入,共有六个输入。分成两类,数据端和地址端。视频这里讲解的四选一数据选择器和之前理解的貌似不一样啊?

这里关于LU单元的设计,除了用数据选择器来设定外,还有一种设计方法,就是将数据端和地址端全当成输入端,F为输出端,列出真值表。

7.AU单位的设计和LU完全不一样,如果没理解错,这个是由全加器来构成的。

-

74F181 4位算术逻辑单元:高速运算的得力助手2026-04-10 131

-

一文读懂,什么是BLE?2023-11-27 4849

-

用VHDL语言创建一个8位算术逻辑单元(ALU)2023-10-24 3793

-

算术逻辑单元ALU四个要素2021-10-29 3212

-

基于可编程逻辑器件和VHDL语言实现算术逻辑单元的设计2021-01-04 2748

-

什么是算术逻辑单元?2020-06-18 16263

-

关于通过FPGA中VHDL语言实现ALU的功能设计详解2018-07-22 8007

-

一文读懂如何验证74ls181运算和逻辑功能2018-05-09 43766

-

低功耗时钟门控算术逻辑单元在不同FPGA中的时钟能量分析2015-11-19 679

-

多功能算术/逻辑运算单元(ALU) ,什么是多功能算术/逻辑2010-04-13 29806

-

什么是ALU/Brach Pediction2010-02-04 520

-

一种8位单片机中ALU的改进设计2009-08-26 3004

-

集成算术/逻辑单元举例2009-04-07 1604

全部0条评论

快来发表一下你的评论吧 !