STM32F429芯片带FIFO的DMA传输实现过程

描述

STM32系列芯片都内置DMA外设,其中很多系列的DMA配备了FIFO。这里以STM32F429芯片及开发板为例,演示一下带FIFO的DMA传输实现过程。

大致情况是这样的,我用TIMER1通道1的比较事件触发DMA,将内存数据写进UART5的数据发送寄存器DR,并将UART5的TX/RX脚物理短接,同时开启UART5的DMA接收模式,即DMA将UART5接收到的数据写到指定的接收内存区。下面重点介绍UART5的DMA方式的接收过程。

首先使用STM32CubeMx完成基本配置。

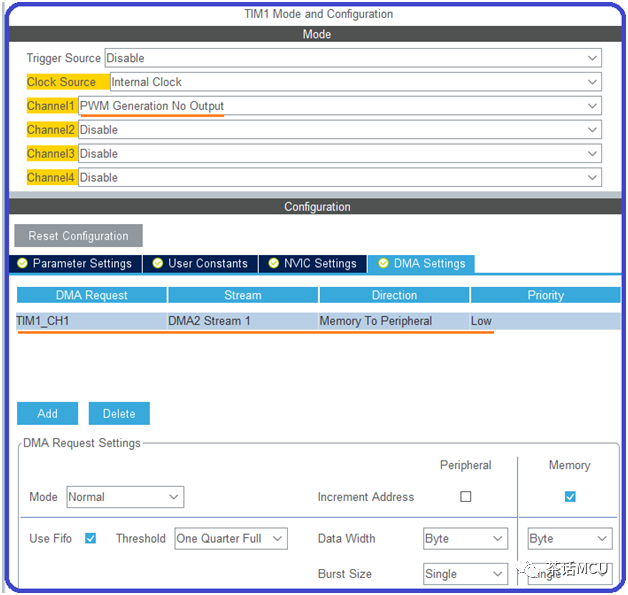

下面是关于TIM1的相关配置,使用通道1的比较事件触发DMA,将内存数据写入UART的发送数据寄存器。为什么还要搞个定时器来触发,其中一个原因是为了后面好演示结果。

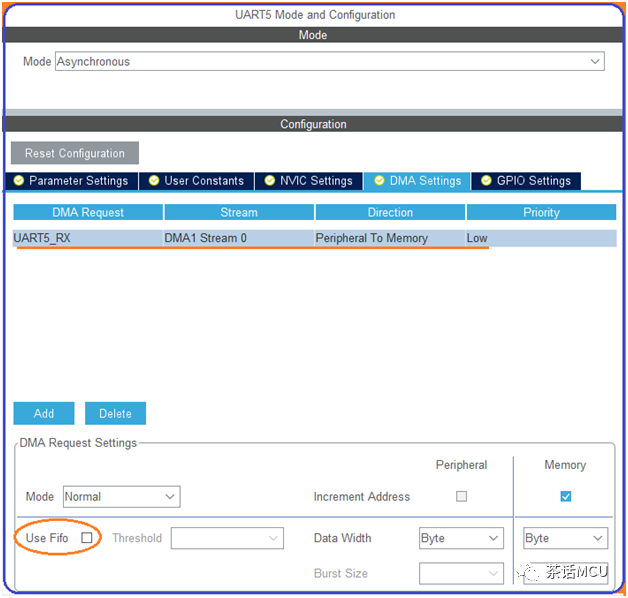

下面是关于UART5的基本配置,并开启其接收的DMA传输。此时配置还没有使用FIFO.

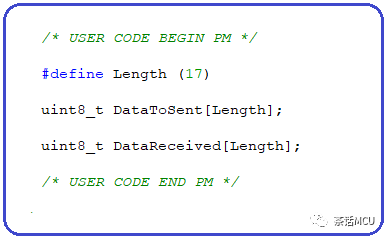

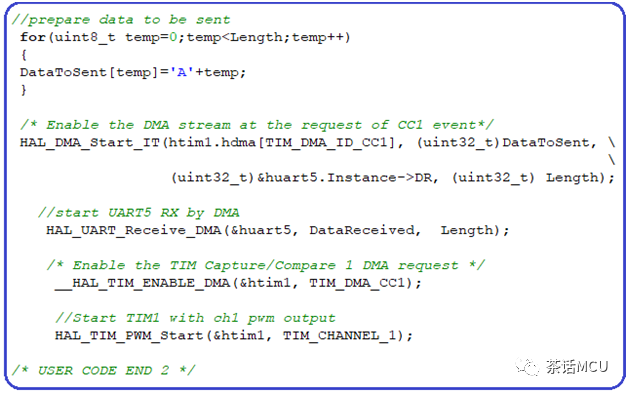

添加用户代码。代码基于STM32Cube库而准备,这里发送端发送17个字节数据出来。

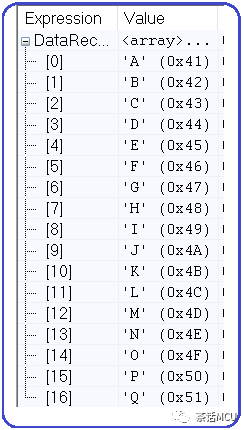

我们不妨先看看基于上面不使用FIFO的配置,即使用DMA 直接传输时的运行结果。

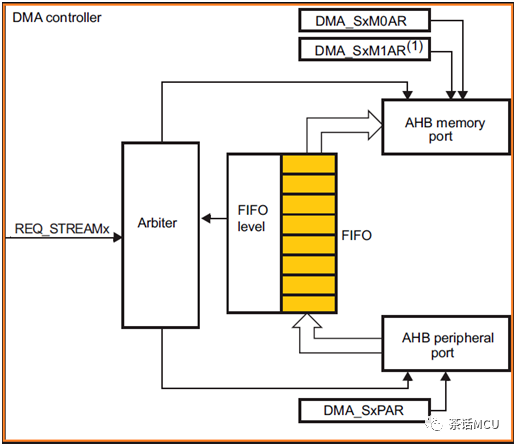

在演示基于FIFO的DMA应用结果之前,不妨简单介绍下FIFO的结构以及DMA传输过程中使用它有什么好处。

对于STM32F4来讲,每个DMA stream都有4个字的FIFO可用。它用来暂存来自DMA源端的数据,每当FIFO里存放的数据达到设定的阈值后,数据就会被移走。阈值可以设置为从1个字到4个字的深度。

启用DMA的FIFO可以最大程度地避免数据传输过程中的溢出问题,可以减少DMA对内存的访问次数从而减少总线访问竞争,通过BURST分组传输优化传输带宽以提升芯片性能。利用FIFO,通过对源端/目标端的数据进行打包或拆包以适应不同数据宽度的访问需求.让DMA的使用更为方便灵活.

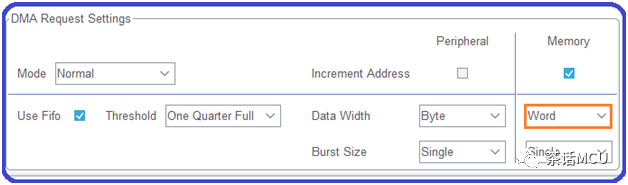

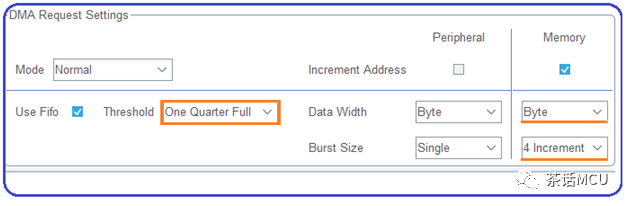

这里以UART5的数据接收为例。当启用FIFO时,目的端数据宽度可以从字节/半字/字格式自由设置。首先,当UART5的DMA接收配置成下面这样时,即DMA single模式。

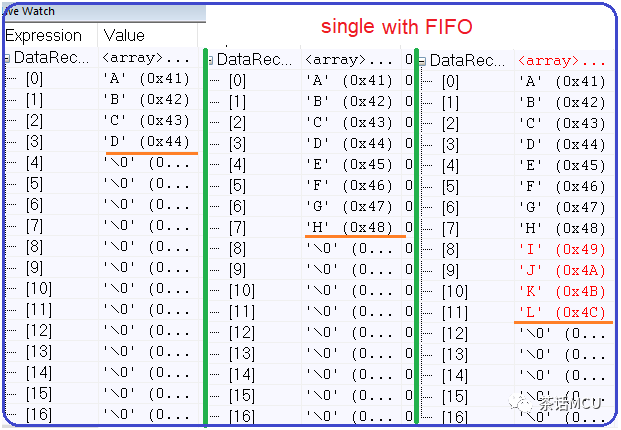

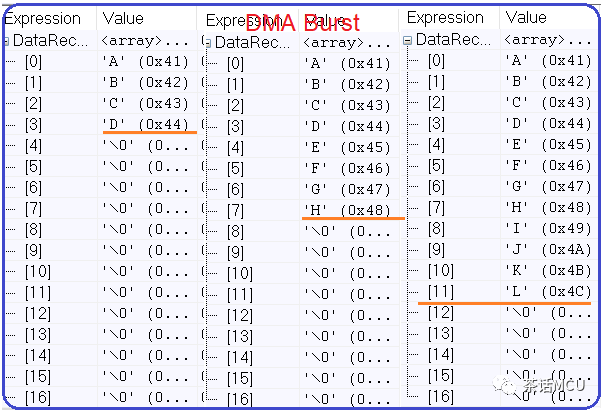

FIFO阈值设置为1/4满,即1个字的深度。运行上面代码,我们可看到来自源端的4个Byte被封装成1个word字。数据会按字方式逐一写入内存。【为看效果,我将定时器的触发放慢后做多次截图】

不过,按照上面方式将4个字节封装成一个字的传输过程中如果发生被打断的情况,此时就会遇到数据损坏的风险。因此就引入了DMA BURST传输,或称DMA节拍传输。即几个数据【4/8/16】被封装成1组,或称1个burst,或称1节。在一节内逐个进行数据传输,每个数据的传输相当于1拍。俨如音乐里的节拍,4拍1节、8拍1节之类的。对于每1节内的数据传输,DMA对总线的占用不会被总线矩阵仲裁器解除或打断,以保证每节数据的可靠完成。

我们还是以上面的应用为例,调整配置并开启BURST模式后具体看看。

我对memory端,也就是这里的目的端启用了BURST节拍传输。因为FIFO深度为1个字,每次源端数据刚好达到FIFO阈值水平时,通过1节4拍即可传输完毕,每拍对应1个byte的传输。基于BUSRT模式配置可以实现跟上面Single模式下同样的效果,而且数据传输更有保障。通过下图可以看出DMA按节进行传输,每节传输4个数据。

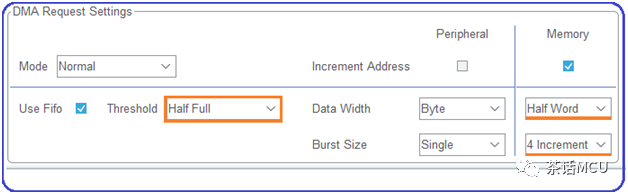

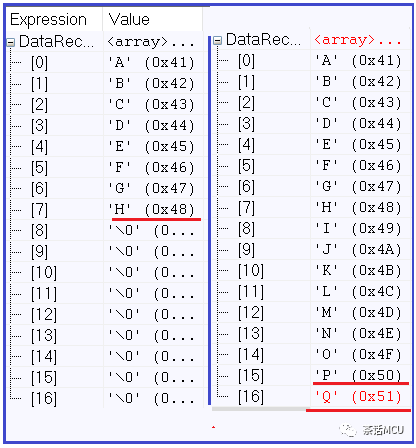

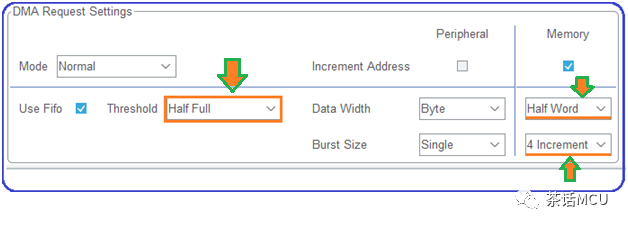

针对上述应用,我们还可以再次调整burst配置,比如下面的样子:

此时FIFO阈值为2个字,源端Memory的数据访问宽度为半字,Burst大小为4。这样的话,源端数据达到FIFO阈值时,4个半字数据组成1节分四拍传输完成,其中每拍传输半字数据。我们同样看看慢动作后的结果。

顺便提醒下,我们在做基于FIFO的burst模式的DMA传输时,BURST的大小乘以数据大小不得超过设置的FIFO阈值大小,否则会出错。比方以刚才上面的配置来看。

FIFO阈值为2个字,即8字节。数据宽度为半字,即2字节,Burst大小为4。完全合规。

-

ES0206_STM32F427/437 和 STM32F429/439 线路限制2022-11-24 652

-

STM32F429参考手册中文版2022-01-26 4868

-

STM32F429与陶晶驰串口屏数据传输(1)2022-01-12 1990

-

调试 STM32F429 + USB33002021-12-28 3471

-

【STM32F429开发板用户手册】第24章 STM32F429的USART应用之八个串口FIFO实现2021-12-27 963

-

【STM32F429开发板用户手册】第14章 STM32F429的电源,复位和时钟系统2021-12-08 1133

-

如何去正确使用STM32F429的DMA串口呢2021-12-06 1573

-

【STM32F429开发板用户手册】第19章 STM32F429的GPIO应用之按键FIFO2021-12-05 1083

-

【STM32F429开发板用户手册】第21章 STM32F429的NVIC中断分组和配置(重要)2021-12-04 1099

-

【STM32F429开发板用户手册】第13章 STM32F429启动过程详解2021-11-23 1114

-

"【STM32F429开发板用户手册】第36章 STM32F429的FMC总线应用之DMA双缓冲驱动AD7606(8通道同步采样, 16bit, 正负2021-11-22 1474

-

STM32F429的USART应用之八个串口FIFO实现2021-08-10 1144

全部0条评论

快来发表一下你的评论吧 !