XM8A51216V33A在功能上等效于异步SRAM

今日头条

描述

XRAM是一种新的内存架构,旨在以具有竞争力的价格提供高密度和高性能RAM.XRAM使用先进的DRAM技术和自刷新架构来显着提高内存密度,性能并简化用户界面。

XM8A51216V33A在功能上等效于异步SRAM,是一种高性能8Mbit CMOS存储器,组织为512K字乘16位和1024K字乘8位,支持异步SRAM存储器接口。星忆存储代理英尚微电子支持提供例程及产品应用解决方案等产品服务。

特征

•异步XRAM内存

•高速访问时间

•tAA=10/12纳秒

•低有功功率

•ICC=80 mA时为55 mA

•低CMOS待机电流

•ISB2=20 mA(典型值)

•工作电压范围:2.2 V至3.6 V

•取消选择时自动掉电

•TTL兼容的输入和输出

•提供44引脚TSOP II,48引脚TSOP I封装和48焊球FBGA封装

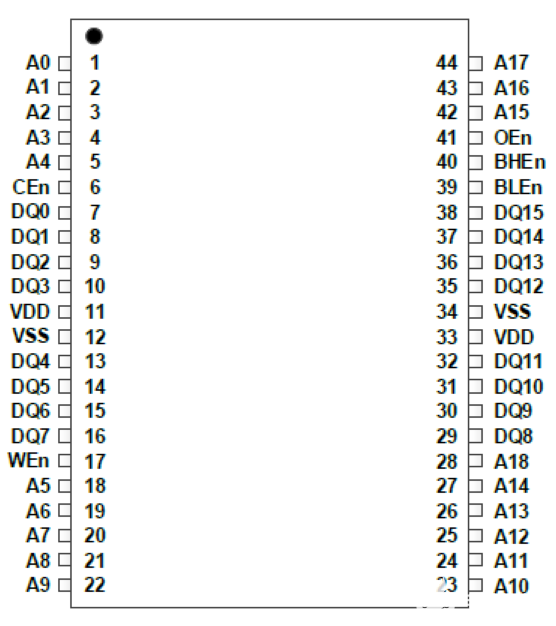

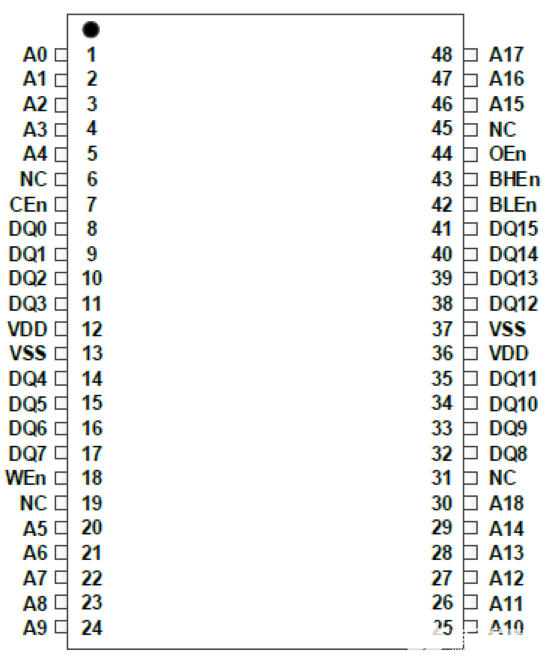

44引脚TSOP II引脚排列 48引脚TSOP I引脚排列

要写入设备,请将芯片使能(CE)和写使能(WE)输入设为低电平。如果字节低使能(BLE)为低,则来自I / O引脚(DQ0至DQ7)的数据被写入地址引脚(A0至A18)上指定的位置。如果字节高使能(BHE)为低电平,则来自I / O引脚(DQ8至DQ15)的数据将写入地址引脚(A0至A18)上指定的位置。要从器件读取,请将芯片使能(CE)和输出使能(OE)设为低电平,同时将写入使能(WE)设为高电平。如果字节低使能(BLE)为低,则地址引脚指定的存储器位置中的数据将出现在DQ0至DQ7上。如果字节高使能(BHE)为低,则来自存储器的数据出现在DQ8到DQ15上。

取消选择器件(CE),禁用输出(OE HIGH),禁用BHE和BLE(BHE,BLE HIGH)或以下操作时,输入或输出引脚(DQ0至DQ15)处于高阻抗状态写操作(CE和WE LOW)。突发模式引脚(MODE)定义突发序列的顺序。当置为高电平时,将选择交错的突发序列。当拉低时,选择线性突发序列。

国产SRAM XM8A系列型号表

| Density | PartNumber | BW bit | Vdd | Speed | Package | Status |

|---|---|---|---|---|---|---|

| 64Mb | XM8A04M16V33A | X16 | 3.3V | 10/12ns | TSOP1(48)/TSOP2(54)/BGA(48) | 2Q19 |

| 64Mb | XM8A08M08V33A | X8 | 3.3V | 10/12ns | TSOP1(48)/TSOP2(54)/BGA(48) | 2Q19 |

| 32Mb | XM8A02M16V33A | X16 | 3.3V | 10/12ns | TSOP1(48)/BGA(48) | 2Q19 |

| 32Mb | XM8A04M08V33A | X8 | 3.3V | 10/12ns | TSOP1(48)/BGA(48) | 2Q19 |

| 16Mb | XM8A01M16V33A | X16 | 3.3V | 10/12ns | TSOP1(48)/BGA(48) | MP |

| 16Mb | XM8A02M08V33A | X8 | 3.3V | 10/12ns | TSOP1(48)/TSOP2(44)/BGA(48) | MP |

| 8Mb | XM8A51216V33A | X16 | 3.3V | 10/12ns | TSOP2(44)/TSOP1(48) | MP |

| 8Mb | XM8A01M08V33A | X8 | 3.3V | 10/12ns | TSOP2(44)/TSOP1(48) | MP |

| 4Mb | XM8A25616V33A | X16 | 3.3V | 10/12ns | TSOP2(44)/BGA(48) | MP |

| 4Mb | XM8A51208V33A | X8 | 3.3V | 10/12ns | TSOP2(44)/BGA(48) | MP |

yyq

-

No Output是什么意思? Generation与Compare在功能上有什么区别?2024-04-07 589

-

KIT_A2G_TC375_LITE和KIT_A2G_TC375_ARD_SB在功能上有啥区别?2024-01-24 1007

-

XM8A51216具有哪些特点功能?2021-10-21 2276

-

为什么STM32F4开发板要搭载SRAM芯片2021-07-28 1405

-

XM8A51216芯片的特点及功能框图2021-04-02 2901

-

XM8A01M08V33A和XM8A51216V33A SRAM存储器芯片的数据手册免费下载2021-03-24 2816

-

汽车 LED 前灯在形式和功能上的演变2021-03-20 555

-

STM32F4驱动外部SRAM芯片XM8A51216介绍2021-01-08 2920

-

XM8A01M16V33A在功能上等效于异步SRAM2020-09-09 1322

-

「ALIENTEK 探索者 STM32F407 开发板资料连载」第四十一章 外部 SRAM 实验2020-06-13 2956

-

国产SRAM芯片XM8A51216随机X型存储器2020-04-30 7155

-

微雪电子IS62WV51216BLL SRAM存储模块简介2019-12-30 5815

-

哪里可找到智能门锁功能上开发的公司2014-09-01 2005

-

等效于35mm相机焦距2009-12-18 1032

全部0条评论

快来发表一下你的评论吧 !