针对码间干扰以及如何消除码间干扰的分析

电子说

描述

随着信号速率的提高,信号质量会朝两个方面恶化。一方面由于时钟周期变短,固有抖动所带来的影响变得严重,举例来说,对于1Gbps的信号,1个时钟周期为1ns,峰值为50ps的随机抖动不会给系统带来太大的影响;但是对于10Gbps的信号,1个时钟周期为100ps,50ps的随机抖动对系统的影响是致命的。另一方面,速率提升使得通道的损耗变大,码间干扰会变得更加严重。这篇文章主要针对码间干扰的产生以及如何消除码间干扰进行分析。

码间干扰,又称ISI(Inter symbolinterference),顾名思义是不同信号(码元)之间的干扰,在说码间干扰之前,我们先说一下编码。

1编码方式

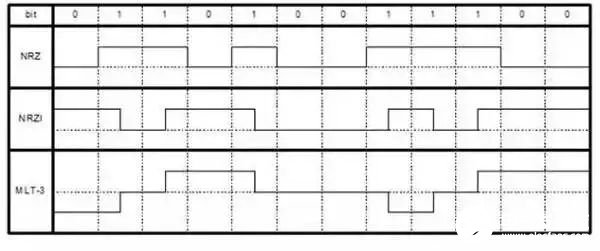

作为一名工程师,我们分析和处理信号,并不仅仅关心信号本身,而是信号中所承载的信息。对于数字信号,最终表现出来的是一连串的二进制(0/1)数据,数据和电平之间有一定的编码关系,下面列举几种常见的编码方式——NRZ、NRZI、MLT-3。

NRZ即Non-Return to Zero Code, 非归零码,是最简单常见的编码方式,用0电位和1点位分别二进制的“0”和“1”,编码后速率不变,有很明显的直流成份,NRZ编码的最高频率基波是波特率的1/2。许多协议都是用的NRZ码,例如:PCIe、SATA、SAS和USB 3.0SS。

NRZI即Non-Return to Zero Inverted,非归零反转码,编码不改变信号速率。NRZI的特点是遇到数据“0”电平保持不变,遇到数据“1”电平翻转,NRZI极性翻转并不影响数据传输。和NRZ一样,NRZI编码的最高频率基波也是波特率的1/2,USB 2.0 HS协议使用的是NRZI编码。

MLT-3即Multi-Level Transmit -3,多电平传输码,MLT-3码跟NRZI码有点类似,其特点都是逢“1”跳变,逢“0”保持不变,并且编码后不改变信号速率。和NRZ/NRZI不同,MLT-3需要4 bit才完成一次完整周期跳变(NRZ和NRZI是2 bit),相对应的最高频率基波是波特率的1/4。百兆以太网(FE)使用的就是MLT-3编码。

图1 NRZ NRZI和MLT-3编码

由于现在高速场景都是使用2电平编码(PAM4尚未普及),NRZ和NRZI码型在物理层上面的表现并没有实质性的区别,所以我们下面以NRZ码为例。

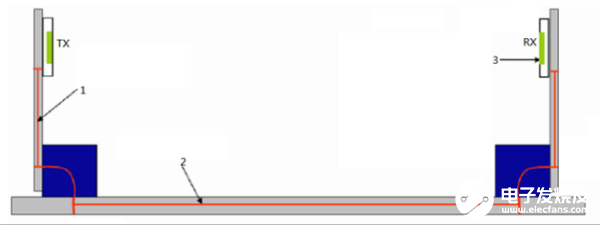

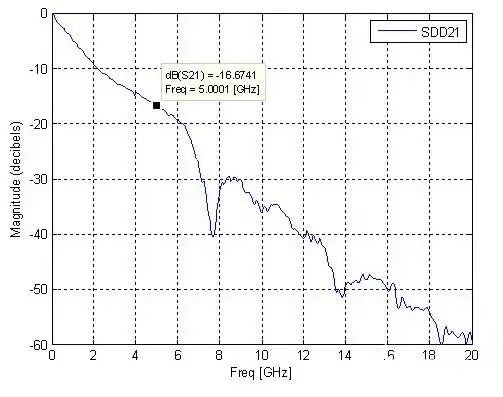

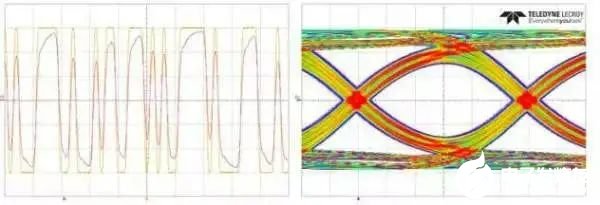

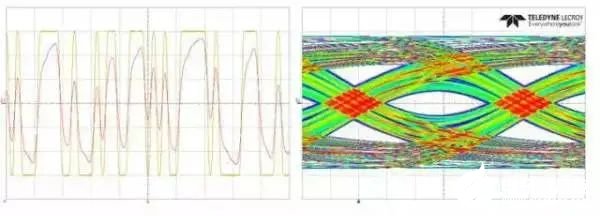

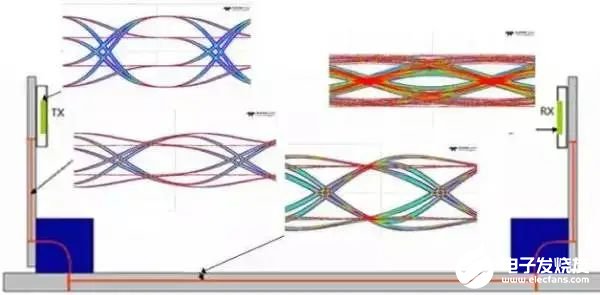

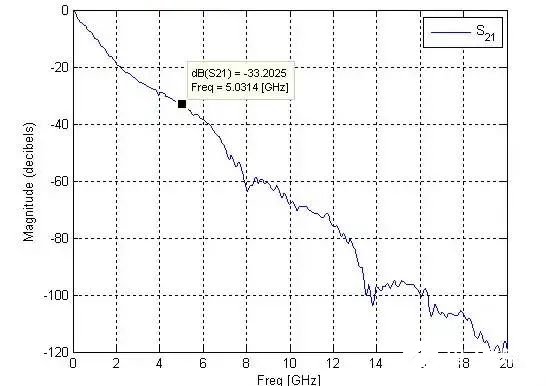

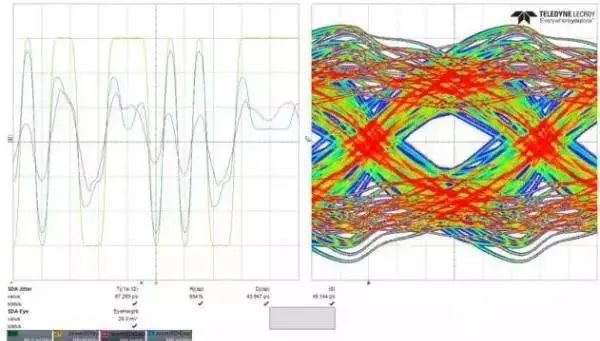

如图2所示的链路的插损[2]如图3所示(相当于20inch FR4背板的损耗),从TX发出的10Gbps理想信号经过背板后在图2中1/2/3所示位置的信号和眼图如图4、图5和图6所示,图中左侧两个信号分别为理想信号和图2中各个不同位置的信号对比,右侧为图2中各个位置的眼图。

图2 互连背板链路示意图

图3 背板插损

插损:介质损耗或InsertionLoss,简称IL,IL =-S21

可以看出,由于ISI的存在,接收端(图6)的眼图已经完全模糊,无法从信号中判断电平的’0’和’1’,如果不经过处理的话,数据从发送端传送到接收端会出现大量的误码。

图4 近端(位置1处)信号和眼图

图5 位置2处信号和眼图

图6 接收端(位置3处)信号和眼图

在插损很大时,在低频信号和高频信号交界的地方,最容易产生ISI。如图6中红圈部位所示,在一串如’11111101’这样的信号,先出现长串的’1’,然后接着是’01’信号,在长’1’信号向’01’信号切换的时候,由于放电时间不足,使得’0’电平严重偏离垂直参考点。所以ISI一般有两个必备条件:1)插损很大;2)低频信号和高频信号切换。消除ISI也需要从这两个方面来考虑。

减小插损一般来说有两种办法:一种是减小走线长度,另一种是使用更好板材的PCB以及更好的连接器,然而减小走线长度的话可能会影响布线,而使用更好的板材和连接器会大大增加系统的成本,所以这种方法本文中不再详述。

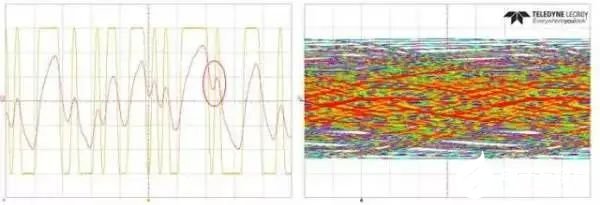

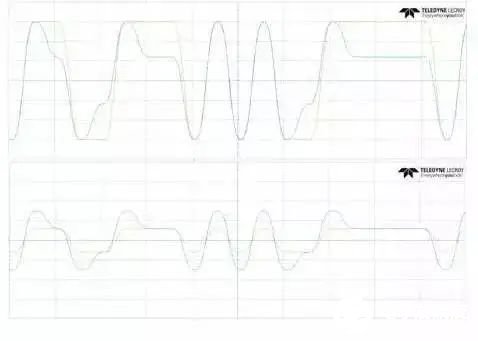

28B/10B编码

由于数据是随机的,当反复发送”010101”之类的电平时是信号中能够出现的最高基波频率成分,恒定为波特率的一半,但是由于在实际信号中出现连续的’1’或者连续的’0’信号的个数是不确定的,出现连续’0’或者’1’的个数越多,对信号质量的影响越大。图7为两种不同码型信号经过同一链路的仿真结果,上边是PRBS7,下边是PRBS9[3],可以明显看出PRBS9的TJ和ISI比PRBS7大。

限制信号中最长的连续’0’和’1’的个数可以改善ISI,8B/10B编码就是其中最常用的一种编码方式,8B/10B编码将8位数据分解成两组,一组3位、一组5位,经过编码之后变成一组4位和一组6位的10位数据,经过编码后的数据中连续’0’和’1’的个数不超过5个,另外,经过8B/10B编码后的数据’0’和’1’数量基本保持相等,使得信号的DC平衡。USB3.0、PCIe1.0、PCIe2.0和SATA等协议都使用8B/10B编码。类似的还有64B/66B、128B/130B编码等,同时在使用NRZI的USB 2.0中,为了限制连续高或者连续低电平的长度,规定在数据中连续出现6个’1’之后自动插入1个’0’,这也是这个目的。但是8B/10B编码会影响信号的有效带宽,每10比特信号中只传递8比特有效信号,先当于20%的带宽是浪费的。从PCIe2.0到PCIe3.0的演进中,就放弃了8B/10B编码,线速率从5Gbps到8Gbps但是实际的带宽却翻了一倍

图7 PRBS7和PRBS9的ISI

PRBS:伪随机码,PRBS后面的数字越大,出现的连续的’0’和’1’信号的个数就越长

3加重和均衡

均衡可以分为发送端均衡和接收端均衡,发送端均衡称为加重或者FFE,接收端的均衡有CTLE和DFE两种。

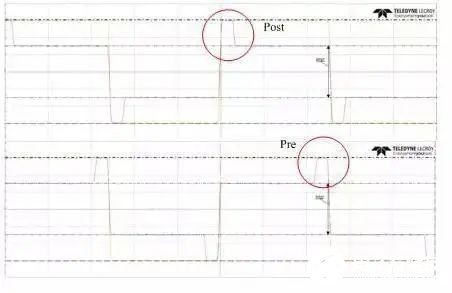

FFE:FFE是Feed forward equalizers的缩写,它可以分为预加重(Pre-Emphasis)和去加重(De-Emphasis)的方法类似,都是通过在TX改变高、低频成分(如图8所示),区别是预加重是增加高频成分,去加重是减少低频成分,经过TX端的均衡后能够改善信号质量,现在一般都使用去加重的方式,常用的有2种——Pre cursor和Post cursor,Pre和Post如图9所示。一般情况下Post cursor使用较多,在链路较恶劣的时候加一些Pre cursor可以使眼图的“眼皮”变薄。De-Emphasis的大小是由高频部分和低频部分的比值决定的,高频部分电压和低频部分电压的比值越大,对抗链路差损的能力也就越强。下图的Pre cursor和Post cursor都是6dB,也就是高频电压是低频的两倍。FFE的优点是不会放大信号的噪声,另外,在恶劣的链路环境下,如果光依靠RX的均衡无法使得眼图睁开,在这种情况下我们推荐使用FFE。

图8 De-Emphasis上和Pre-Emphasis下

图9 Post cursor和Pre cursor

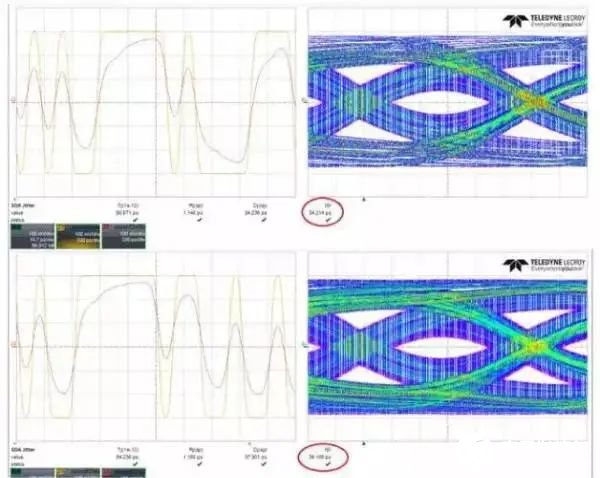

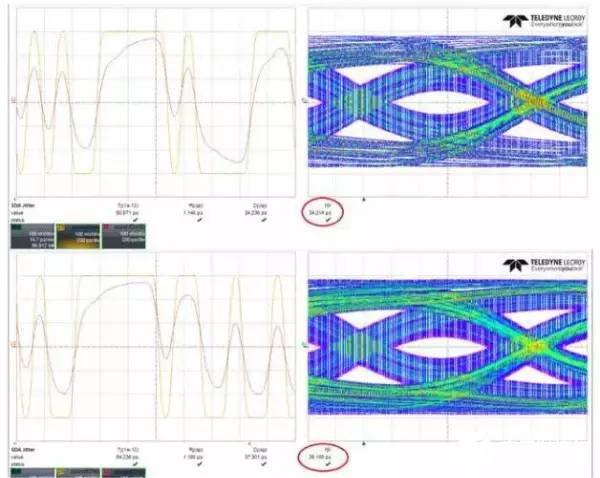

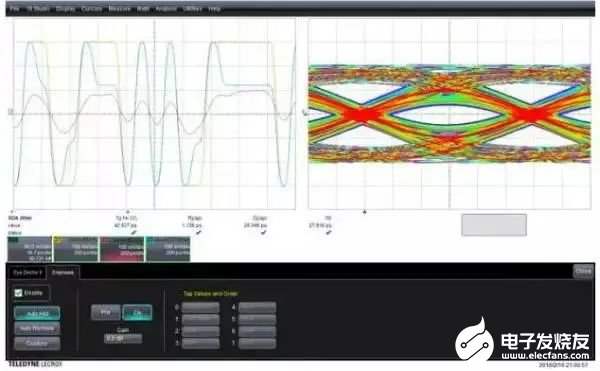

图10是链路中接收端经过加重后的眼图,经过8dB的Post cursor去加重后,眼图已经睁开。

图10 链路中接收端经过加重后的眼图

图11是加上8dB 去加重后链路中各个位置的眼图。从图11可以看出,在链路中芯片发送端以及位置1/2处的眼图都有严重的overshoot,这就是FFE的不足之处,由于在发送端增加了高频成分,在多Lane系统中会增加串扰,并且可能会导致EMC超标,在现在的高速系统中,会将较多的均衡的权重分配在接收端。

图11 经过加重后链路中各个位置的眼图

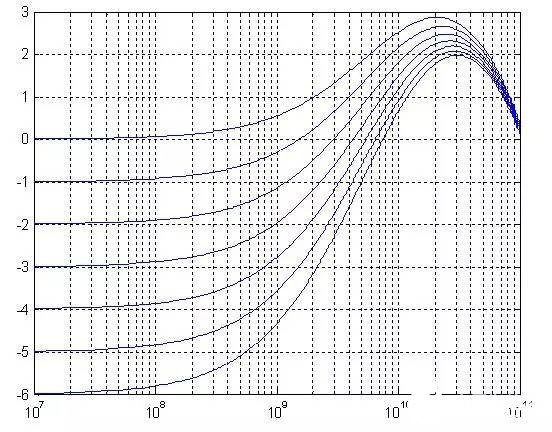

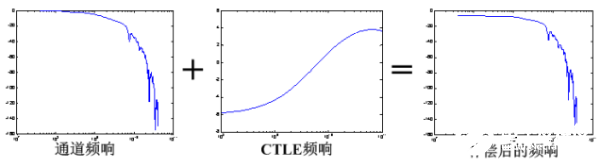

CTLE:CTLE是Continuous-time linearequalizer的缩写,它是有如图12频响曲线的放大电路,它们会对高频信号进行放大,对低频信号进行衰减,以补偿通道的插损。对待不同的链路,我们可以调节CTLE电路的参数(如增益、boost、零点、peak点等)获得恰当的频响曲线来进行补偿(如图13所示)。通常来说,CTLE电路各参数相互配合组成的组合越多,芯片应对不同场景链路的能力也就会越强,这种芯片通常还会集成CTLE的自适应算法,根据链路自动调节CTLE的参数以获得最优的参数。

图12 CTLE频响曲线示意图

图13 经过CTLE补偿的链路频响

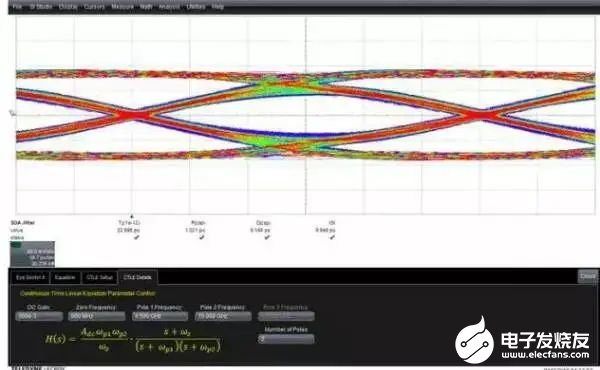

图14是图13中信号经过CTLE均衡后得到的眼图。可以看出,CTLE补偿的效果和去加重相比要好一些。

图14 经过CTLE均衡后的眼图

但是在链路很长(链路插损很大)时,CTLE为了补偿链路的插损,通常会将高频进行放大,这样一方面会将高频噪声放大,降低系统的信噪比;另一方面,CTLE的温度特性相对较差,高温下的增益比低温小,所以在温度变化时不利于系统的稳定,在这个时候我们需要DFE的帮助。

DFE:DFE是Decisionfeedback equalizer的缩写,电路中DFE一般在CTLE之后。DFE的实现方式和FFE类似。DFE可以辅助CTLE改善信号质量,另外DFE可以实时地根据眼图的情况进行自适应调节,它可以用来补偿由于温度或者其他条件变化带来的链路和芯片(如CTLE)的变化,增加系统的稳定性。

图15 经过CTLE和DFE均衡后的眼图

在实际的使用过程中,需要FFE、CTLE和DFE三者相互配合使用,尤其是在链路条件相对复杂的情况下。下面是一个比较恶劣的线路,在5GHz处,链路的插损达到了约33dB(相当于40inch FR4 背板的损耗)。这个时候单纯靠FFE或者CTLE、DFE已经无法实现将眼图张开,这时候需要使用FFE+CTLE+DFE相互配合,使得在接收端的采样点处眼图能够完全张开,确保达到目标误码率。

图16 更恶劣的背板差损

-

#硬声创作季 #通信 通信原理-3.5.1 码间干扰与Nyquist准则水管工 2022-11-04

-

无线通信原理:码间干扰与Nyquist准则#无线通信jf_49750429 2022-11-08

-

STM32的ADC通道间干扰的问题2017-12-24 8770

-

如何消除STM32的ADC通道间干扰?2022-01-27 1155

-

OFDM在高速移动下的载波间干扰消除2009-02-28 626

-

3G系统间的共存干扰研究2010-09-15 899

-

COMPASS和Galileo系统间信号干扰研究2013-01-08 1365

-

WCDMA和HSDPA的单系统的系统的容量以及系统间干扰进行仿真分析2017-12-13 1644

-

基于中继间干扰消除的安全传输方案2018-01-14 1096

-

如何消除码间串扰_怎么避免码间串扰2018-04-16 47422

-

解决多用户链路数据传输的并行干扰消除算法的研究分析2020-01-16 5096

-

无码间串扰的传输特性及有哪些消除方法2020-03-04 17863

-

如何在高速信号中降低符号间干扰2023-11-27 1622

全部0条评论

快来发表一下你的评论吧 !