利用可编程逻辑器件实现多路采集与切换系统的应用方案

可编程逻辑

描述

作者:王威,张秋云,江虹,余恒松,易志强,朱笛

引言

随着信息网络与分布式采集技术的飞速发展,在智能交通、工业测控等领域,对网络数据传输处理速度、可靠性及实时性的要求越来越高。同时,现场可编程门阵列(FPGA)凭借日益丰富的片内资源、运行速度快和并行处理等特点,使其成为高速采集传输系统设计的一个有效手段。以太网标准TCP/IP协议是Internet互联网络的基础,其不依赖固定的硬件或软件系统,可以集成于不同的网络环境中,具有通信可靠、使用普遍、易于适配接口等优点。但传统的基于CPU软件实现的TCP/IP协议处理方式,占用大量的CPU资源,消耗存储空间,无论在处理速度还是稳定性方面,都无法与基于硬件实现的相比。韩国WIZnet公司推出的以太网控制芯片W5500支持硬件TCP卸载引擎(TCP Offload Engine,TOE),其集成了TCP/IP全硬件协议栈,能够大幅提高应用设备的网络性能,降低CPU占用率,减少FPGA逻辑资源使用,缩短响应时间。

针对上述研究现状和分布式采集场景分析,本文介绍了一种基于FPGA和TOE架构,实现TCP/IP协议数据传输的多路采集与切换系统。该系统涉及并行数据采集、多路通道切换、TCP/IP协议通信等模块,并通过上位机PC(或键盘与LCD)进行远程(或本地)准确控制与实时显示,满足多路通道切换、模拟信号并行采集、可靠性传输等功能的需求。

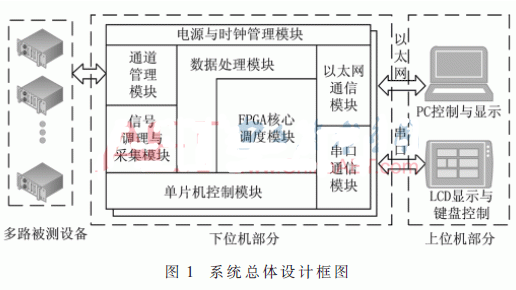

1 系统总体设计

该系统包含上、下位机设计,组成一个完整的多路采集与切换系统,系统总体设计框图如图1所示。上位机部分中的PC控制与显示子系统,可根据监测需求,远程对下位机进行配置和部署,并实时显示获取的数据。LCD显示与键盘控制子系统,与下位机安装为一体,可独立地对下位机进行通道控制与信号检测,提升该系统的便捷性和实用性。下位机作为该系统的主体部分,主要由基于FPGA芯片的核心调度、数据处理、通道管理、信号调理与采集、网络通信、串口通信、单片机控制及电源与时钟管理七大模块组成。FPGA核心调度模块是下位机的核心部分,完成对下位机各个模块间的协调运行与逻辑控制,实现全局时钟管理、TCP/IP协议与串口通信、命令和数据的组帧与解析、通道切换与配置、信号采集与数据处理等功能。

基本工作原理:系统上电后,首先等待FPGA初始化,完成默认配置,被测外围接口保持关闭,下位机处于TCP服务器模式,等待上位机连接。上位机PC连接成功后,进行通道切换与选择命令配置,并通过以太网将命令数据传至下位机。然后,下位机通过以太网通信模块接收TCP数据,解析数据获取命令后,逐一对各通道管理模块进行配置,切换到被测通道,并对其中8路通道的电压和电流进行信号调理与采集。每次采集的数据和状态信息,再通过数据处理模块组帧后,交付给以太网通信模块以TCP/IP协议发送数据至上位机。最后,上位机对接收数据进行分析和显示,完成对多路通道的远程切换、采集与监测。

若无PC连接,系统可使用键盘进行命令配置,LCD显示部分测试结果,采用串口通信与下位机进行命令和数据的交互,实现本地便捷控制与监测。

2 系统硬件及FPGA设计

多路采集与切换系统的硬件设计主要由电源与时钟模块、FPGA逻辑控制模块、以太网通信模块、通道管理与切换模块、ADC信号采集模块和STM32控制模块组成,硬件设计结构框图如图2所示。

2.1 FPGA逻辑控制模块

FPGA逻辑控制模块采用了基于Xilinx公司Spartan-6系列的XC6SLX150-2FG484C开发的核心板AC6150具有高速、高带宽、高容量等特点。这款核心板尺寸为60 mm×60 mm,搭载FPGA上电配置功能,扩展用户I/O接口168个,并具备丰富的内部逻辑资源。其作为载板直插使用,为工程技术人员提供了一个简便的FPGA使用方案,极大降低了设计复杂度与周期。

FPGA是下位机部分的核心控制单元,逻辑设计采用硬件描述语言(Verilog HDL)和集成开发套件ISE14.7实现。FPGA逻辑控制模块的顶层设计包括时钟管理与系统复位、W5500控制、数据处理、通道切换、AD采集控制以及STM32控制等子模块,顶层模块负责各个子模块的连接和逻辑综合,FPGA顶层设计结构如图2中间虚线框中所示。

2.2 以太网TCP/IP通信模块

以太网TCP/IP通信模块主要采用WIZnet公司的一款多功能全硬件以太网接口芯片W5500,内部集成10/100 M以太网控制器,嵌入TOE技术,支持TCP、UDP、IPv4等协议,无需考虑协议内部各层关系,不涉及操作系统,只需要正确配置就可以实现网络连接,接口电路简单、编程灵活方便。该模块电路如图3所示。

FPGA基于SPI(外部串行接口)协议对W5500内部的寄存器区和内存进行读写访问。寄存器区由通用寄存器区(用于配置网关、子网掩码、源IP和源MAC地址等)和8个Socket_n(0≤n≤7)寄存器区(用于配置Socket端口号、模式、配置命令等)组成。W5500内嵌32 KB缓存(接收内存和发送内存,各占16 KB),用于缓存以太网传输中已接收和待发送的用户数据。

采用FPGA+W5500的方式实现基于TCP/IP协议的硬件通信系统设计,具有状态稳定、体积小、成本低、高速可靠等优势。FPGA通过W5500控制子模块实现W5500的状态机控制和SPI协议通信,实现对W5500芯片的控制和数据交互。W5500的状态机控制包括对W5500控制器的状态初始化、寄存器配置、TCP连接管理、内存数据读写等功能,其主控制状态机状态转移如图4所示。

FPGA逻辑设计中,将W5500配置为TCP服务器模式,等待上位机PC(作为客户端)进行主动连接。建立连接后,PC下发通道切换、采集等命令数据,通过以太网传输至W5500。FPGA检测到W5500接收中断后,从W5500接收缓存中读取数据,然后交给数据处理模块,进行数据解析,并将命令信息下发到相关控制模块。

数据处理模块主要完成对接收(和待发送)的TCP数据进行解析(和组帧);W5500控制模块的核心在于TCP的连接建立、数据接收和数据发送控制。使用Socket_0作为与上位机通信的端口,TCP通信建立、数据收发流程如图5所示。经回环测试,TCP传输最高速率达40 Mb/s,满足众多嵌入式应用需求。

2.3 通道管理与切换模块

通道管理与切换模块采用通道选通芯片(ADG1408YRUZ)、电平转换芯片(LSF0108DCUR)、控制切换芯片(ADG819BRM)和继电器(G3FD-X03SN)组成,以实现对外围不同接口管脚的选通、驱动和控制。通道选通芯片实现8通道选一的选通功能;控制切换芯片和继电器控制外围输入通道是否接入;FPGA管脚输出电平为3.3 V,难以直接驱动外围器件,通过电平转换芯片将输出转换为5 V,以提高驱动能力。

当数据解析模块收到通道切换命令后,FPGA通过通道切换子模块,实现对外围芯片的控制,完成多路不同通道的管理和切换。

2.4 ADC信号采集模块

ADC信号采集模块由电压采集和信号调理子模块组成。电压采集子模块选用ADI公司的高精度模数转换芯片AD7609BSTZ,它是一款18位、8通道、真差分、同步采样模数数据采集系统(DAS) ,最高吞吐率达200 kS/s。该系统采用2片AD7609芯片分别对8路被测通道的电压和电流进行采集,模拟信号输入范围采用±5 V。在采集前端,连接信号调理子模块,选用电流转电压芯片(MAX4080SASA+)将被测电流信号转换为模拟电压信号,再经过电压信号调理芯片(AD8276ARZ)和适当高精度电阻进行分压,使输入AD芯片的被测模拟信号范围在-5 V~+5 V之间。

FPGA完成对通道的管理切换后,通过AD采集控制子模块,开启对接入被测的8路通道AD采集。采样频率为10 kHz,16路并行采集,采样速度达2.88 Mb/s(16×18 bit×10 kHz/s)。AD采集控制子模块采用串行工作方式,每完成一次采集,将数据交由数据处理子模块进行组帧,再通过W5500将数据以TCP/IP协议传输至上位机PC。

3 系统软硬件综合测试

3.1 FPGA逻辑设计仿真与测试

进行FPGA逻辑设计时,仿真分析是必不可少的环节,利用ISE14.7自带的仿真软件ISim和在线逻辑分析软件ChipScope,有利于验证设计的正确性,提高设计效率。由于篇幅有限,以下针对该系统FPGA设计的重难点模块之一——以太网TCP/IP通信模块的W5500数据发送功能,进行仿真和测试分析。

以太网TCP/IP通信通过控制W5500实现,对W5500控制模块进行数据发送测试仿真如图6所示。在接收到命名标志Cmd_Receive后,将测试数据Test_Data_r[7:0]依次存入B_FIFO中,再以单bit的方式从B_FIFO中读出,结合SPI协议将数据发送至W5500发送缓存;数据全部写入后,给出写入完成标志W5500WrFlag,以此开启W5500进行TCP数据发送。使用ChipScope对实测信号在线“抓取”,得到W5500数据发送测试信号截图如图7所示,实测与仿真结果一致,表明该设计的正确性。

3.2 系统测试与效果

下位机采用标准2U机箱设计,可同时连接8台被测设备,每台设备有13路不同的接口,共需控制8组×13路通道的切换。上位机的命令配置界面如图8所示,通过勾选通道组合,实现多通道选择和切换命令的配置。图8中展示了同时开启对8台被测设备的2通道监测,并施加控制信号1、4的命令配置过程。

使用网络封包分析软件WireShark对系统的TCP/IP传输过程进行测试,下位机为服务器(IP:192.168.1.168,端口号:10000),上位机PC为客户端(IP:192.168.1.1,端口号:8001),TCP/IP通信测试的流量统计结果如图9所示。图中给出“三次握手”建立TCP连接,和命令数据发送接收与ACK回复过程,表明TCP/IP通信正常。

在2号通道接入被测器件,上位机采用图8中的通道切换命令配置,系统测试对应的PC和LCD监测显示结果如图10所示,PC在报表界面可实时显示被测8路通道的电压和电流,LCD以10 Hz的频率刷新显示监测结果。经长期试验和测试结果表明,PC与LCD显示结果与实际一致,测试效果良好,显示画面稳定,操作便捷流畅。

4 结论

本文设计了一种基于FPGA和TCP/IP协议的多路采集与切换系统,其采用FPGA+W5500的方式实现了基于硬件的TCP/IP协议栈,并详细介绍了该系统的TCP/IP通信、通道切换和多路采集部分的设计方法。综合测试结果表明,系统可以实现多路采集与切换控制的功能,稳定可靠、使用便捷,具有一定的实用价值。

责任编辑:gt

-

可编程逻辑器件2014-04-15 3680

-

可编程逻辑器件发展历史2019-02-26 4623

-

求一种可利用复杂可编程逻辑器件设计技术实现的专用键盘接口芯片方案2021-04-15 1092

-

可编程逻辑器件是如何发展的?2021-04-29 1876

-

PLD可编程逻辑器件2021-07-22 2327

-

可编程逻辑器件设计2006-03-25 1186

-

可编程逻辑器件基础及应用实验指导书2010-03-24 788

-

什么是PLD(可编程逻辑器件)2009-06-20 30063

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1168

-

可编程逻辑器件(书皮)2022-07-10 798

-

采用复杂可编程逻辑器件实现多路信号采集系统的设计2020-03-03 2102

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 2265

-

可编程逻辑器件的结构2023-03-24 2156

-

可编程逻辑器件测试2023-06-06 1318

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4592

全部0条评论

快来发表一下你的评论吧 !