自己动手做一个16位CPU该如何操作

电子说

描述

如果想要制作一个CPU,首先得明白下计算机的组成结构(或者计算机的替代品,因为并不是只有计算机有CPU,现在的电子产品都很先进,很多设备例如手机、洗衣机甚至电 视和你家的汽车上面都得装一个CPU),数字电路基础,还最好有点编程的基础(当然,没有也没关系,这些知识都很容易获得,各种书上面都会提到,并且在接下来的过程中我会提到这些知识)

我们要实现的是一个RISC指令集的CPU,并且我们最后要自己为这个CPU设计指令并且编码。

首先我们来听个故事,关于CPU的诞生的故事:

日本客户希望英特尔帮助他们设计和生产八种专用集成电路芯片,用于实现桌面计算器。英特尔的工程师发现这样做有两个很大的问题。第一,英特尔已经在全力开发 三种内存芯片了,没有人力再设计八种新的芯片。第二,用八种芯片实现计算器,将大大超出预算成本。英特尔的一个名叫特德?霍夫(Ted Hoff)的工程师仔细分析了日本同行的设计,他发现了一个现象。这八块芯片各实现一种特定的功能。当用户使用计算器时,这些功能并不是同时都需要的。比 如,如果用户需要计算100个数的和,他会重复地输入一个数,再做一次加法,一共做100次,最后再打印出来。负责输入、加法和打印的电路并不同时工作。这样,当一块芯片在工作时,其他芯片可能是空闲的。

霍夫有了一个想法:为什么不能用一块通用的芯片加上程序来实现几块芯片的功能呢?当需要某种功能时,只需要把实现该功能的一段程序代码(称为子程序)加载到通用芯片上,其功能与专用芯片会完全一样。

经过几天的思考后,霍夫画出了计算器的新的体系结构图,其中包含4块芯片:一块通用处理器芯片,实现所有的计算和控制功能;一块可读写内存(RAM)芯片, 用来存放数据;一块只读内存(ROM)芯片,用来存放程序;一块输入输出芯片,实现键入数据和操作命令、打印结果等等功能。

看完这个故事后,可以总结:CPU是一种用来代替专用集成电路的器件(这只是我的理解,不同人有不同理解,这个就智者见智了,我在接下来的例子中也会说明我的想法)。

然后考虑如下这个例子:

例1-1:

mov eax,0

repeat:inc eax

jmp repeat

例1-2:

int main()

{

unsigned int i = 0;

while(1)

i++;

}

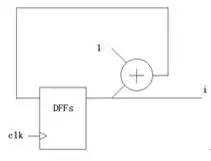

例1-3:

可以看到,以上三个例子都产生了一个从0不断增加的序列,而且前两个例子会一直加到溢出又从0开始(这个取决于计算机的字长也就是多少位的CPU,eax是 32位寄存器所以必然是加到4294967295然后回0,而后面那个c程序则看不同编译器和不同平台不一样),后面那个例子则看你用的是什么样的加法器和多少个D触发器

那问题就来了,我假设要一个递减的序列怎么办呢?前两个例子很好解释,我直接改代码不就得了:

例2-1:

mov eax,0

repeat:dec eax

jmp repeat

例2-2:

int main()

{

unsigned int i = 0;

while(1)

i--;

}

你只需要轻轻敲击键盘,修改了代码之后,它就会如你所愿的执行。

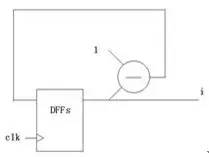

但是后面那个例子怎么办呢?可能你已经想到办法了:如例2-3所示。

例2-3:

问题就来了,你在键盘上敲两下可不能改变实际电路!上面(例1-3)中是个加法器,但是跑到这里却变成了减法器(例2-3)!

这样的话,你就得再做一个电路,一个用来算加法,一个用来算减法,可是两个电路代表你得用更多的电路和芯片,你花的钱就得更多,要是你不能同时使用这两个电路你就花了两份钱却只干了一件事!

这个问题能被解决吗?答案是能!

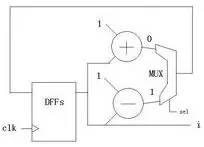

请看例3:

这个例子中使用了一个加法器一个减法器,没比上面的电路省(显然。。。。难道你想用减法器做加法器的功能?不可能吧!当然,加上一个负数的补码确实就是减去 一个数,但是这里先不考虑这种问题),多了一组多路器,少了一组D触发器。总的来说,优势还是明显的(两块电路板和一块电路板的差别)。

而sel信号就是用来选择的(0是递增,1是递减)。

如果我们把sel信号看做“程序”的话,这个电路就像一个“CPU”能根据“程序”执行不同的“操作”,这样的话,通过“程序”(sel信号),这个电路就能够实现复用。

根据上面的结论,我认为(仅仅是个人认为啊~):程序就是硬件电路的延伸!

而CPU的基本思想,我认为就是这样的。

接下来我们就分析CPU的结构和各个部件,然后实现这个CPU。

什么是单周期CPU,什么是多周期CPU,什么是RISC,什么是CISC

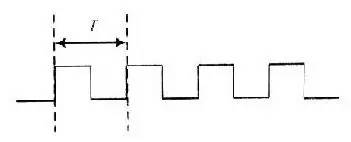

首先大家得有时钟的概念:这个问题不好解释 啊。。。。。。可以理解为家里面的机械钟,上上电池之后就会滴答滴答走,而它“滴答滴答”的速度就是频率,滴答一下用的时间就是周期,而人的工作,下班, 吃饭和学习娱乐都是按照时钟的指示来进行的(熬夜的网瘾少年不算),一般来说,时钟信号都是由晶体振荡器产生的,0101交替的信号(低电平和高电平)。

数字电路都需要一个“时钟”来驱动,就像演奏交响乐的时候需要一个指挥家在前面指挥一样,所有的人都会跟着指挥的拍子来演奏,就像数字电路中所有的部件都会跟着时钟节拍工作一样。

如下是一个理想的时钟信号:(注意是理想的)。

当然,实际的时钟信号可能远没有这么理想,可能上升沿是斜的,而且占空比也可能不是50%,有抖动,有偏移(相对于两个器件),可能因为导线的寄生电容效应变得走形。

上面那段如果没听懂也没关系~~~反正就是告诉你,实际的时钟信号测出来肯定没这么标准。

而 cpu的工作频率,是外频与倍频的积(cpu究竟怎么算频率,其实这个我也不太清楚呵呵),因为cpu是通过外部的晶振产生一个时钟信号,然后再通过内部 的电路(锁相环),倍频至需要的频率。当然,有人问,为什么要这么麻烦呢?直接在电路外边做个时钟晶振能产生那么高的时钟信号就可以了嘛,这个是可以的, 在某些简单的系统上(例如51单片姬)就是这样的,但是计算姬的cpu比较复杂,因为一些原因所以必须要做到cpu内。

下面简单说一下CPU的两种指令集:CISC和RISC。

说下我的看法(个人看法,如有错误还请高手指正):

RISC是Reduced Instruction Set Computer,精简指令集计算机,典型例子是MIPS处理器。

CISC 是Complex Instruction Set Compute,复杂指令集计算机,典型例子是x86系列处理器(当然现在的x86指令还是当初cisc的指令,但是实际处理器的结构都已经变成了 risc结构了,risc的结构实现流水线等特性比较容易,在计算机前的你如果用的是intel某系列的处理器,则它使用的指令集看上去还是像cisc的 指令,但是实际上你的cpu的结构已经是risc的了)。

一般CISC的处理器需要用微指令配合运行,而RISC全部是通过硬连线实现的, 也就是说,当cisc的处理器在执行你的程序前,还得先从另外一个rom里面读出一些数据来“指导”处理器怎么处理你的命令,所以cisc效率比较低,而 risc是完全通过部件和部件之间的连接实现某种功能,极大的提高了工作效率,而且为流水线结构的出现提供了基础。cisc的寄存器数量较少,指令能够实 现一些比较特殊的功能,例如8086的一些寄存器:

ax,bx,cx,dx,si,di等;段寄存器有:cs,ds,es,ss等。相对的指令功能比较特殊,例如xlat将bx中的值作为基地址,al中的值作为偏移,在内存中寻址到的数据送到al当中(以ds为段寄存器)

而risc的处理器则通用寄存器比较多,而指令的功能可以稍微弱一点,例如:

以nios嵌入式处理器来说明,nios处理器有32个通用寄存器(r0~r31),而指令功能相对x86的弱一些,而且x86进行内存访问是直接使用mov指令,nios处理器读内存用的是load,写内存用的是store,

二者响应中断的方式也不一样,举一个典型的例子,x86的处理器将中断向量表放在了内存的最低地址(0-1023,每个中断向量占四个字节),能容纳256 个中断(以实模式的8086举例)响应中断时,将中断号对应的地址上的cs和ip的值装入到cs和ip寄存器而将原来的地址保存,并且保存状态寄存器然后 进入中断处理,而risc则拥有一个共同的中断响应函数,这个函数会根据中断号找到程序向系统注册的函数的地址,并且调用这个函数。一般来说而是用的 cisc指令的长度是不定的,例如x86的xor ax,bx对应机器码是0x31d8、而push ax是0x50、pop cx是0x59。而risc的指令确是定长的,例如32位。

如果还有不清楚的。。。。。自行百度,要理解这些概念需要一点时间

一个CPU的基本结构以及必要组件

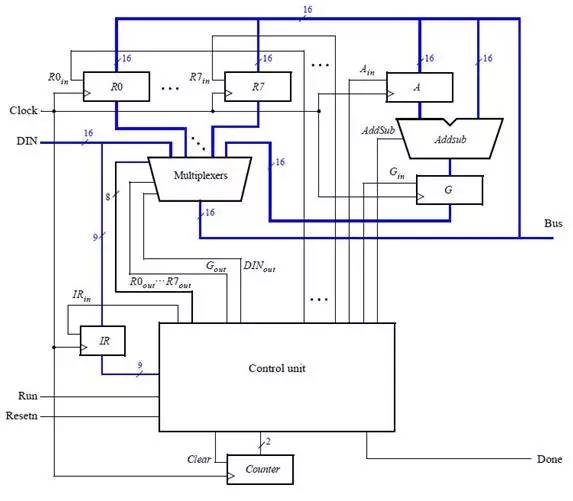

这个例子引用自DE2开发板套件带的光盘上的Lab Exercise 9,我们从图中可以看到,一个CPU包含了通用寄存器组R0~R7,一个ALU(算术逻辑单元),指令寄存器IR,控制器(一般这部分是一个有限状态机或 者是用微指令实现),还有就是数据通路(图中的连线)。当然真正的CPU不可能只包含这么一点点组件,这是一个模型CPU,也就是说只是说明CPU的原 理,真正复杂的CPU要涉及到很多复杂的结构和时序,例如虚拟模式需要使用一些特殊的寄存器、为了支持分页需要使用页表寄存器等,为了加速内存的访问需要 使用TLB,加速数据和指令的访问而使用data cache和instruction cache等等。。。。。当然,那都是后面该考虑的,所以我们先从这个简单的部分开始讲起。

例子中能实现如下指令:

mv指令将Ry的数据转移到Rx中,mvi将立即数D转移到Rx当中,add将Rx和Ry的和放到Rx中,sub同上,不过执行的是减法。

首先来说明mv指令是如何执行的:mv指令将Ry的值移入Rx寄存器当中,这两个寄存器都是由一组D触发器构成,而D触发器的个数取决于寄存器的宽度,就像 32位机、64位机这样,那他们的寄存器使用的D触发器的个数就是不一样的。当执行mv rx,ry时,中间的多路器(图中最大的那个multiplexer)选通Ry,让Ry寄存器驱动总线,这个时候Bus上的信号就是Ry的值;然后再看到 R0~R7上分别有R0in~R7in信号,这个信号是使能信号,当这个信号有效时,在上升沿此触发器会将din的数据输入,所以说到这里大家一定想到 了,这个时候Rx触发器上的Din信号就会变为有效,这样过了一个时钟周期后Ry的值就被送到了Rx当中。

与mv指令类似,mvi指令也将一个数据送入Rx当中,只不过这次的数据存在指令当中,是立即数,所以Rx的Din信号会变为有效,而多路器会选择IR中的数据,因为mvi指令的立即数存在指令当中。并且进行一定处理,例如扩展等。

add 指令会让多路器先选择Rx,然后Ain信号有效,这样一个时钟周期后,Rx数据被送入Alu的A寄存器当中,这时多路器选择Ry,addsub信号为 add以指示ALU进行加法操作,Gin有效让G寄存器存放运算结果,然后再过一个时钟周期G当中的数据就是Rx与Ry的和,这时多路器再选择 Gin,Rx的Din有效,过了一个时钟周期后数据就被存放到Rx当中了。

sub的过程与add差不多,不过addsub信号是sub指示ALU进行减法。

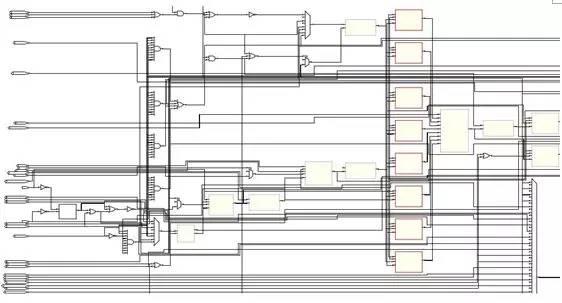

我做的CPU模型

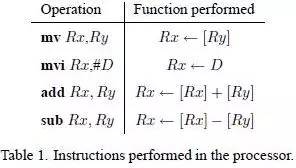

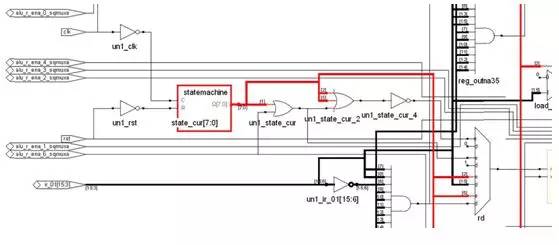

下面我就将我做的CPU模型的RTL网表发出来,代码我会上传的,但是这个还只能进行仿真,因为设计 的时候理念有问题,出现了异步设计,而且出现了将状态机的输出作为另一个器件的时钟端的错误,所以这个模型只能用于仿真。我用的synplify pro综合出的RTL,而状态转移图是用的Quartus的FSM Viewer截下来的。

首先是整个系统的概览:

这个比上面的那个简单模型复杂多了吧!但是别担心,其实这个只是上面的那个CPU变得稍微复杂了一点,这个和上面那个不同的地方还有:这个CPU是一个多周期CPU而上面的Lab Exercise是一个单周期的CPU

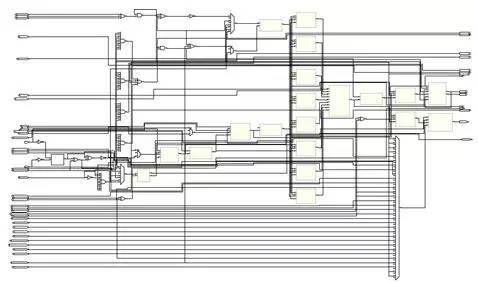

下图是程序计数器(PC),也就是常见x86处理器里面的ip(instruction poiniter):

红色部分就是pc了,后面是一个三态桥,连接到了总线上面,这里的数据有时候是要送到地址总线,用于寻内存中的数据,以便完成Instruction Fetch过程。有时候又要送到通用寄存器的数据端,用于将pc的值送到其他寄存器。

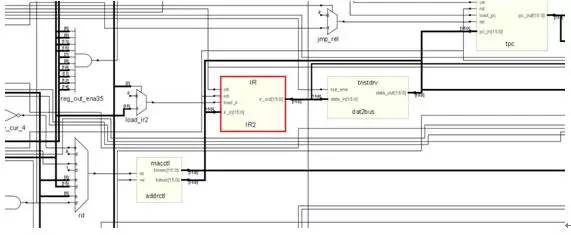

下面这个是IR(Instruction Register),这个是多周期处理器的典型特征,因为处理器在第一个周期里面将机器码从内存取出,然后存放到这个寄存器里面,后面的几个状态都是通过这个寄存器里面的数据作为指示执行操作的。

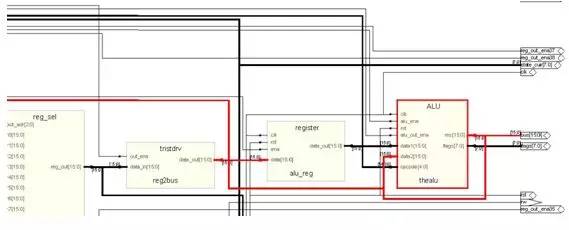

下面介绍一下ALU,ALU是Arithmetic Logic Unit,即算术逻辑单元,这个装置的作用是进行算术操作和逻辑操作。典型的算术操作例

如:1+1=2,11x23=253,而典型的逻辑操作例如:1 and 1=1,0 or 0 = 0,1<<3=8这种属于逻辑操作。

而从图中大家也看得到,ALU的输出用一根很长的线连接到了后面,参考整个CPU的图的话,会发现这些线连到了通用寄存器上面,这是为了让运算的结果存放回 去,例如你用add eax,1的时候,eax的值被加上1然后放回eax,所以ALU的运算结果要用反馈送回到通用寄存器,而ALU的输入也应该有通用寄存器的输出。

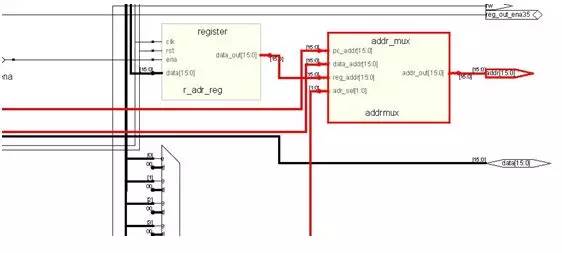

下面再介绍ADDRMUX:

这个部件是用来选择地址的,右边的输出是CPU的地址总线,而CPU的地址总线就已经送出CPU了(也就是你能够在芯片的外表上看到引脚了),CPU的地址总线是送到存储器的地址端的,而现代的计算机系统实际上是相当复杂的,所以其实你家的计算机上CPU是通过北桥芯片访问内存的(当然也有将内存控制器做到 CPU里面的)左边是地址的来源,地址的来源即有通用寄存器,也有程序计数器,还有一个是直接从IR里面送出,这是因为有的立即数里面也包含内存地址信息。

最后介绍通用寄存器:

通用寄存器的作用就是用来保存中间值或者用于运算,例如

add eax,2

相当于eax+2然后送回eax。

最后介绍一下状态机,这个部分就是CPU的“灵魂”,如果说有了上面那些部件CPU有了一副“躯体”的话,这一部分就是CPU的“灵魂”了:

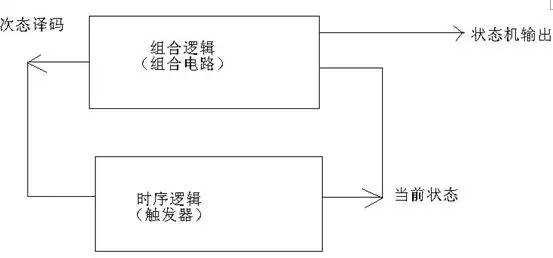

状态机基本上与系统所有的组件都连接到一起了,因为上面所说的所有动作的执行,都需要状态机的控制,状态机其实就是由一部分触发器构成的记忆电路和另外一部 分组合逻辑构成的次态译码电路构成,还有根据当前状态和输入进行译码的部分用于控制各个部件,下面是教科书上的典型FSM结构:

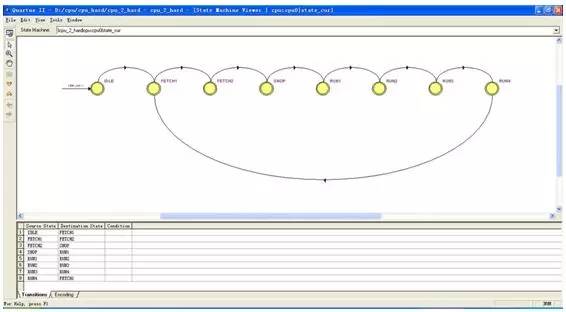

而我们用的状态机状态转移图如下:

因为这个处理器设计的很简单,所以没有出现很多状态,当处理器经历完以上的状态之后,处理器就执行完了一条指令。

有的CISC的处理器用微指令进行控制,作用和状态机相近,这种结构出现在一些比较古老的处理器上,因为那个时候的设计工具和方法没有现在的先进,所以往往 改动硬件是困难的和高成本的,所以用微指令的话,做好了硬件的结构,要是需要改动只要修改微指令就好了,而现在的电子技术很发达,设计工具也很完备,所以 就有很多直接通过硬连线实现的处理器。

好马配好鞍,有了处理器,我们就得给它配上一个好的程序,下面我们就用自己设计的处理器进行求和,从1加到100,因为我们没有设计编译器,也没有设计汇编器,所以程序只能用机器码写出,示例程序如下:

我们不妨先写出程序的汇编代码:

mov [ADDR],r0;r0 = 0

mov r1,100

lop:add r2,r1

sub r1,1

cmp r1,0

jz ext

mov r4,4

jmp r4(lop)

ext:mov [ADDR],r2

jmp $

先将内存中存放数据的地址清零,这样才能存放等下送来的结果,然后将r1寄存器存入循环次数(也就是求和的上限)。然后再将r1的值加到r2中来,r2其实就是放求和的寄存器,最后我们会将r2中的值送到内存中的某个地址存放的。

然 后将r1减去1,看看是否为0?如果为0则说明求和结束了,如果不是0则说明还要继续,结束后程序就跳到ext部分将结果存放到内存中某个地址(例子中给 的是49152也就是二进制的1100000000000000b),最后jmp $是为了让程序停在这一行,防止程序跑飞(跑飞的程序危害很大!有可能吧数据当代码或者把代码当数据!)

转换成VerilogHDL语言如下:

module memory

(

input [15:0] addr,

inout [15:0] data,

input rw

);

reg [15:0] data_ram[0:16'b1111_1111_1111_1111];

integer i;

initial begin

for (i = 0; i <= 16'b1111_1111_1111_1111; i = i + 1)

data_ram[i] = $random();

data_ram[0] = 16'b1000000100000000; //mov [ADDR],r0;r0 = 0

data_ram[1] = 16'b1100000000000000; //ADDR

data_ram[2] = 16'b1000000010001000; //mov r1,100

data_ram[3] = 100; //100

//data_ram[2] = 16'b1110011001000000;

data_ram[4] = 16'b0010000100010001; //lop:add r2,r1

data_ram[5] = 16'b1110000011001000; //sub r1,1

data_ram[6] = 16'b0000000000000001; //1

data_ram[7] = 16'b1110000000001000; //cmp r1,0

data_ram[8] = 16'b0000000000000000; //0

data_ram[9] = 16'b1110011010000000; //jz ext

data_ram[10] = 16'b0000000000000011; //+3 offset(ext)

data_ram[11] = 16'b1000000010100000;//mov r4,4

data_ram[12] = 16'b0000000000000100;

data_ram[13] = 16'b0110011001100000;//jmp r4(lop)

data_ram[14] = 16'b1000000100000010;//ext:mov [ADDR],r2

data_ram[15] = 16'b1100000000000000;//ADDR

data_ram[16] = 16'b1110011001000000;//jmp $

data_ram[17] = 16'b1111111111111110;//-2 offset($)

/*data_ram[0] = 16'b1000000010000000; //mov r0,imm

data_ram[1] = 16'b0011111111111111; //imm

data_ram[2] = 16'b0000000001111000; //mov r7,r0

data_ram[3] = 16'b1000000010011000; //mov r3,0

data_ram[4] = 16'b0000000000000000;

data_ram[5] = 16'b1000000010100000; //mov r4,code of jmp r5

data_ram[6] = 16'b0110011001101000; //jmp r5

data_ram[7] = 16'b0000000101011100; //mov [r3],r4

data_ram[8] = 16'b1000000011110000; //mov r6,[0]

data_ram[9] = 16'b0000000000000000; //[0]

data_ram[10]= 16'b1000000100000110; //mov [255],r6

data_ram[11]= 16'b0000000011111111;

data_ram[12]= 16'b0110011001011000; //jmp r3

*/

end

always @ (addr or rw or data)

if (rw)

data_ram[addr] = data;

assign data = rw ? 16'hzzzz : data_ram[addr];

endmodule

设计中CPU外围还需要一个内存设备(Memory),我用HDL对其建模,初始化的时候每个内存地址上对应的数据都初始化为随机的,然后只有从0开始的一系列地址被初始化为我写的代码,机器码对应的汇编指令在注释中已经给出。

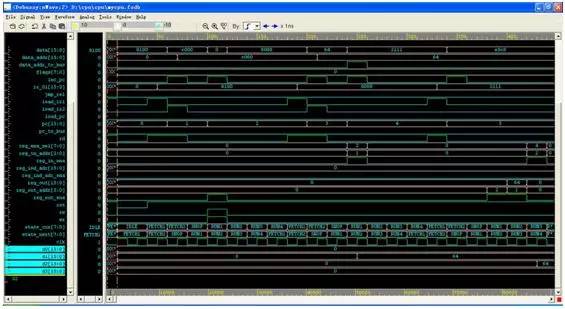

然后是结果,结果应该是r2从0变化到5050(1+2+3+......+100=5050)

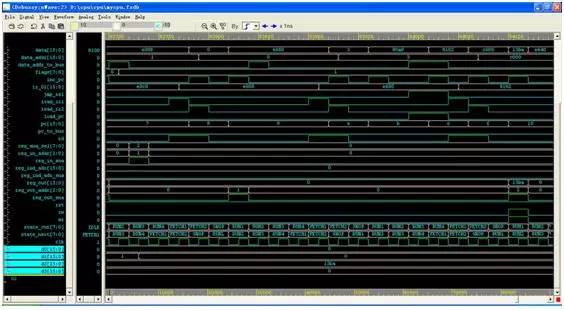

而r1则从100变化到0,变化到0后程序将进入死循环,停止在jmp $那一条。这是仿真开始的时候:

大家可以看到初始化后,d0~d7都变成了0,这是r0~r7寄存器的Q端,而state_current和state_next则是状态机的现态和状态机 的次态,cpu的各个部件都通过这个状态机受到控制。状态名出现的顺序和上面的FSM Viewer的连线顺序是一样的。

而且大家可以看到,d2从0变化到了0x64也就是十进制100,说明已经执行了第一次加法了。

再来看看仿真结束:

这时候d1变化到了0而d2变化到了0x13ba(十进制的5050),说明程序已经在我们设计的处理器里面运行并且成功的得出了结果!

最后给出一些我用到的指令(跟x86的很像):

add dst,src 将src和dst相加并且送到dst寄存器中

mov [addr],src 将src的值送到以addr位地址的内存单元

sub dst,src 将dst减去src并且送到dst中去

cmp dst,src 将dst减去src 然后不送到dst中 只改变标志位

jz dst 当zf=1时(即上次的算术操作结果为0)则跳转到dst中去

最后再提一下:

我是用synplify综合的电路,然后用debussy+modelsim仿真的,

相关资料请参考:

CPU逻辑设计,朱子玉,李亚民著

Lab Exercise 9出自DE2的开发光盘

(作者:大法师千寻 来源:百度贴吧 http://tieba.baidu.com/p/1177032485?pn=1)

原文标题:大师教你如何制作一个简单的16位CPU

文章出处:【微信公众号:玩转单片机】欢迎添加关注!文章转载请注明出处。

-

自己动手做操作系统(附光盘)2008-10-17 6467

-

自己动手做简单移动电源2012-10-26 54187

-

自己做一个项目比看十个教程都管用2013-03-07 11243

-

自己动手做单片机的问题2013-04-05 2494

-

冰雪的STM32 参加自己动手做示波器活动2015-06-09 3296

-

自己动手做的VI2016-04-23 2515

-

怎么用最基本的元件做一个遥控钥匙,我想自己动动手做一个2018-03-15 3819

-

自己动手做原电池2009-10-22 2537

-

自己动手做-制作简易扬声器2010-01-04 14243

-

自己动手DIY录音机2016-01-07 4423

-

DIY:自己动手做数码相机2017-01-24 1228

-

超简单!如何自己动手做一个简易的逆变器?2018-08-07 65440

-

自己动手做简单移动电源 - 工程师创意 - 中国电子技术论坛 - 最好最受欢迎电子论坛!...2022-01-05 1495

-

万圣节来临,动手做一个无线充电的南瓜灯吧2022-11-07 595

-

自己动手做一个好玩的POV显示设备2024-12-25 3321

全部0条评论

快来发表一下你的评论吧 !