基于FPGA的低压差正压可调稳压器应用电路设计

电源设计应用

455人已加入

描述

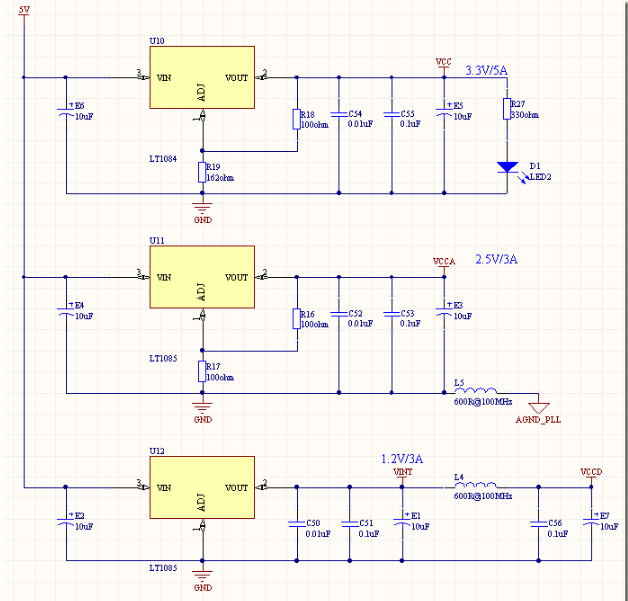

LDO(低压差线性稳压器),FPGA需要3.3V、2.5V和1.2V,可选用凌力尔特LINEAR:LT1083/84/85,低压差正压可调稳压器。

应用电路如图所示:

输入端加10UF电解电容,输出端加10UF胆电容。

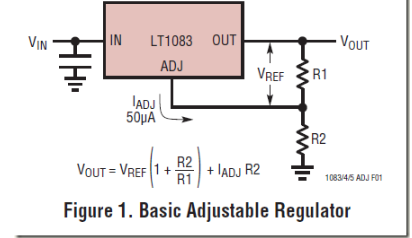

基本可调稳压器电路图如上图所示,通过改变R1、R2阻值输出需要的电压值,由于Iadj很小,计算时可以忽略不计。故等式变为:

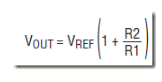

,其中,Vref=1.25V。

,其中,Vref=1.25V。

电路板电源设计如下图所示:

3.3V:R1=100Ω,R2=162Ω

2.5V:R1=R2=100Ω

1.2V:ADJ直接接地,1.25V≈1.2V

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

低压差稳压器的基本定义和特性2025-06-05 2177

-

LDO低压差稳压器电路设计2025-05-06 312

-

面向可调低压差稳压器的降噪网络2023-11-24 519

-

低压差线性稳压器是什么2021-11-15 3150

-

集成稳压器的种类2021-11-12 2956

-

低压差稳压器2021-11-07 1100

-

带低压差稳压器的模拟集成电路设计2021-07-14 1672

-

AN-1329:面向可调低压差稳压器的降噪网络2021-03-19 791

-

1.5A高精度的低压差稳压器2020-08-19 2155

-

具有可调输出的低压差线性稳压器2020-03-26 2669

-

用于NCV47411双通道可调节低压差稳压器的评估板2019-07-12 2146

-

可调节输出低压差稳压器的降噪网络2016-01-07 888

-

低压差稳压器电路2009-10-13 1294

-

多端可调稳压器的应用电路2008-05-02 1168

全部0条评论

快来发表一下你的评论吧 !