同相不同频的跨时钟域路径介绍

描述

同步时钟是指发送时钟和接收时钟是由同一个MMCM或PLL生成,两者之间有明确的相位关系。例如:两者可以是同频但有固定相差;或者同相但不同频。这里我们重点介绍一下同相不同频的跨时钟域路径,分两种情形:从慢时钟到快时钟和从快时钟到慢时钟。

从慢时钟到快时钟

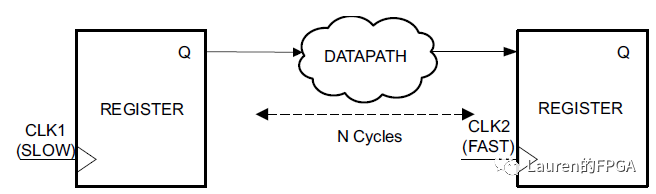

如下图所示,这里假定CLK2的频率是CLK1的3倍。这实际是条多周期路径。

发送时钟和接收时钟之间的关系如下图所示。

在只有时钟周期约束而没有多周期路径约束的情况下,STA(Static Timing Analysis)工具会认为建立时间检查和保持时间检查如下图所示。不难看出,保持时间检查是合理的,但建立时间检查不是期望的。换言之,建立时间如果按此分析就会过紧。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- 同步时钟

-

如何处理跨时钟域这些基础问题2024-01-08 1341

-

FPGA跨时钟域处理方法(一)2023-05-25 2914

-

跨时钟域电路设计总结2023-05-18 1340

-

揭秘FPGA跨时钟域处理的三大方法2022-12-05 2394

-

关于跨时钟域信号的处理方法2022-10-09 8107

-

介绍3种方法跨时钟域处理方法2021-09-18 23255

-

如何处理好FPGA设计中跨时钟域间的数据2021-07-29 1650

-

关于跨时钟域的详细解答2021-04-27 4966

-

CDC单bit脉冲跨时钟域的处理介绍2021-03-22 4207

-

vivado约束案例:跨时钟域路径分析报告2020-11-27 6736

-

FPGA设计中解决跨时钟域的三大方案2020-11-21 4990

-

关于FPGA中跨时钟域的问题分析2019-08-19 3885

-

跨时钟域的时钟约束介绍2018-07-03 4638

-

cdc路径方案帮您解决跨时钟域难题2017-11-30 8588

全部0条评论

快来发表一下你的评论吧 !