PHY的管理接口MDIO/MDC时序图解析

电子说

描述

MDC/MDIO接口是为MII总线接口定义的,在802.3协议clause 22中有详细的介绍,MII用于连接MAC和PHY,包含两种信号:

1. 数据接口,用于MAC和PHY之间接收和发送以太网数据

2. 一个PHY管理接口,即MDIO接口,用于读写PHY的控制寄存器和状态寄存器。

本文主要描述PHY的管理接口,MDIO/MDC.

MDIO 总线只支持 MAC 作为主设备,PHY 作为从设备。MIDO 支持两种时序,分别为 Clause 22 和 Clause 45.

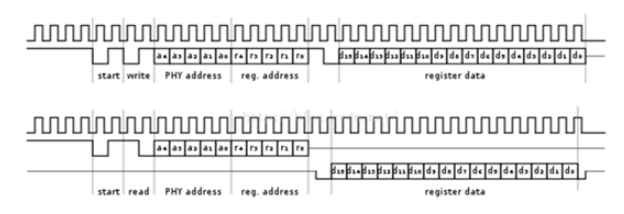

MDIO clause 22 是 MDIO 使用的一种信号时序,在这个信号时序模式,MAC 先向 MDIO 信号线上拍 32 个周期,接着传输 16 bit 的控制位。16 个信号位包含了两个开始位, 2 个访问控制位,5 bits 的 PHY 地址,5 bits 的寄存器地址,以及 2 bits 的翻转位。 当进行写操作的时候,MAC 在接下来的周期中提供地址和数据;当进行读操作的时候, PHY 会翻转 MDIO 之后向 MDIO 信号线上发送数据。

MDIO 也支持 Clause 45 时序,其是 Clause 22 的拓展协议。与 Clause 22 不同的是, 16 位中的起始位:Clause 22 是 00, 而 Clause 45 是 01.

MDC (Management Data Clock), MDC是由MAC管理实体输出给PHY,作为管理数据MDIO的参考时钟信号,在上升沿触发MDIO的读写。MDC是一个非周期性的信号,最小时钟周期为400ns,与MII中的TX_CLK和RX_CLK无关。

MDIO(Management Data Input Output),MDIO是一个双向信号线,用来传输PHY的控制和状态信息。控制信息由MAC驱动,状态信息有PHY驱动。MDIO信号线初始为三态,由MAC或者PHY来驱动信号。

MDC/MDIO时序图

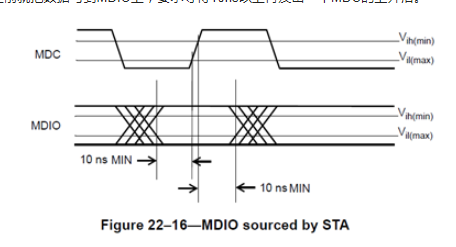

当MDIO由MAC驱动的时候,MAC芯片提供最小10ns的建立时间和最小10ns的保持时间。

需要注意的是,为了保证PHY能准确采样,当MAC向MDIO写数据的时候,需要在MDC的上升沿之前就把数据写到MDIO上,要求等待10ns以上再发出一个MDC的上升沿。

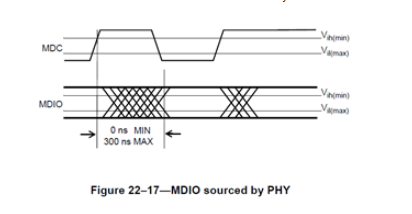

当MDIO由PHY芯片驱动时候,由MAC芯片在MDC的上升沿进行采样。而为了保证MAC能准确采样,当PHY向MDIO写数据时,这个clock-to-data的delay时间范围可以是0-300ns(小于上面提到的400ns)。

Preamble+Start:32bits的前导码以及2bit的开始位。

OP Code:2bits的操作码,10表示读,01表示写

PHYAD:5bits的PHY地址,一般PHY地址从0开始顺序编号,例如6口switch中PHY地址为0-5。

REGAD:5bits的寄存器地址,即要读或写的寄存器。

Turn Around:2bits的TA,在读命令中,MDIO在此时由MAC驱动改为PHY驱动,并等待一个时钟周期准备发送数据。在写命令中,不需要MDIO方向发生变化,则只是等待两个时钟周期准备写入数据。

Data:16bits数据,在读命令中,PHY芯片将读到的对应PHYAD的REGAD寄存器的数据写到Data中,在写命令中,MAC将要写入对应PHYAD的REGAD寄存器的值写入Data中。

Idle:空闲状态,此时MDIO无源驱动,处高阻状态,但一般用上拉电阻使其处在高电平。

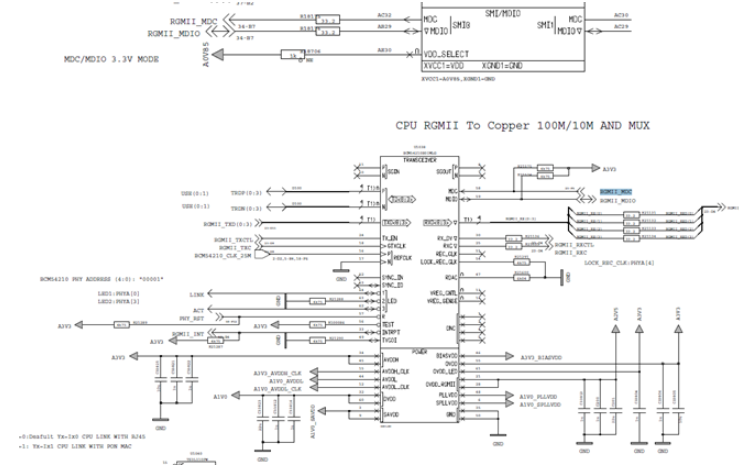

Marvel CN71XX的SMI电路图

CN71XX的CPU有两个SMI的管理接口,其中SMI0连接到了BCM54210的PHY芯片。

-

efans_da3e13

2023-08-23

0 回复 举报clause 22是01,clause 45是00。两个反了。 收起回复

efans_da3e13

2023-08-23

0 回复 举报clause 22是01,clause 45是00。两个反了。 收起回复

-

可以在任何FLEXCOMM接口上使用MDIO吗?2025-04-08 857

-

基于FPGA的MDIO接口读写测试方案2023-10-01 4752

-

LS1046双10G XFI PHY MDIO问题如何解决?2023-05-09 799

-

使用不同的以太网PHY,MDC信号的问题求解2023-03-23 879

-

Marvell交换芯片介绍之MII、MDIO2023-01-26 10996

-

CH563能否支持SMI(MDC/MDIO),能否管理其他的网络芯片?2022-06-09 816

-

CH32V307VCT6使用RGMII接口实现千兆以太网是否不具备MDC和MDIO来控制和配置PHY?2022-05-31 3613

-

请问stm32是怎样配置PHY芯片的呢2022-01-19 1991

-

通过MDIO接口管理PHY芯片的验证设计方案2020-12-29 9400

-

MDIO接口的基础知识详解2020-09-29 50273

-

【正点原子FPGA连载】 第二十四章MDIO接口读写测试实验-领航者ZYNQ之FPGA开发指南2020-09-27 1671

-

以AR8031 为例解读sgmii的PHY芯片(实用版)2019-12-26 9091

-

【MYD-CZU3EG开发板试用体验】【以太网入门】 使用MDIO2019-10-27 2182

-

请教关于c6748的MDIO接口读写phy的问题2018-07-25 3575

全部0条评论

快来发表一下你的评论吧 !