详解移位寄存器,串行输入和串行输出的分析

描述

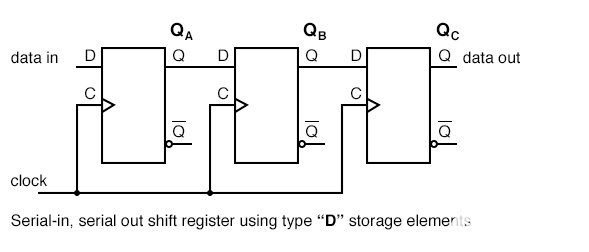

串行输入,串行输出移位寄存器每级将数据延迟一个时钟时间。它们将为每个寄存器存储一点数据。串行输入,串行输出移位寄存器的长度可能为一到64位,如果级联寄存器或封装,则长度会更长。下面是一个单级移位寄存器,用于接收与寄存器时钟不同步的数据。

当时钟由低变高时,D FF(触发器)类型的D引脚上的“数据输入” 不会改变电平。我们可能希望将数据同步到电路板上的系统级时钟,以提高数字逻辑电路的可靠性。

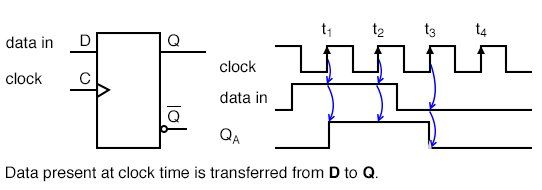

上面所示的明显点(与下图相比)是,在D FF类型的D引脚上存在的任何“数据输入”都在时钟时间从D传输到输出Q。由于我们的示例移位寄存器使用的是上升沿敏感的存储元件,因此当时钟从低到高转换时,输出Q跟随D输入,如上图的向上箭头所示。

毫无疑问,在时钟时间存在什么逻辑电平,因为数据在时钟沿之前和之后都稳定。在多级移位寄存器中很少出现这种情况。但是,这是一个简单的例子。我们只关心从低到高的正时钟沿。下降沿可以忽略。很容易看到Q在上面的时钟时间跟随D。将其与下图比较,其中“数据输入”似乎随时钟的上升沿而变化。

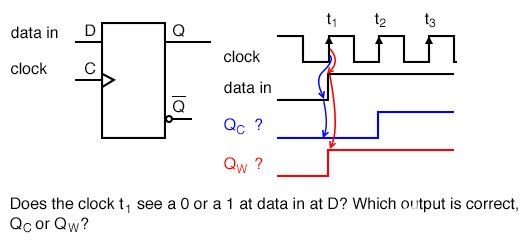

由于“数据输入”似乎在上述时钟时间t 1发生了变化,因此D FF 类型在时钟时间会看到什么?简短的简化答案是,它会在时钟之前看到D处存在的数据。那就是在时钟时间t 1传输到Q的内容。正确的波形是Q Ç。如果在t 1处 Q还不是零,则Q变为零。所述d寄存器不看到一个直到时间t 2,在该时间Q变高。

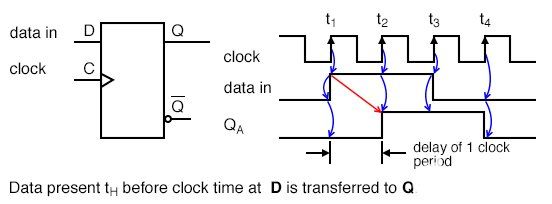

由于在D处出现的上述数据在某个时钟时刻被计时到Q,并且Q直到下一个时钟时刻才能改变,因此D FF将数据延迟一个时钟周期,前提是该数据已与该时钟同步。Q A波形与“数据输入”相同,但延迟一个时钟周期。接下来将详细介绍D型触发器的输入在时钟时间的情况。

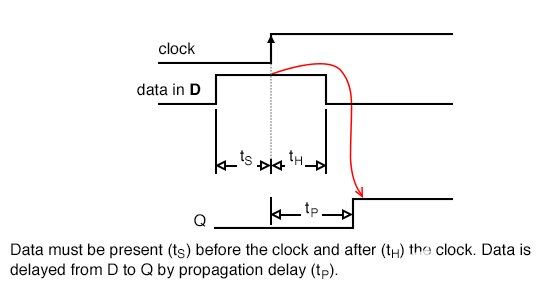

请参考下图。由于“数据输入”似乎在时钟时间(以上)发生变化,因此我们需要更多信息来确定D FF看到的内容。如果“数据输入”来自另一个移位寄存器级,另一个相同的D FF,我们可以根据数据手册信息得出一些结论。数字逻辑制造商在数据表中提供了有关其零件的信息,以前仅在称为数据手册的集合中可用。数据手册仍然可用;但是,制造商的网站是现代资源。

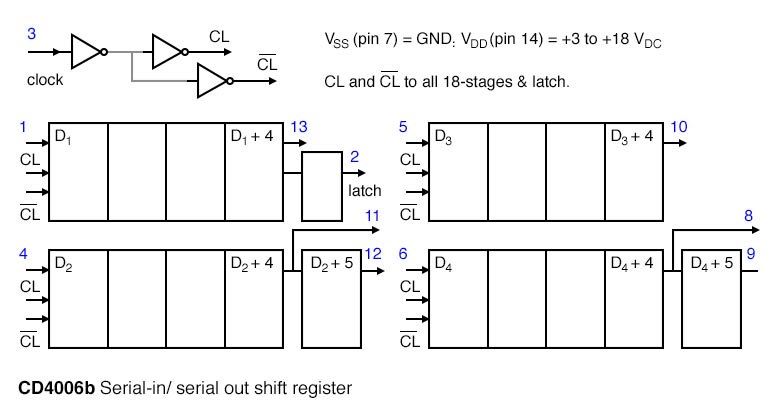

下面的数据是从CD4006b数据表中提取的,用于在5V DC下工作,这是一个说明时序的示例。[*]

t S = 100ns

t H = 60ns

t P = 200-400ns典型值/最大值

t S是建立时间,时间数据必须在时钟时间之前存在。在这种情况下,数据必须在时钟之前的D 100ns 出现。此外,必须在时钟时间之后将数据保持时间 t H = 60ns。必须满足这两个条件,才能将数据从D可靠地时钟到触发器Q。满足60ns的建立时间没有问题,因为如果D处的数据来自另一个移位寄存器级,则该数据在整个先前的时钟周期内一直存在。

例如,在1 Mhz的时钟频率下,时钟周期为1000 µs,这是很多时间。实际上,数据将在时钟之前存在1000µs,这比60ns 的最低要求t S大得多。之所以满足保持时间t H = 60ns,是因为连接到另一级Q的D的变化不能快于前一级t P = 200ns 的传播延迟。只要前一个D FF 的传播延迟大于保持时间,就可以满足保持时间。

对于CD4006b,由另一级Q驱动的D处的数据变化不会快于200ns。总而言之,如果触发器级联到多级移位寄存器中,则输出Q在接近时钟时间跟随输入D。

三个D型触发器在Q到D之间级联,并且时钟并行,以在上面形成三级移位寄存器。

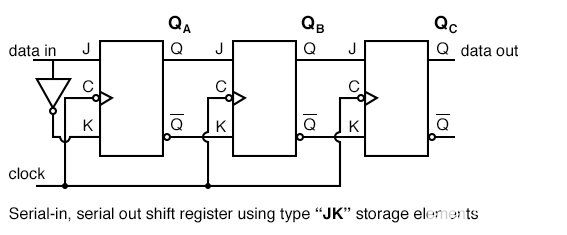

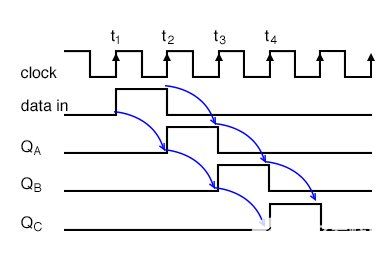

键入JK翻转Flopss级联Q可J,Q”至K的时钟在平行于上述得到的移位寄存器的另一种形式。串行输入/串行输出移位寄存器具有时钟输入,数据输入和最后一级的数据输出。通常,其他级输出不可用,否则它将是一个串行输入,并行输出移位寄存器。以下波形适用于串行输入,串行输出移位寄存器的前两个版本之一。三对箭头表示三级移位寄存器临时存储3位数据,并将其从输入到输出延迟三个时钟周期。

在时刻t 1 “数据中”的0是从计时d到Q的所有三个阶段。特别地,阶段A的D看到逻辑0,该逻辑0被计时到Q A,在这里它一直保持到时间t 2。在时刻t 2 “数据在”的1从计时d至Q A。在阶段乙和Ç,一个0,从先前级供给的计时至Q 乙和Q Ç。

在时刻t 3 “数据中”的0是从计时d至Q A。由于“ data in”为0, Q A变为低电平并在其余时钟中保持低电平。由于前一级为1,Q B在t 3处变高。由于前一阶段的较低,在t 3之后Q C仍然较低。由于从前一级Q B馈入D的高电平,Q C最终在时钟t 4处变为高电平。所有早期阶段都有0 s移入其中。并且,在t 5的下一个时钟脉冲之后,所有逻辑1 s将被移出,取而代之的是0 s

串行输入/串行输出设备

我们将仔细研究一下德州仪器(TI)提供的以下集成电路零件。

CD4006b 18位串行输入/输出移位寄存器

CD4031b 64位串行输入/输出移位寄存器

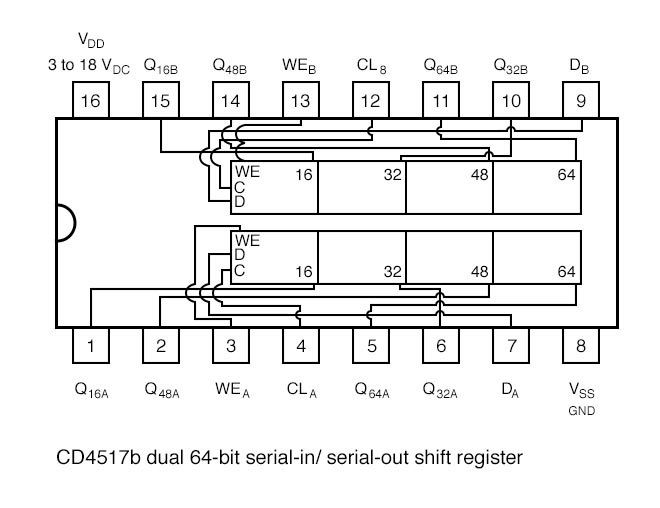

CD4517b双64位串行输入/输出移位寄存器

以下串行输入/串行输出移位寄存器是4000系列CMOS(互补金属氧化物半导体)系列器件。因此,他们将接受3到15伏的V DD正电源。V SS引脚接地。移位时钟的最大频率随V DD变化,为几兆赫兹。

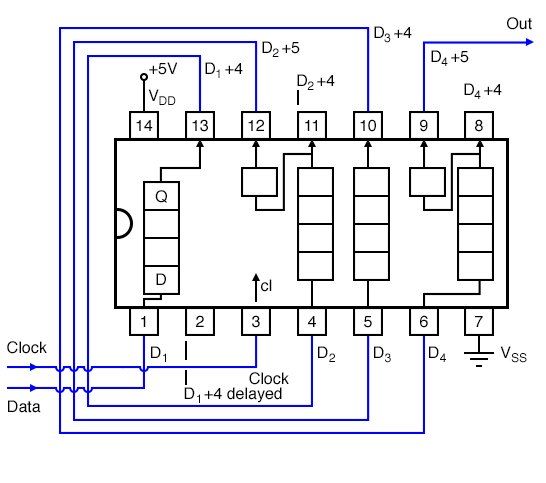

18位CD4006b由两级4位和另外两级5位组成,输出抽头为4位。因此,5位级可以用作4位移位寄存器。要获得完整的18位移位寄存器,必须将一个移位寄存器的输出级联到另一个移位寄存器的输入,依此类推,直到所有级都创建一个移位寄存器,如下所示。

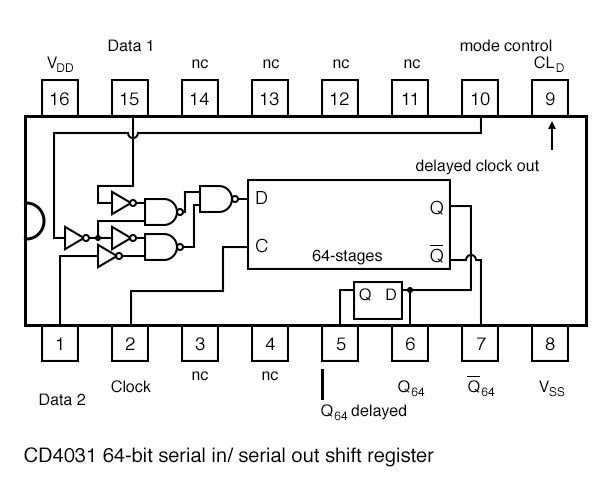

CD4031 64位串行输入/输出移位寄存器如下所示。未连接许多引脚(nc)。Q和Q“是可从第64阶段,实际上Q 64和Q” 64。还有一个Q 64从半级“延迟”,它延迟了半个时钟周期。一个主要功能是数据选择器,它位于输入到移位寄存器的数据上。

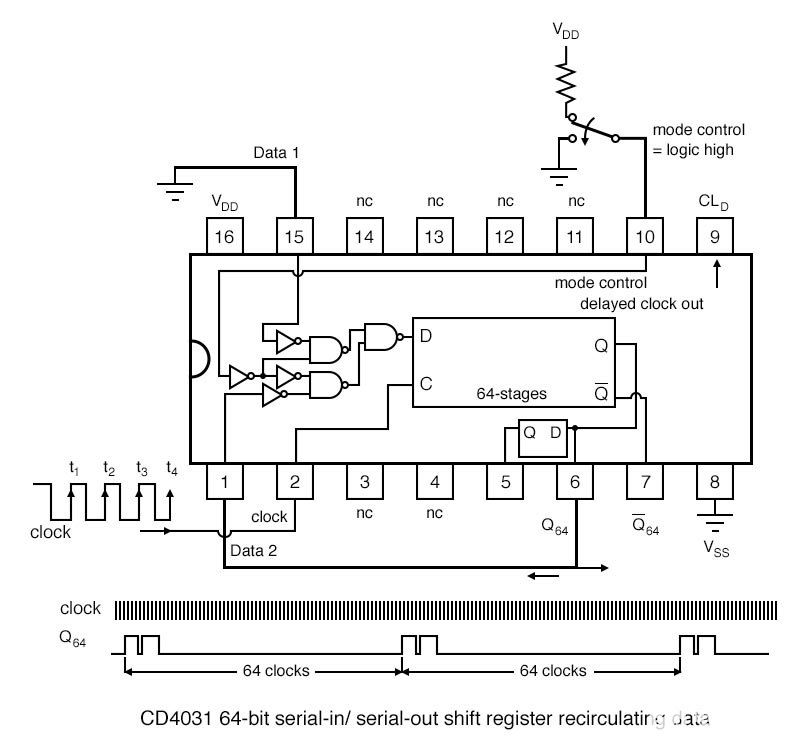

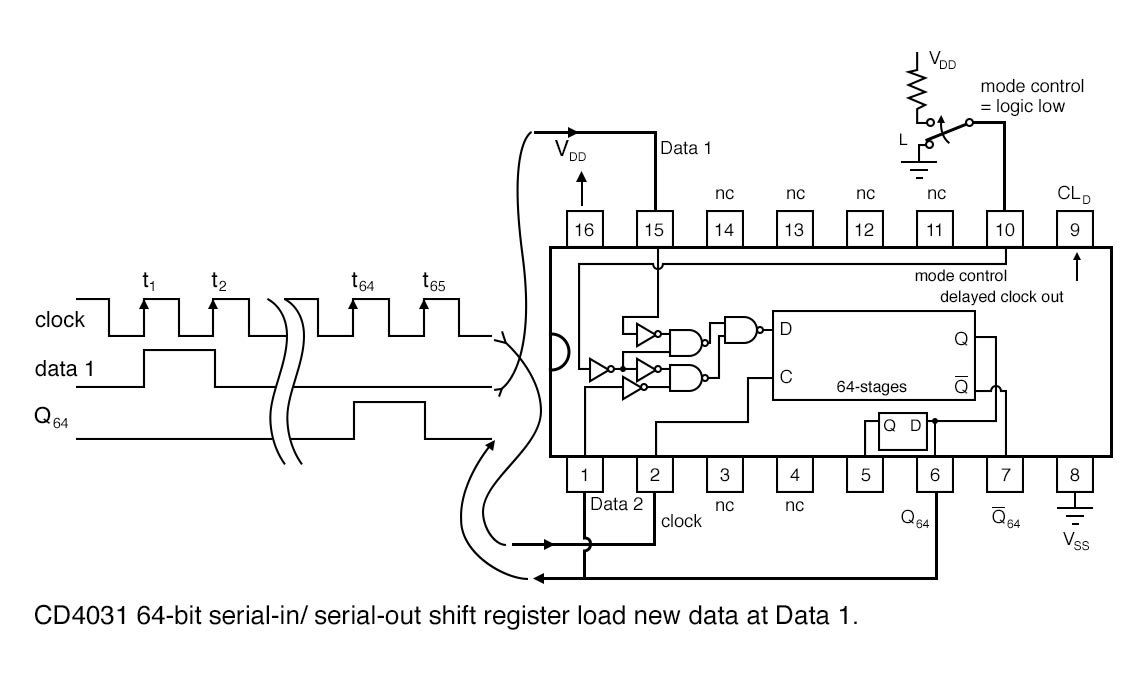

“模式控制”在两个输入之间进行选择:数据1和数据2。如果“模式控制”为高,将从“数据2”中选择数据以输入到移位寄存器。在“模式控制”为逻辑低的情况下,选择“数据1”。下面的两个图中显示了此示例。

上面的“数据2”连接到移位寄存器的Q 64输出。当“模式控制”为高电平时,Q 64输出被路由回到移位器数据输入D。数据将从输出循环到输入。如上所示,数据将每64个时钟脉冲重复一次。出现的问题是该数据模式如何首先进入移位寄存器?

当“模式控制”为低电平时,选择CD4031“数据1”作为输入到移位器。输出Q 64不再循环,因为下部数据选择器门已禁用。“禁用”是指在较低的NAND门上两次反转为低电平的逻辑低“模式选择”阻止其将较低引脚(数据2)上的任何信号传递至栅极输出。因此,它被禁用。

上面显示了CD4517b双64位移位寄存器。请注意在第16、32和48阶段的抽头。这意味着可以使用64位移位器之一来配置这些长度的移位寄存器。当然,可以将64位移位器级联以产生80位,96位,112位或128位移位寄存器。级联两个移位器时,时钟CL A和CL B需要并联。WE B和WE B为正常变速操作接地。

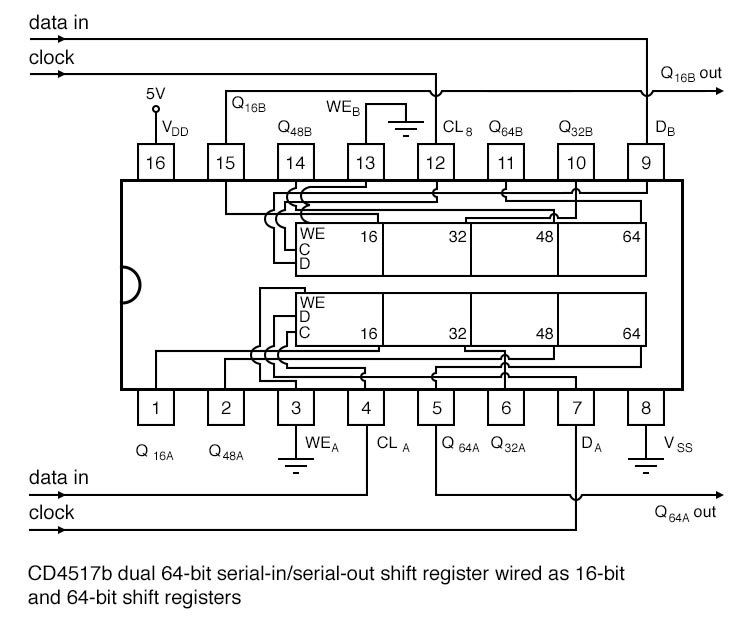

数据输入到移位寄存器A和B是d 阿和d 乙分别。假设我们需要一个16位的移位寄存器。可以用CD4517b进行配置吗?同一部分的64移位寄存器怎么样?

上面我们显示了CD4517b,它被连接为B部分的16位移位寄存器。B部分时钟CL A。数据在CL B处计时。然后从Q 16B提取延迟了16个时钟的数据。写入使能WE B接地。上面我们还显示了与独立部分A的64位移位寄存器连接的相同CD4517b。对于A部分中的时钟是CL A。在CL的数据进入A。从Q 64A拾取延迟了64个时钟脉冲的数据。WE A(A部分的写使能)已接地。

fqj

-

74AHCT595:8位串行输入/串行输出或并行输出移位寄存器的深度剖析2026-03-13 642

-

8位并行输入/串行输出移位寄存器-74LV165A2023-03-03 706

-

带输出锁存器的8位串行输入/串行输出或并行输出移位寄存器-74AHC_AHCT595_Q1002023-02-20 553

-

带输出锁存器的8位串行输入/串行输出或并行输出移位寄存器-74VHC_VHCT595_Q1002023-02-17 687

-

带输出锁存器的8位串行输入、串行或并行输出移位寄存器;3-状态-74HC_HCT5952023-02-15 668

-

8位并行输入/串行输出移位寄存器-74LV1652023-02-08 725

-

移位寄存器的设计与实现2022-09-06 6413

-

串行输入,串行输出的移位寄存器2020-10-08 4636

-

移位寄存器:串行输入,串行输出2020-09-24 6133

全部0条评论

快来发表一下你的评论吧 !