设计电路时怎么选取滤波电容?

电子说

描述

在很多场合,我们都会看到一个现象:集成芯片的电源端接了一个或多个电容到地。

这种电容叫做退耦电容,也可以叫做滤波电容,这个没有严格的区分。作用是为了去除电源端的的干扰和电源噪声,很多芯片对电源的要求是很高的,如果你电源端都是不稳定的或者带来了额外的噪声,那芯片的功能务必会受到很大的影响。

那我们在设计电路的时候该怎么选取滤波电容呢?

原理

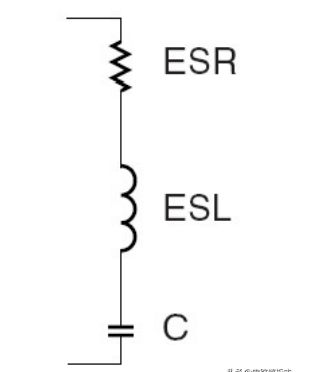

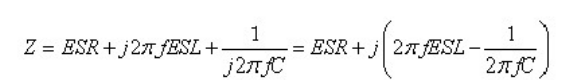

我们实际用的电容并不是理想的电容,我们用到的电容可以用上图的模型来代替:电阻(ESR)、电感(ESL)和电容C串联的电路形式。这样我们就可以得出一个电容的实际阻抗表达式:

Z(阻抗):Z=R(电阻)+jX(电抗)

X=wL-1/wC

XL=JwL

XC=1/jwC

下面,我们分两种情况来讨论下这个看上去比较复杂的表达式

1.高频(w很大)时,容抗(1/jwC)就趋近于0,但是感抗jwL会很大,这就导致了电容在高频的时候不再是电容了,它相当于一个电阻和一个很大的电感的串联,这样就会产生很大的阻抗Z,会对我们的高频信号产生很大的阻挡,高频信号就会被阻挡在外面过不去。

这时候我们得想个办法,如何能让高频信号过去呢?我们仔细看我们的Z阻抗表达式,我们发现高频信号过不去最主要的原因就是电感这个哥们太调皮了,竟敢一个人挡着我们的去路。所以,我们得叫一个帮手来帮助我们抵抗电感。我们将感抗(1/jwC)增大,因为它与感抗是一个减法关系(死对头)。感抗一增大,(jwL-j/wC)就会减小,Z就会减小。我们的高频信号就可以比较轻松的通过了。我们如何来增大感抗?减小C,j/wC就会增大。这样,我们就可以得出一个结论:小电容可以让我们的高频信号更轻松的通过!所以,在电源滤波中,小电容是用来滤除高频信号的。为什么说是滤除?因为高频信号都从电容上流向大地了,这样高频信号就不会对我的电源造成干扰,就可以成功地让电源保持稳定。

2.低频时(w较小时),感抗(jwL)就会变得很小,此时1/jwC就会变得很大,同样,它也造成了我们的阻抗Z变得很大,我们的低频信号就被阻挡了。分析方法同1是类似的,我们的目的就是减小阻抗,尽量让Z=ESR。这里与上面稍微有点不同,看感抗的表达式(XL=jwL),我们不能对它做什么,L是与工艺有关的,是一个固定的值。所以此时,我们就要去减小容(j/wC)。增大C,C就是你电容的值,它是可以改变的。所以,我们得出结论:大电容可以让低频信号更轻松地通过!所以,大电容滤除低频。

由于我们的电源是直流电(w=0),由于容抗j/wC会变得无穷大,所以直流电就通过不了电容,就可以稳稳当当地供给我们的芯片了。在实际应用中,为了由更好的频率范围,我们会用一个大电容和小电容并联的组合(两者之间的数量级一般至少是100以上)。

电容取值

每种电容都有自己的V型曲线(不同的滤波范围),有兴趣的朋友可以去看一下V型曲线。

下图是电容取值的参考值:

我刚开始的时候,也不懂为什么电容要这么取,我问过很多人,他们多说这是经验,你多试试,达不到你要求,你就换电容嘛!我想说的是,实践才是检验真理的唯一标准!

-

请问滤波电路的电容为什么要选取高精度的?2023-11-13 675

-

电源滤波电容如何选取?2023-06-06 4127

-

电源滤波电容的选取2022-01-11 977

-

滤波电容的选取选用原则2021-10-29 994

-

如何选取电源滤波电容?2021-06-18 2486

-

电源滤波电容如何选取资料下载2021-03-29 982

-

电源滤波电容选取详解2018-08-07 2033

-

什么是滤波电容_滤波电容大小计算公式及选取2018-02-11 114391

-

滤波电容大小选取与pcb摆放顺序2018-01-14 19204

-

详细解析电源滤波电容的选取与计算2018-01-09 6057

-

滤波电容要如何选取2017-08-22 2943

-

关于电路中旁路电容的滤波选取2012-08-01 3129

-

开关电源中选取滤波电容的三个主要参数2009-02-10 5132

-

电源滤波电容的选取和选择2008-07-14 26200

全部0条评论

快来发表一下你的评论吧 !