基于ASIC和VHDL语言实现成/解帧电路的设计

可编程逻辑

描述

来源:微计算机信息 作者:李鹏程,颜永红,帅金晓

在通信领域,采用数字化,能够大大提高传输的容量。模拟的话音信号经过脉冲编码调制,即PCM 处理(包括抽样、量化以及编码三个步骤)后,被变换为一个64Kbit/s 速率的数字信号。在北美,数字 复接设备将24 路话音信号即24 路64Kbit/s 速率的数字信号按字节交错复接成1.544Mbit/s 的高速率信号; 而在欧洲,将30 个独立64Kbit/s 信道与两个用于信息控制信道一起同步复接为一个32 个数字信道帧结 构,其帧重复频率是8000 帧/秒,复接后比特率是2.048Mbit/s。这就是所谓的E1 信号,它是数字通信的 基础,由E1 复接而成的各高次群形成的数字系列,称为准同步数字系列(PDH)。虽然同步数字系列 (SDH)正逐步取代PDH,但PDH 设备以低廉,灵活的特点仍然发挥着它的作用。

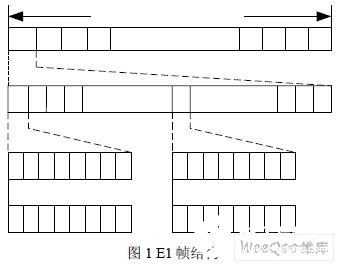

1.帧结构

符合G.704 标准的E1 帧结构如图1 所示,每基本帧由32 个路时隙(ts0“ts31)组成,分别分配给30 个话音数据流和相应辅助信息。每个路时隙由8bit 码组成,基本帧帧频为8K,而每16 基本帧(F0”F15) 构成一个复帧,故每个复帧共由4096 比特组成。

复帧结构中的ts1“ts15,ts17”ts31 分别用来传30 个64kbit/s 数字信息的数据时隙,而ts0 和ts16 用 来传各种辅助信号,下面分别介绍。

在一个复帧中,基本帧可以分为两类:奇帧和偶帧。奇帧和偶帧的区分是通过ts0 的第2bit 来区分的, 奇帧的bit2 为‘1’。偶帧ts0 时隙的bit2“bit8 是用来传基本帧对准信号FAS 的。G.704 协议规定帧对准信 号FAS 为“0011011”。整个复帧又可以看成由两个CRC-4 校验快构成,前8 个基本帧为第一校验块,根 据协议要求的方式对其进行CRC-4 校验,校验结果共4bit 放在偶帧(F0,F2,F4,F6)ts0 的bit1,同 理对后一校验块校验的结果放在偶帧(F8,F10,F12,F14)ts0 的bit1。同时奇帧的第3bitA1 为对告bit, A1 为‘1’时表示有告警,当收到lof 或者los 时,则将A1 置为‘1’。奇帧ts0 的第1bit 传复帧定位信号MFAS, 协议规定MFAS 为“001011”。可以看到复帧定位信号为6bit,而一个CRC 复帧中有8 个奇帧,所以协议 规定奇帧(F13,F15)ts0 的第1bit 用来传误块指示比特E0 和E1,当其为‘0’时表示有误块。还有奇帧的 第4 至第8bit 为备用bit,不用时应置为‘1’。

基本帧的ts16 用来传信令信号,既可以传共路信令,也可以传随路信令,同样当其传随路信令时每 16 基本帧的ts16 可构成16 字节的信令复帧。复帧的第一帧ts16 的前四个码位分配给复帧定位使用,其 定位码组是“0000”,第6bit 为复帧对告比特,无报警时固定为‘1’。复帧中第2”16 帧的ts16 作为30 个话 路的信令时隙,每路信令占4 个码位(a,b,c,d),在这里以4 比特为单位实现30 路信令的同步交错 复用,同时(a,b,c,d)不能为“0000”。但由于目前国内使用的是公共信令,所以一般使用的帧应该 是PCM31 即31 路话路,ts16 传也为数据,本设计也是针对这种帧结构。

2.系统设计

本系统包括e1_framer,e1_deframer,e1pi 三个模块,e1_framer 模块对待发送的数据组成符合G.704 协议规定的E1 帧结构;e1_deframer 模块对接收到的数据进行解帧,即对帧组成部分的进行分离并加以 解释;e1pi 模块负责将数据发送到线路侧同时从线路上接收数据,这其中包括对数据进行检测、从数据 中恢复出时钟(收方向)、进行码型的转换(hdb3 编解码)、对编码违例进行检查。

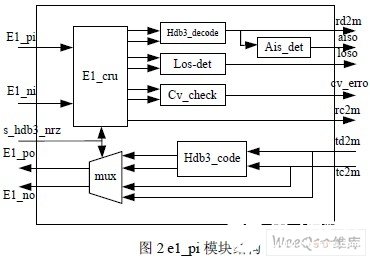

2.1 e1_pi 模块设计

E1_pi 模块从功能上来说需要处理收发两个方向的数据。e1_pi 模块结构如图2 所示,在收方向上: E1_cru 模块从输入信号中提取时钟完成定时功能;hdb3_decode 和cv_check 模块分别完成hdb3 的解码和 做编码违例检查;los_det 和ais_det 模块对输入信号进行检测,如果在两帧时间内(512bit)收到的‘0’的 个数少于或等于2,则给出全1(ais)告警,反之若收到的‘1’的个数少于或等于2 则给出信号丢失(los) 告警。在发方向则只需就待发信息做hdb3 编码然后发送到线路上。

E1_cru 模块是时钟恢复模块,设计思想是先用一个高速的时钟(本设计中为65MHz)去采样频率为 2.048 MHz 的E1 信号,得到数据的变化沿;再根据变化沿的位置,由高速时钟分频产生2.048 MHz 时钟。

HDB3码是一种AMI码的改进型,不仅克服了当AMI码中出现连“0” 码定时提取困难的缺点,而且具 有频谱能量主要集中在基波频率以下,占用频带较窄的优点。其编码原则可以简述为:(1) 当连“0” 码 的个数不大于3时, “1” 码变为“+1”、“-1” 交替脉冲;(2) 当代码序列中出现4个连“0” 码或超过4 个连“0”码时,把连“0” 段按4个“0” 分节,即“0000”,并使第4个“0” 码变为“1” 码,用V 脉冲(破坏脉冲) 表示,且V脉冲极性与其前一个“1” 脉冲极性相同;(3) 必须使相邻的破坏点之间有奇数个“1” 码。 如果原序列中破坏点之间的“1” 码为偶数,则必须补为奇数,即将破坏节中的第一个“0” 码变为“1”,用 B脉冲表示。B脉冲极性与其前一个“1” 脉冲极性相反。

假设 hdb3 数据线分别为hdb3p 和hdb3n,从hdb3 编码规则可以得出hdb3 编码违例的发生包括在以 下四种情况中:(1)hdb3p 和hdb3n 上同时出现‘1’;(2)将hdb3p 和hdb3n 或操作,得到合路数据,此 数据上出现4 连0 或者大于4 连0 的情况;(3)hdb3p 或者hdb3n 上出现连续‘1’的情况,即数据中出现 连续的正极性/负极性B 脉冲;(4)两次破坏点之间的B 脉冲个数不为奇数个;若检测到以上四种情况中 的一种,就会产生编码违例告警(cv)。

2.2 e1_framer 模块设计

该模块为成帧模块,根据G.704 帧结构标准,在每复帧不同的基本帧ts0 时隙插上开销比特(包括帧 同步码,复帧同步码和对告等),同时需要对整帧做crc-4 校验,crc-4 产生方法采用 x4 + x + 1 序列(10011), 把校验结果放在下一帧的相应位置上,然后依次将开销比特和数据发出。

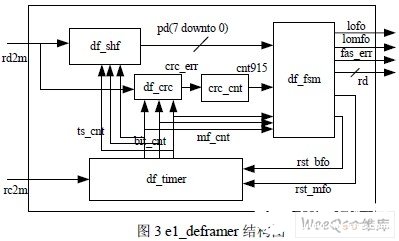

2.3 e1_deframer 模块设计

e1_deframer 模块结构如图3 所示,关于e1 帧的解帧,最重要的是做到基本帧和复帧的同步,只有同 步了才能依次取出各话路信息,另一方面就是如果检测到传输过程中出现了问题需要给出告警指示。 df_timer 是定时模块为其他模块提供时隙计数(ts_cnt),基本帧计数(bf_cnt),复帧计数(mf_cnt);df_shf 为移位寄存器,实现数据从串行输入到并行输出的作用;df_crc 模块完成crc_4 校验并比较结果,出错则 给出告警,crc_cnt 模块用来对crc 误块进行计数,这是判断lof 的条件之一。df_fsm 是核心模块主要做基 帧和复帧同步,然后产生告警。

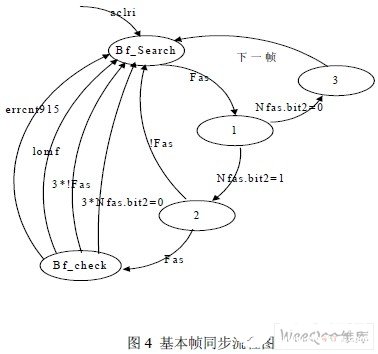

根据G.706 规定的帧同步算法,基本帧同步的过程如图4 所示,系统复位即进入基本帧搜索状态, 当收到正确的帧定位信号(FAS=“0011011”)后进入状态1;在状态1 检测下一帧ts0 的bit2,看是否为1, 如果为1 则进入状态2 反之则进入状态3 后回到搜索态;在状态2 时检查下一帧是否包含正确的FAS, 如果正确则进入同步态,反之回到搜索态。

在基本帧同步的情况下如若出现以下情况,则会出现帧失步,状态机恢复到搜索态:(1)检测到三 个偶帧连续的错误FAS;(2)奇帧ts0 的bit2 出现三个连续的错误;(3)出现复帧丢失(lomf);(4)在 1s 内,即1000 个CRC-4 块中出现大于等于915 个误块。在帧失步状态后自动回到基本帧搜索状态,并给 出lof 告警、向下插AIS、发对告A=‘1’、停止CRC-4 性能监视。

对于复帧同步采用的算法是:在8ms 时间(4 个CRC 复帧)内至少出现2 次复帧同步信号“001011” (由奇帧ts0 第1 比特构成),则认定复帧已经同步;而在复帧已同步的情况下连续4 帧没有找到正确的 MFAS 则认为复帧已经失步,需重新定位。复帧失步需给出lomf 告警。另外对于传随路信令的帧结构还 存在ts16 复帧同步问题,由于国内不常采用,在此就不赘述。

3.仿真验证

本设计采用VHDL 语言进行了RTL 级的描述,用modelsim 对设计进行了仿真,经过FPGA 验证后, 各功能都得到正确地实现,最后采用FUJITSU 的CS86MN 工艺得到ASIC 实现。

下图给出了系统部分RTL 级仿真波形。 仿真系统采用的是E1 环回模式,即从E1 接口出来的hdb3 信号又给到接口的输入,从图a 中可以反映 出发送前的nrz 信号跟接收后解码出来的nrz 信号是一样的,只是时间上有些延迟,由此证明编解码模块是 正确的。 图b 反映的是E1 解帧模块中基本帧同步的过程,从图中可以看到基本帧的同步经历了找到FAS,下一 帧为奇帧,再一帧又找到FAS,这样三个步骤,这也是符合G.706 标准的。

4.结论

本文描述了E1 帧的基本结构,详细介绍了E1 基本帧和CRC 复帧同步的算法,采用VHDL语言对符 合G.704 和G.706 标准的成/解帧电路进行了RTL 描述,并最终得到ASIC实现。实验证明,该系统的时钟 恢复模块能达到通信的指标,HDB3 编解码模块能有效进行编解码工作,并能正确检测到线路上编码违例的情况,各项告警均符合标准的要求,具有很强的实用价值。同时该电路设计相对于以往的设计来说具有面 积小的特点,在保证质量的前提下节约了成本。

本文作者创新点:1.充分利用了标准中规定的预留比特形成了新的CRC 复帧结构,有利于在通信中发现错误; 2.对编解码模块进行了优化设计,达到缩小芯片面积的目的。

责任编辑:gt

-

基于VHDL语言实现远程防盗报警设计2023-11-08 586

-

如何利用FPGA和VHDL语言实现PCM码的解调?2021-05-07 1379

-

如何利用VHDL语言实现FPGA与单片机的串口异步通信电路?2021-04-29 696

-

如何用VHDL语言实现帧同步的设计?2021-04-08 1401

-

基于VHDL硬件描述语言实现CPSK调制的程序及仿真2021-01-19 940

-

使用Quartus和VHDL语言实现的LPC时序的工程文件2020-09-18 1177

-

FM收音机的解码及控制器VHDL语言实现2016-06-07 981

-

VHDL语言实现的帧同步算法2010-07-02 2336

-

用VHDL语言实现3分频电路(占空比为2比1)2009-06-22 9063

-

vhdl语言实例大全下载2008-05-20 84337

-

用VHDL语言实现3分频电路2007-08-21 6325

全部0条评论

快来发表一下你的评论吧 !