FPGA程序设计:如何封装AXI_SLAVE接口IP

电子说

1.4w人已加入

描述

在FPGA程序设计的很多情形都会使用到AXI接口总线,以PCIe的XDMA应用为例,XDMA有两个AXI接口,分别是AXI4 Master类型接口和AXI-Lite Master类型接口,可通过M_AXI接口对数据进行读取操作,此时设计一个基于AXI-Slave接口的IP进行数据传输操作就非常的方便。

封装的形式并不复杂,只是略微繁琐,接下来一步一步演示如何封装AXI_SLAVE接口IP:

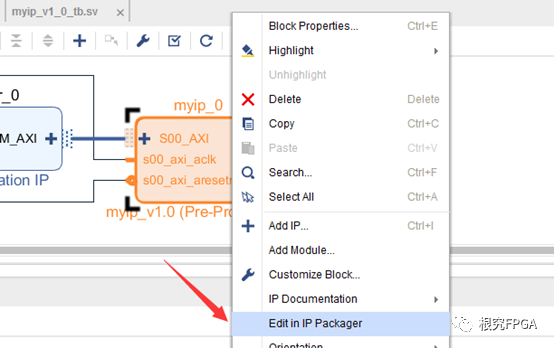

1、创建工程

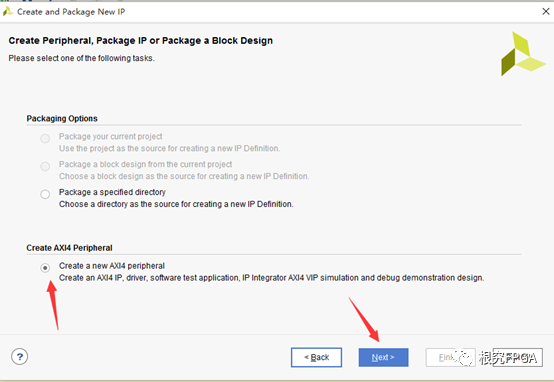

2、选择Create AXI4 Perpheral,点击next

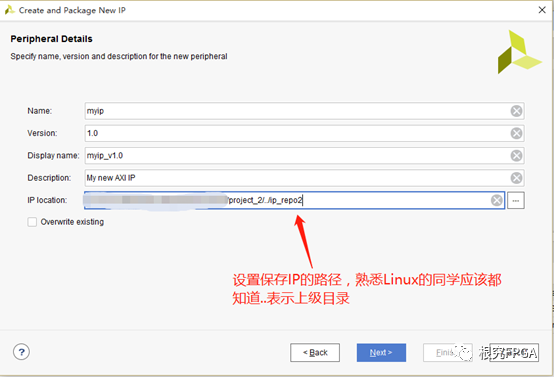

设置保存路径,也可默认:

3、设置保存路径:

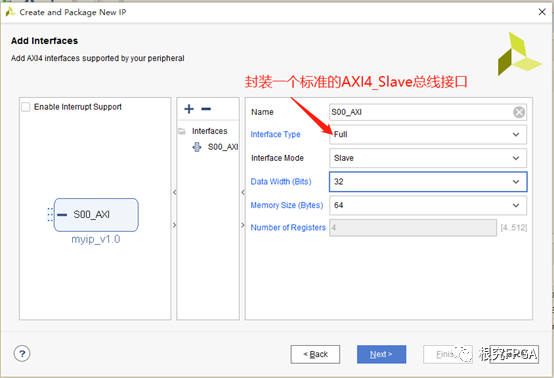

4、设置封装的接口类型:

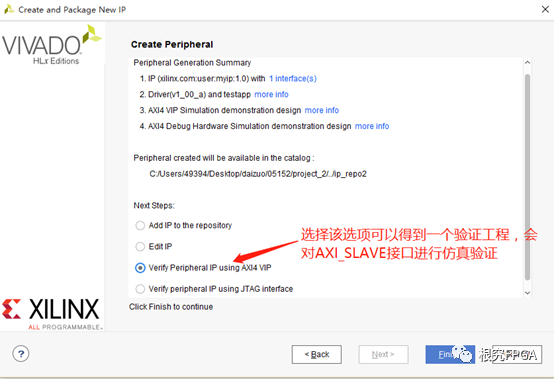

5、选择Verify Peripheral IP using AXI4 IP

6、对IP进行修改:

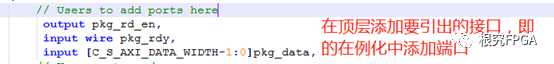

在顶层和总线文件中添加自定义的端口和信号:

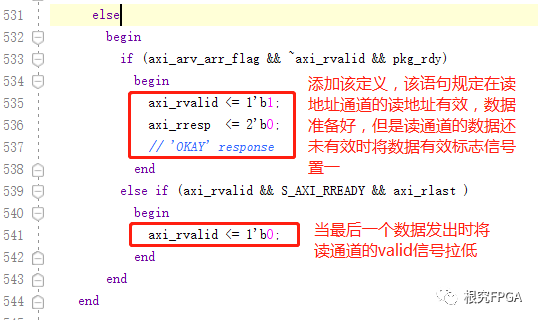

在S00_AXI.v中编辑:

7、保存工程

如果不慎将初始的IP封装界面关掉的话,在Tools下选择Create and Package New IP,选择Package your current project,NEXT之后选择open(你会看到的)。

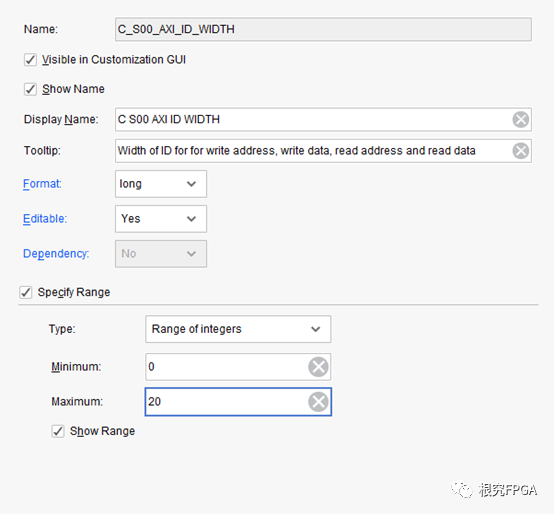

设置ID位宽,该选项主要用于outstanding传输:

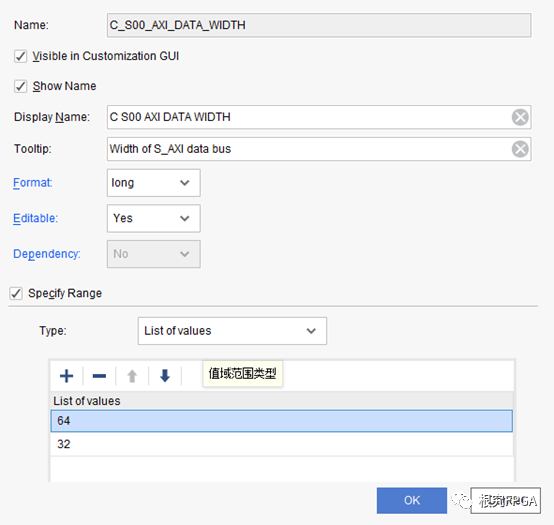

设置数据位宽,根据需要自行设计:

如果出现Merge提示的话,点击,选择覆盖参数。

最后选择重新封装IP,就得到属于自己的AXI_SLAVE接口IP啦!

在刚刚设置的ip_repo2文件目录下可以看到IP:

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

如何用zedboard创建一个AXI接口应用程序?2020-08-12 1612

-

看看在SpinalHDL中AXI4总线互联IP的设计2022-08-02 3302

-

AXI接口简介_AXI IP核的创建流程及读写逻辑分析2018-06-29 18010

-

自定义sobel滤波IP核,IP接口遵守AXI Stream协议2019-08-06 4797

-

ARM+FPGA开发:基于AXI总线的GPIO IP创建2020-12-25 7010

-

AHB Slave Decoder和AHB Slave Interface接口的使用说明2020-11-11 2774

-

AXI 总线交互分为 Master / Slave 两端2022-02-08 18669

-

全面介绍ZYNQ-AXI互联IP2021-05-11 8183

-

AXI_GP接口和AXI_HP接口的相关内容2022-07-03 5239

-

使用AXI VIP的几个关键步骤及常见功能2022-10-08 7829

-

FPGA AXI4协议学习笔记(二)2023-05-24 3040

-

AXI VIP当作master时如何使用?2023-07-27 3430

-

基于Xilinx FPGA AXI-EMC IP的EMIF通信测试2023-08-31 12718

-

XILINX FPGA IP之AXI Traffic Generator2023-11-23 5645

-

使用AXI4接口IP核进行DDR读写测试2025-11-24 3935

全部0条评论

快来发表一下你的评论吧 !