CH340G设计的一键下载电路原理解析

电子说

描述

在做基于STM32的多功能MP3播放器的课题时,在程序下载这部分时借鉴了正点原子开发板上的一键下载电路,采用CH340G这款芯片设计。

在画PCB初期原理图部分,对采用CH340G设计的一键下载电路不甚了解,于是花了一些时间来研究一下这个电路。

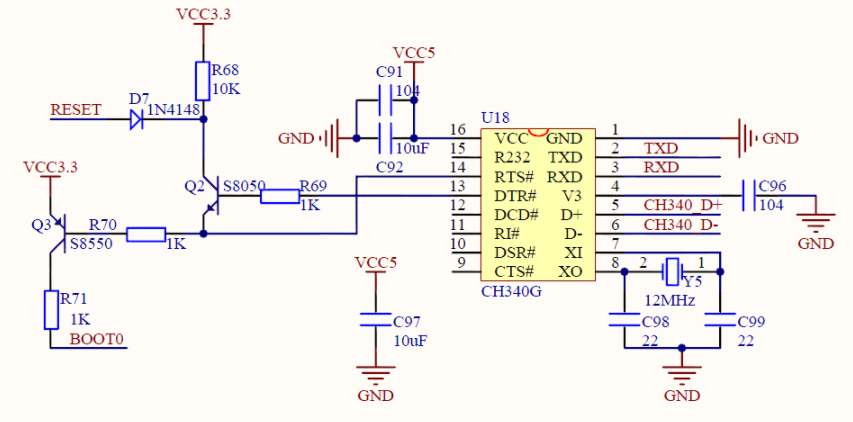

引用正点原子的一键下载电路:

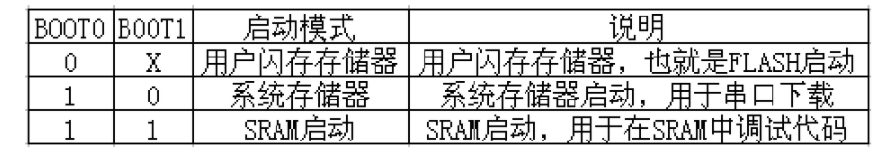

我们通过RTS#和DTR#两个输出信号来控制STM32 IC的BOOT0和BOOT1两引脚来选择启动模式,如下表:

当烧写程序时,我们希望BOOT0=1,BOOT1=0。当烧写完成后我们希望BOOT0=0,BOOT1=0(这个模式BOOT1可以是0可以是1,这里我们让BOOT1拉低,即整个过程BOOT1都为L接地,简化电路设计)。

这里我们只需考虑BOOT0的高低。

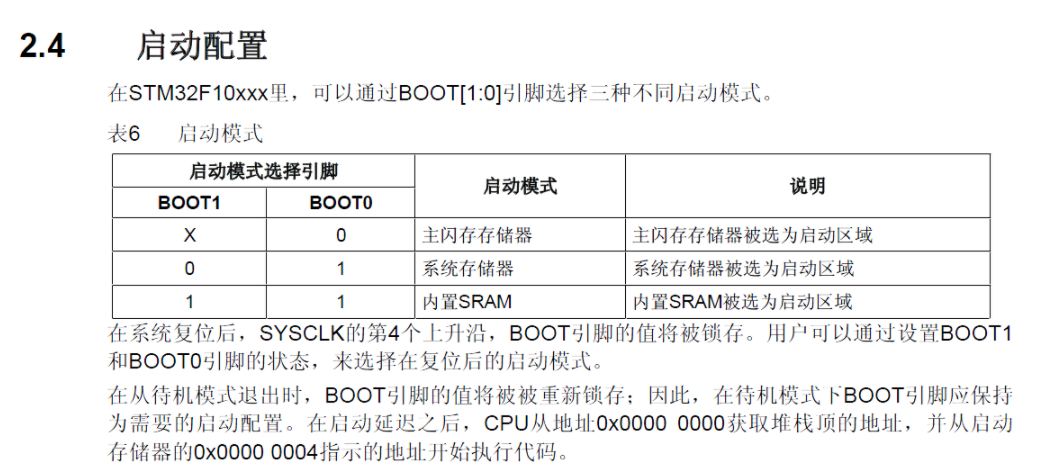

查看STM32的参考手册,如下图:

注意表6下方第一句话:“在系统复位后,SYSCLK的第4个上升沿,BOOT引脚的值将被锁存。”

OK,综上所诉,我们可以得到: 1、系统上电,BOOT0需为L,进入模式一。上电复位后,在SYSCLK的第4个上升沿,BOOT引脚的值将被锁存,进入主闪存存储器,执行我们烧写的代码。

2、当我们编译好程序,生成HEX文件。在烧写HEX文件时,BOOT0需为H,进入模式二。然后,系统必须复位一次(因为由1知道,系统上电后默认执行代码,即模式一),让系统重新锁存BOOT引脚。系统进入模式二,开始烧写HEX文件。

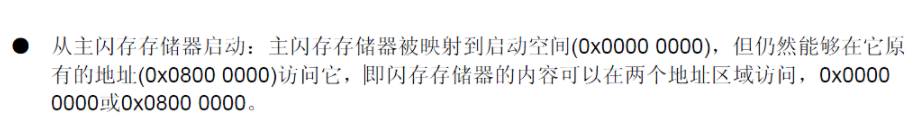

3、烧写完成后,我们希望系统再次进入模式一,执行代码。但正点原子的一键下载电路并没有让系统完成烧写程序后再次复位重新锁存BOOT引脚进入模式一。这个原因应该是MCUISP软件帮我们配置好了,在烧写完成后会有报告:“成功从08000000开始运行”。

在参考手册中有这样一段话:

从另一个方向来理解它,可以这么说:主闪存存储器从地址(0x0800 0000)访问,不管是系统自动的还是软件配置的,只要系统指针跳到主闪存存储器的地址(0x0800 0000)处开始执行代码,就可以了,结果是我们想要的。

以上就是一键下载电路需要实现的功能,原子兄帮我们设计出来了。如果看不懂的话,可以参考我下面的解释。

我们需要注意一点:CH340G上电后DTR#和RTS#都为高电平,在用MCUISP烧写软件时,我们在软件下方选择“DTR的低电平复位,RTS高电平进BootLoader”,CH340G IC在实际操作时引脚的变化为“DTR#拉高,RTS#拉低”,即软件设置和实际情况是取非的,相反的。

画个时序图,直观一些:

编辑:hfy

-

经典CH340G驱动2025-04-09 274

-

ch340g无法识别的usb设备2024-01-05 7045

-

CH340G转换芯片模块jf_72064266 2022-11-21

-

带有CH340G的Arduino Mega Rev.32022-08-04 1114

-

ch340g下载电路测试小慕 2022-07-22

-

求助,请问ch32f103c8t6可不可以与ch340g实现串口一键下载?2022-05-30 830

-

CH340G中文资料-数据手册-参数2022-03-21 2874

-

如何利用CH340G芯片去设计一键下载电路呢2021-12-06 2870

-

USB转串口电路之CH340G解析2020-12-25 4929

-

ch340g下载电路2018-01-11 23740

-

stm32的ISP一键下载问题2017-03-02 5426

-

CH340G模块原理图2016-03-30 6353

-

ch340g的原理图2015-12-08 6067

全部0条评论

快来发表一下你的评论吧 !