数字下变频概念及matlab实验结果

模拟技术

描述

1.数字下变频介绍

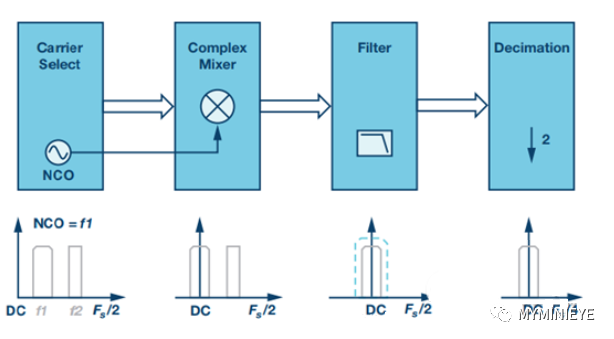

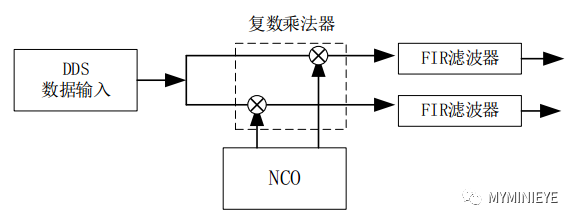

数字下变频是一种广泛应用于数字无线电接收机的数字信号处理技术,其主要目的是经过数字混频将A/D转换输出的中频信号搬移至基带,然后通过滤波,抽取完成信道提取的任务,如下所示:

主要的电路模块由四部分组成:数控震荡、数字混频、数字滤波、采样抽取。

2.matlab结果

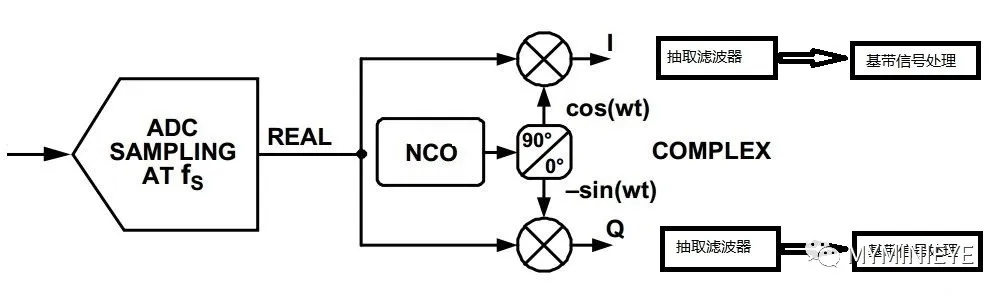

(1)首先使用matlab对整个过程进行验证,输入信号中频f0 =4.5MHz;采样频率fs=40/3*f0;采样时间为1us,输入信号和NCO输出相乘,得到I、Q两路信号,分别对输入信号和NCO相乘结果做FFT,点数为256点,点数的选择不是固定的,可以参考之前介绍FFT的文章,其信号以及频谱如下:

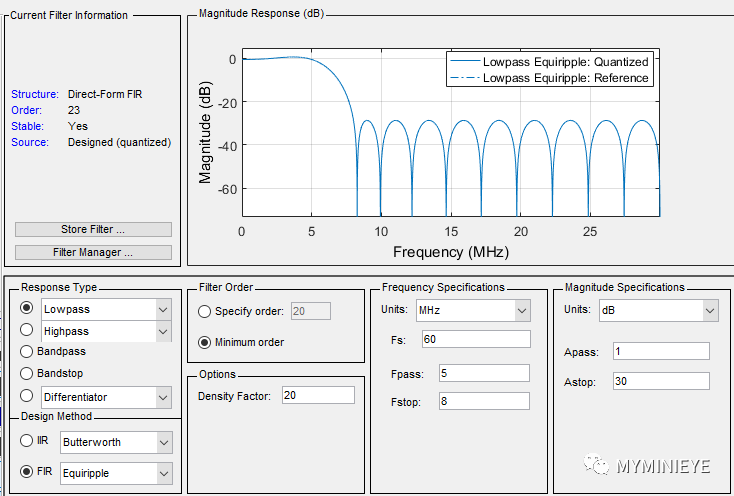

(2)如上图所示,滤波器的作用就是滤除-8.9MHz的频率,滤波器设计采用matlab的Filter Design,FIR滤波器设计也可以参考之前的文章,设计滤波器如下:

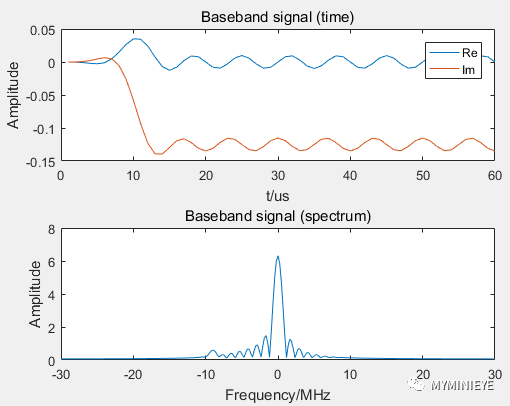

(3)由于采样率比较低,这里就不做抽取,最后信号的频谱如下所示:

3.FPGA实现

我们使用DDS代替信号输入,然后通过复数乘法器和NCO输出相乘,滤波器的系数直接导入matlab生成的系数即可:

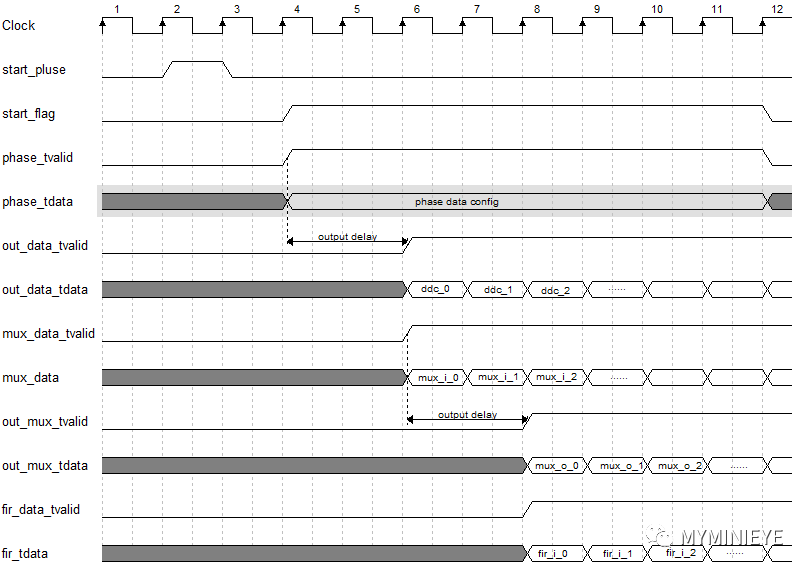

针对以上系统结构,每次触发采集1us的数据,NCO和DDS的数据同时产生,由phase_tvalid控制,mux_data包括两路信号,如上图所示,复数乘法器的输出分为两路做滤波,具体时序设计如下:

最后实际结果和matlab数据进行比对,数据比对的时候要注意位宽量化的问题:

(1) vivadoIP核没有提供复数乘法器的matlab仿真模型,可以直接使用点乘来代替,但是要量化之后才能把数据输入滤波器,不然的话,后续数据比对就会出现问题

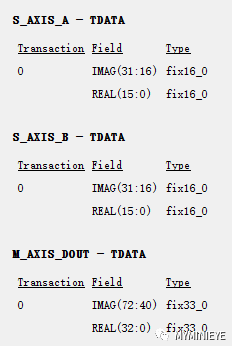

DDS和NCO的输出分别是16位的数据,由复数乘法器的输入和输出端口的结构可以知道

如果不进行输出截位,输出为33位,我们这里设置输出为16位,也就是截取高16位,在matlab里可以这样做,截掉低17位。

s_fix = s_in.*s_nco

floor(s_fix/2^17)

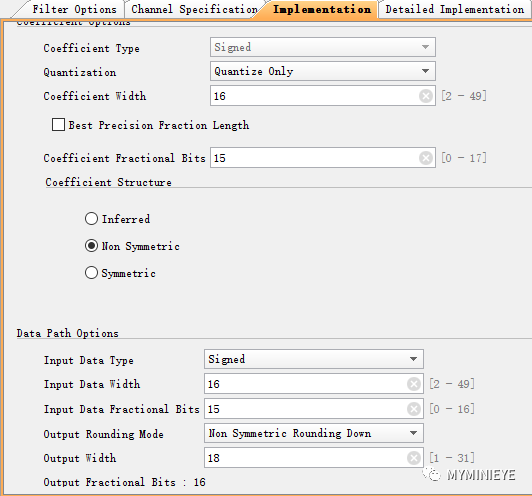

其中输出舍入方式要与IP核中的一致。

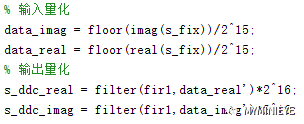

(2) 滤波器输出要注意,输入的数据是fix16_15,我们设置输出为18位,输出的数据是fix18_16

对输入和输出做如下量化:

按照上述操作,matlab输出的数据和FPGA的输出是一致的。

-

基于FPGA的超宽带数字下变频设计2014-02-22 4654

-

雷达系统中数字下变频的实现2025-08-30 1542

-

【设计进展】数字下变频模块2012-06-06 4019

-

基于fgpa的数字正交下变频2014-04-01 4806

-

数字下变频2017-02-15 4795

-

数字下变频的FPGA实现2009-11-30 1027

-

基于新型FPGA实现高速数字下变频2010-07-02 613

-

基于FPGA的DDC数字下变频设计2016-04-27 1030

-

myddc数字下变频程序2017-08-30 1289

-

基于FPGA的数字下变频器的设计与实现2017-11-22 7085

-

重新思考快速宽频ADC中的数字下变频.pdf2018-04-23 709

-

基于FPGA的DDC(数字下变频)设计与实现2021-09-15 1003

-

基于FPGA的数字下变频器(DDC)的设计2021-09-16 1558

-

基于MATLAB雷达信号采集及处理技术研究2022-04-14 933

-

数字下变频器是怎么回事2023-01-05 4890

全部0条评论

快来发表一下你的评论吧 !