何谓 AXI?关于AXI3/AXI4的相关基础知识

电子说

描述

引言

近来,几乎每个赛灵思 IP 都使用 AXI 接口。Zynq®、Zynq MP、MicroBlaze™ 和全新的 Versal™ 处理器都无一例外使用 AXI 接口。因此,AXI 接口已成为几乎所有新的赛灵思器件设计中不可或缺的一部分。充分了解其基础知识对于赛灵思器件的设计和调试都很有帮助。

本篇博文将介绍赛灵思器件上的 AXI3/AXI4 的相关基础知识。首先,我们将从一些通俗易懂的知识、理论和术语开始讲解。

何谓 AXI?

AXI 表示 Advanced eXtensible Interface(高级可扩展接口),它是由 Arm 定义的接口协议,包含在“高级微控制器总线架构 AMBA”标准中。

AXI3/AXI4 规格可通过 Arm 网站免费获取(链接),因此如果您对其感兴趣,我鼓励您务必下载。

AXI4 接口 (AMBA 4.0) 分 3 种类型:

AXI4 (AXI4-Full):用于满足高性能存储器映射需求。

AXI4-Lite:用于简单的低吞吐量存储器映射通信(例如,往来于状态寄存器的通信)。

AXI4-Stream:用于高速流传输数据。

注:本文不涵盖 AXI4-Stream 相关内容。此处“AXI”表示 AXI3、AXI4 和 AXI4-Lite。

注:AXI3 接口与 Full AXI 接口接近。

AXI 读写通道

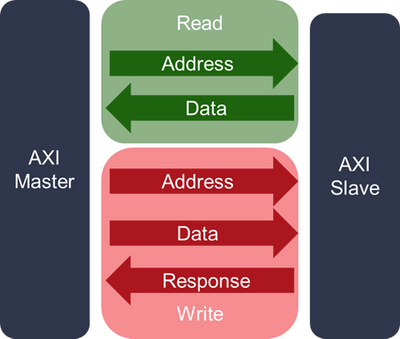

AXI 协议定义了 5 条通道:

其中 2 条用于读取传输事务

读地址

读数据

另 3 条用于写入传输事务

写地址

写数据

写响应

通道 (channel) 是与 VALID 和 READY 信号关联的 AXI 信号的独立集合。

注:AXI4/AXI3/AXI4-Lite 接口只能用于读取(仅包含 2 条读取通道)或者只能用于写入(仅包含 3 条写入通道)。

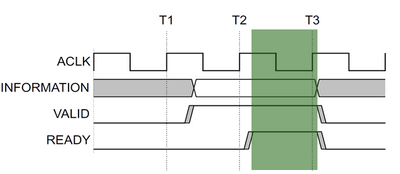

任一通道上发射的每一条数据都称为一次传输 (transfer)。当 VALID 和 READY 信号均居高不下并且时钟存在上升沿时,就会发生传输。例如,在下图中,在 T3 处正在发生传输:

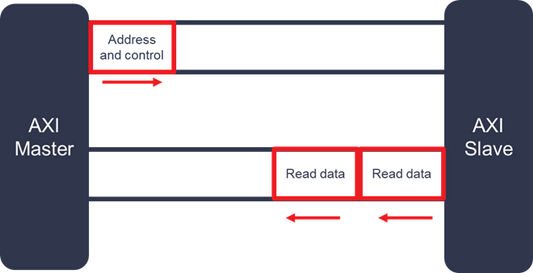

AXI 读取传输事务

AXI 读传输事务需要在 2 条读取信道上发生多次传输。

首先,地址读通道 (Address Read Channel) 从主设备 (Master) 发送到从设备 (Slave),以便设置地址和部分控制信号。

然后,此地址的数据通过读数据通道 (Read data channel) 从从设备发送到主设备。

请注意,根据下图所示,每个地址中可发生多次数据传输。此类型的传输事务称为突发 (burst)。

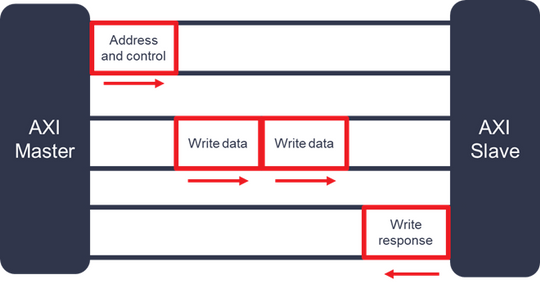

AXI 写入传输事务

AXI 写入传输事务需要在 3 条读取信道上存在多次传输。

首先,写地址通道 (Address Write Channel) 从主设备发送到从设备,以便设置地址和部分控制信号。

然后,此地址的数据通过写数据通道 (Write data channel) 从主设备发射到从设备。

最后,写入响应通过写响应通道 (Write Response Channel) 从从设备发送到主设备,以指示传输是否成功。

写响应通道 (Write Response Channel) 上可能的响应值包括:

OKAY (0b00):正常访问成功。表示已成功完成正常访问

EXOKAY (0b01):专属访问成功。

SLVERR (0b10):从设备错误。已成功访问从设备,但从设备希望向发端主设备返回错误条件(例如,数据读取无效)。

DECERR (0b11):解码器错误。通常由互连组件生成,用于指示传输事务地址处没有任何从设备

注:读取传输事务同样包含响应值,但此响应通过读响应通道 (Read Response Channel) 来发射

AXI4 接口要求

在 AXI4 规格中记录了部分要求。

最值得注意的是:

断言 VALID (AxVALID/xVALID) 信号时,它必须保持处于已断言状态直至从设备发出 AxREADY/xREADY 断言后出现上升时钟沿为止。

发送信息的 AXI 接口的 VALID 信号不得从属于接收该信息的 AXI 接口的 READY 信号。

但是,READY 信号的状态可从属于 VALID 信号

写响应必须始终位于所属的写入传输事务中最后一次写入传输之后

读数据必须始终位于数据相关的地址之后

从设备必须等待发出 ARVALID 和 ARREADY 断言后,才能发出 RVALID 断言以指示该有效数据可用

-

AXI接口FIFO简介2025-03-17 2361

-

SoC设计中总线协议AXI4与AXI3的主要区别详解2024-05-10 14036

-

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】2023-06-21 3260

-

FPGA AXI4协议学习笔记(二)2023-05-24 3049

-

AXI4协议五个不同通道的握手机制2023-05-08 2291

-

AXI3与AXI4写响应的依赖区别2023-03-30 2086

-

看看在SpinalHDL中AXI4总线互联IP的设计2022-08-02 3302

-

AXI VIP设计示例 AXI接口传输分析2022-07-08 3120

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 10952

-

关于AXI4-Stream协议总结分享2022-06-23 3358

-

深入AXI4总线一握手机制2021-03-17 1276

-

ZYNQ中DMA与AXI4总线2020-11-02 5321

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 7572

-

AXI4接口协议的基础知识2020-09-23 7255

全部0条评论

快来发表一下你的评论吧 !