Video Frame Buffer IP初学者入门案例分析

电子说

描述

Video Frame Buffer IP 简介

Video Frame Buffer Read/Write IP 支持您将视频数据从存储器域(AXI4 存储器映射接口)迁移到 AXI4-Stream 接口,或反之亦然。

从更高层次来看,它的作用与我们在先前视频系列(视频系列 24、视频系列 25、视频系列 26 等)中所使用过的 AXI VDMA IP 并无差异。

那么为什么要使用 Video Frame Buffer IP 核而不是 AXI VDMA IP 呢?

答案就记录在(赛灵思答复记录 72543)中。究其本质,AXI VDMA IP 从 AXI4-Stream 接口提取字节,并直接将其移植到存储器中,无关乎视频数据格式。

Video Frame Buffer 必须关注传入传出存储器的数据格式。根据所选格式,它能以不同方式将数据存储在存储器中。这对于 Linux 应用非常实用。

比如,V4L2 格式 YUYV 和 UYVY 都表示 YUV4:2:2 8 位,唯一差别就在于两者在存储器中的存储方式。

因此,建议针对新设计采用 Video Frame Buffer IP。

如需了解有关 Video Frame Buffer Read/Write IP 的详情,请参阅 (PG278)。

为 Video Frame Buffer IP 生成设计示例

注意:下文是基于 2019.2 版本中提供的设计示例编写的。

硬件 (Vivado 2019.2) 设计示例

要生成应用设计示例的硬件部分 (Vivado Design),请遵循 (PG278) 的第 5 章中的步骤进行操作。此处设计示例可用于 KC705、ZCU102、ZCU104 和 ZCU106 评估板。即使您没有上述任意评估板,我也建议从设计示例开始实践。这始终都是最佳的起点。

注意:要利用 Vivado WebPack 许可证生成设计示例,请使用 ZCU104 评估板作为起点开始操作。

设计示例分为两种。一种用于 Video Frame Buffer Read IP,另一种用于 Video Frame Buffer Write IP。

我建议使用面向 Video Frame Buffer Write IP 的设计示例,因为 Video Frame Buffer Write IP 和 Video Frame Buffer Read IP 都囊括在其中。

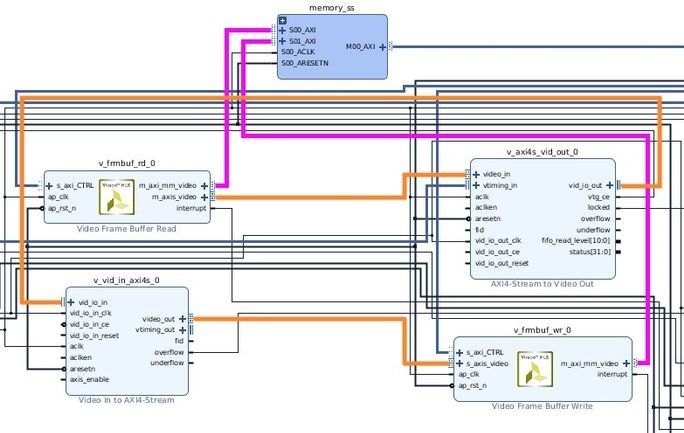

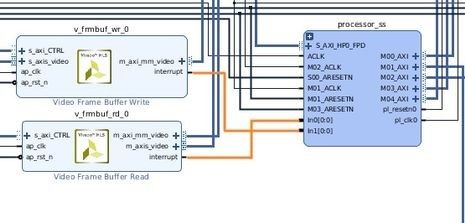

Video Frame Buffer Write IP 设计示例的硬件设计属于非常基础性的设计。

它使用 Video Frame Buffer Read IP 将数据从存储器读取到 AXI4-Stream 接口。

随后,将其转换为本地视频,然后再使用 AXI4-Stream to Video Out IP 和 Video in to AXI4-Stream IP 重新转换为 AXI4-Stream。

最后使用 Video Frame Buffer Write IP 将 AXI4-Stream 数据重新写入存储器。

我认为对于此设计,有两个值得注意的要点:

1. 上述两个 Video Frame Buffer IP(Read 和 Write)各自的中断输出都连接到处理器。这是前提条件。Video Frame Buffer 是基于中断的 IP。

2. 而这两个 Video Frame Buffer IP 的复位输入则连接至 AXI GPIO IP。这一点至关重要,因为它支持您从处理器执行 IP 软复位。就像所有 HLS IP 一样,只要分辨率改变,就需要将 Video Frame Buffer 复位。

应用示例 (Vitis 2019.2)

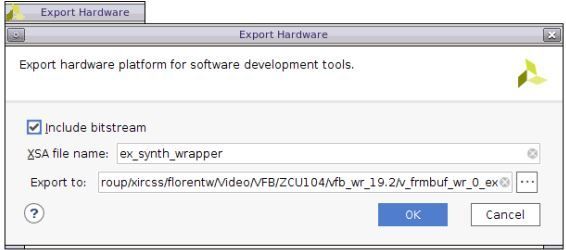

要生成应用示例,在 Vivado 中,首先将硬件导出至赛灵思 Vitis(依次单击 File > Export > Export Hardware …)。

确保在导出的硬件中包含比特流。这将创建一个 XSA 文件。

启动赛灵思 Vitis 并选择要用作为工作空间的目录。

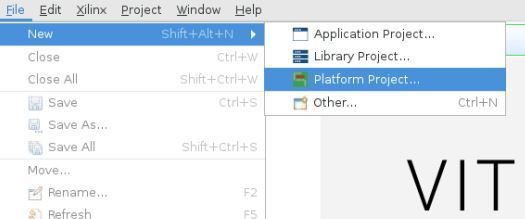

在 Vitis 中,单击 New > Platform project。

输入您所选的平台名称(例如,v_frmbuf_zcu104_pfm),然后单击 Next。

确保选中 Create from hardware specification (XSA),然后单击 Next。

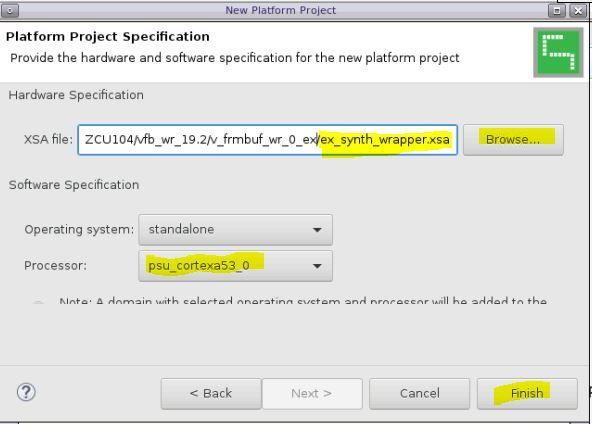

选择从 Vivado 导出的 XSA 文件,确保已选中 A53 处理器,然后单击 Finish。

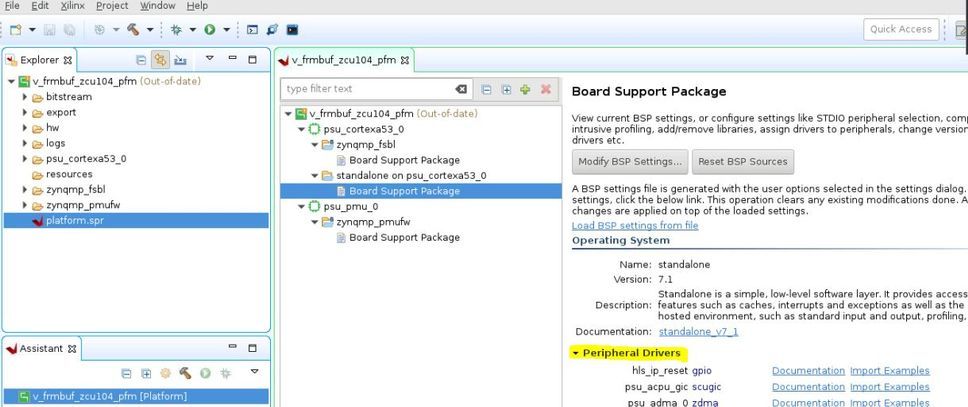

创建平台后,单击 psu_cortexa53_0 > standalone on psu_cortexa53_0 下的 Board Support Package,然后展开 Peripheral Drivers 部分。

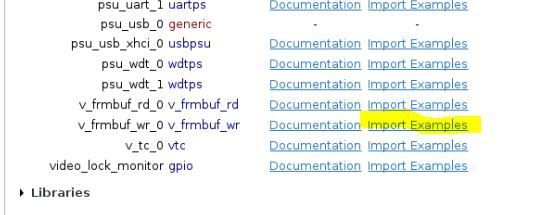

在 Peripheral Drivers 下,查找对应于 Video Frame Buffer Write (v_frmbuf_wr) 的行,然后单击 Import Examples。

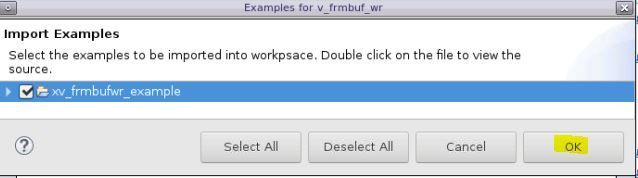

选择示例 (xv_frmbufwr_example),然后单击 OK。

运行应用示例

注意:以下步骤假定评估板已上电并且已通过 UART 连接,BOOT 模式开关已设置为 JTAG 模式和 JTAG,并且已打开 UART 终端(如 Tera Term)供正确的 COM 端口使用。

单击应用并单击锤子图标以构建应用:

要在硬件上启动应用示例,请右键单击设计应用示例,并单击 Run As > Run Configurations…

在 Create, manage, and run configurations 窗口中,右键单击 Single Application Debug,然后单击 New Configuration。

在配置窗口的 Target Setup 选项卡中,确保已启用 psu_init(如果在 ZCU102、ZCU104 或 ZCU106 评估板上运行)和 Program FPGA,然后单击 Run。

在 UART 终端中,可以看到此应用正在尝试不同的视频分辨率和色彩空间组合。

在应用运行结束时,可能会显示部分测试失败的原因(主要原因是硬件配置不支持)。

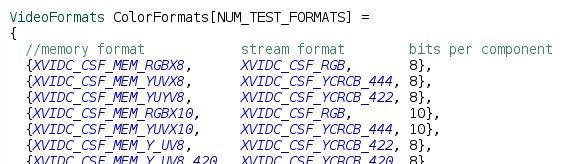

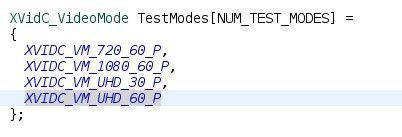

色彩空间和视频分辨率在应用中以 ColorFormats 和 TestModes 结构来定义。

编辑:hfy

-

面向CAN总线初学者的入门教程2023-10-20 946

-

Gowin Video Frame Buffer IP快速用户指南2022-10-10 677

-

Gowin Video Frame Buffer with PSRAM IP用户指南2022-09-16 624

-

初学者AVR软件入门基础知识(2)2018-07-04 3222

-

linux初学者入门2017-10-27 1099

-

PSOC1初学者5个实验,针对初学者的实验2017-10-16 1305

-

初学者密码学简单入门2017-09-21 1221

-

从51初学者到电子工程师2016-02-23 1060

-

CAN入门书_CAN总线初学者入门书2015-12-17 2214

-

初学者之路—硬件学习经验2011-12-29 14784

-

初学者USB技术入门总结2009-04-22 977

全部0条评论

快来发表一下你的评论吧 !