HDMI VCU118设计移植到VCU128开发板的步骤解析

电子说

描述

简介与视频示例设计概览

许多视频 IP 核都附带有示例设计。这些设计用于 IP 演示,并提供示例以供您在自己的设计中使用 IP 核时作为参考。

这些 IP 示例设计的介绍请参阅 IP《产品指南》第 5 章。

在IP主页上,Document Navigator 或视频设计中心内可找到《产品指南》。

HDMI VCU118 示例设计简介

赛灵思 HDMI IP 核分为两种:源端 (Source) IP 核 (HDMI 1.4/2.0 TX Subsystem) 和 Sink IP 核 (HDMI 1.4/2.0 RX Subsystem)。

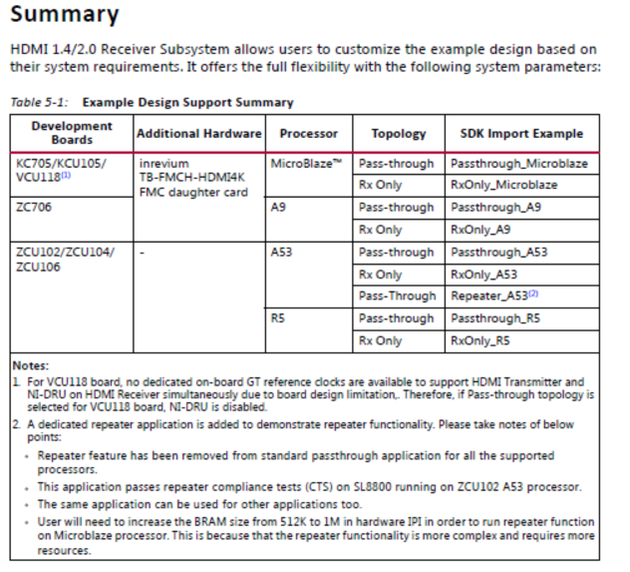

这些 IP 核的介绍请参阅 (PG235) 和 (PG236)。《产品指南》第 5 章中包含HDMI 1.4/2.0 示例设计的表格。

通过该表可以看到,其中包含 VCU118 示例设计,但不含 VCU128 示例设计。

注意:如该表所示,传递模式下无 DRU 时钟可用,因为并无任何振荡器引脚信号输出至 HDMI 核附近 bank 中的 gtrefclk。

教程

以下是我将 HDMI VCU118 设计移植到 VCU128 开发板时所使用的步骤。这些步骤仅作为示例以供参考,并非唯一方法。

1. 移植设计的第一步是确保已构建新硬件平台用于为设计提供支持。

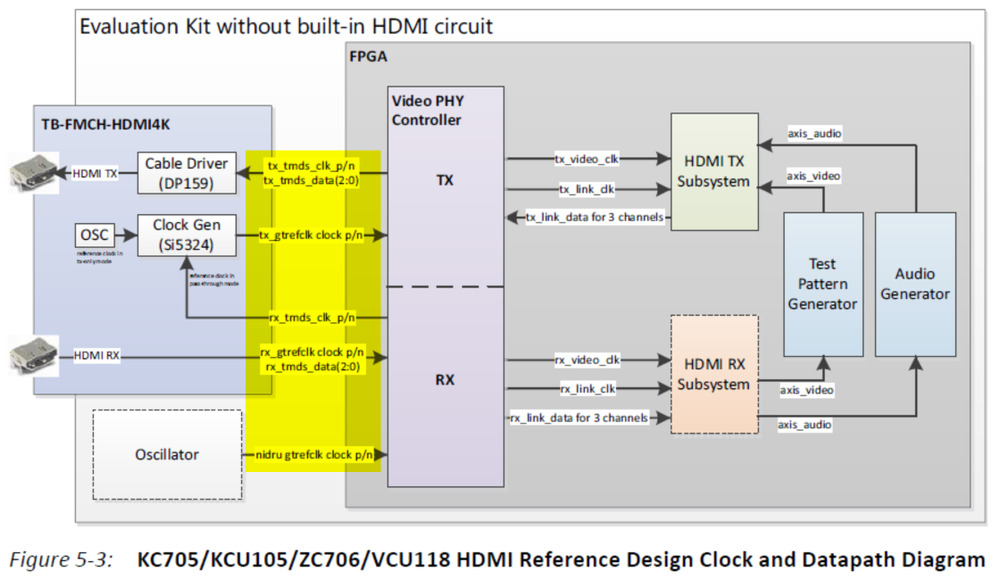

最好首先罗列出 HDMI 设计要求。通过使用《产品指南》中的图 5-3 并聚焦高亮的 I/O,设计要求一目了然。

注意:VCU118 与 VCU128 开发板都不具有 nidru gtrefclk。

设计要求列表:

TMDS 时钟引脚信号已输出至 FMC

已通过 3 个 GT 引脚将发射器数据引脚信号输出至 FMC

发射器参考时钟引脚信号已从 FMC 输入

接收器参考时钟引脚信号已输出至 FMC

接收器参考时钟引脚信号已从 FMC 输入

已通过 3 个 GT 引脚将接收器数据引脚信号输出至 FMC

**请核实周围各 bank 以确认是否存在可编程 NI-DRU 时钟源

2. 已知设计要求情况下即可检查 VCU128 以确认是否已满足这些要求。

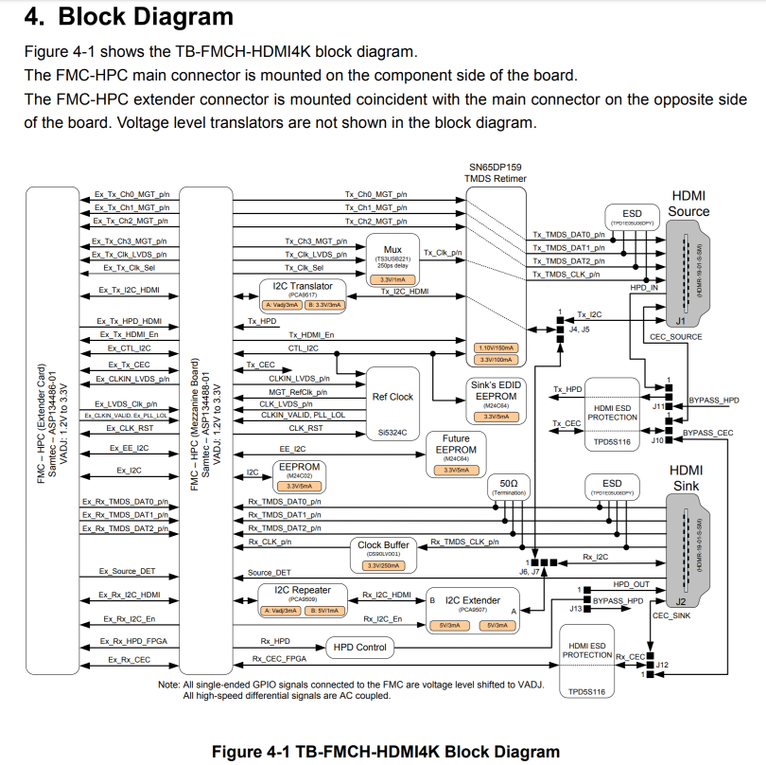

为此,我们可以查阅 VCU128 原理图、VCU128 开发板用户指南以及wikipinout.xml 并对比FMC 文档(如下图所示)

通过使用上述文档即可将列表转换为引脚名称。

M2C -> 夹层卡到载卡(FMC -> 开发板)

C2M -> 载卡到夹层卡(开发板 -> FMC)

TMDS 时钟引脚信号已输出至 FMC -> LA27_P

已通过 3 个 GT 引脚将发射器数据引脚信号输出至 FMC -> DP0_C2M_P 至 DP2_C2M_P

发射器参考时钟引脚信号已从 FMC 输入 -> GBTCLK1_M2C_P

接收器参考时钟引脚信号已输出至 FMC -> LA00_CC_P

接收器参考时钟引脚信号已从 FMC 输入 -> GBTCLK0_M2C_P

已通过 3 个 GT 引脚将接收器数据引脚信号输出至 FMC -> DP0_M2C_P 至 DP2_M2C_P

**请核实周围各 bank 以确认是否存在可编程 NI-DRU 时钟源

bank124 周围无可用时钟

通过查看设计可以发现,在图 5-3 中并未显示全部引脚。

Si5324 RST

FMC_IIC_SCL

FMC_IIC_SDA

rs232_uart_rxd ->UART0_RXD

rs232_uart_txd ->UART0_TXD

reset -> CPU_Reset

RX_DDC_OUT_scl_io ->LA16_P

RX_DDC_OUT_sda_io ->LA16_N

TX_DDC_OUT_scl_io->29_P

TX_DDC_OUT_sda_io->29_N

TX_EN_OUT ->LA26_P

TX_CLK_SEL_FPGA -> LA18_CC_P

用于选择是否使用第 4 个 GT 或 LVDS 引脚作为 HDMI TMDS 时钟。

RX_HPD_OUT -> LA20_N

RX_I2C_EN_N_OUT -> LA22_P

RX_DET_IN -> LA03_P

SI5324_LOL_IN ->LA02_N

TX_HPD_IN -> LA31_N

3. 鉴于已知 I/O 引脚存在并且已正常连接到 FMC,下一步即可构建 VCU118 示例设计。

注意:该过程的介绍请参阅《产品指南》第 5 章。

4. 完成设计构建后,需要更新所有 VCU118 特定参数。这样在更改部件号时,连接将保持断开状态。

在此设计中,MMCM 是直接以 VCU118 为目标的唯一 IP。

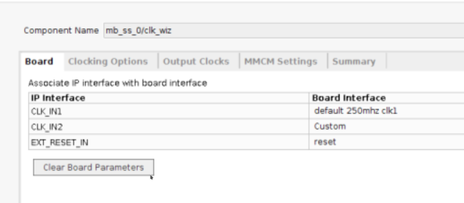

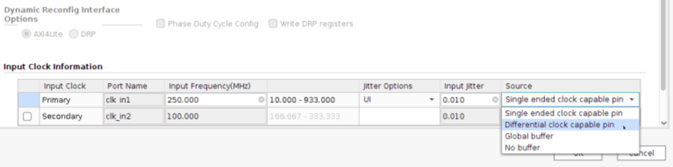

4.1. 打开 mb_ss_0 块并打开时钟向导 (clk_wiz)。

4.2. 单击“Clear board parameters”以清空开发板参数。这将删除 VCU 特定参数。

4.3. 将“Source”更新为“Differential clock capable pin”,然后保存块设计

5. 设置新项目目标 -> VCU128 (XCVU37P-L2FSVH2892E)

6. 将 IP 更新到新项目

打开 IP 集成器、选择报告 IP 状态,然后升级所有 IP。

验证其中不存在任何错误。

注意:不保证这对所有设计或移植都有效。如果此步骤无效,请使用先前的设计作为示例并手动构建新项目.

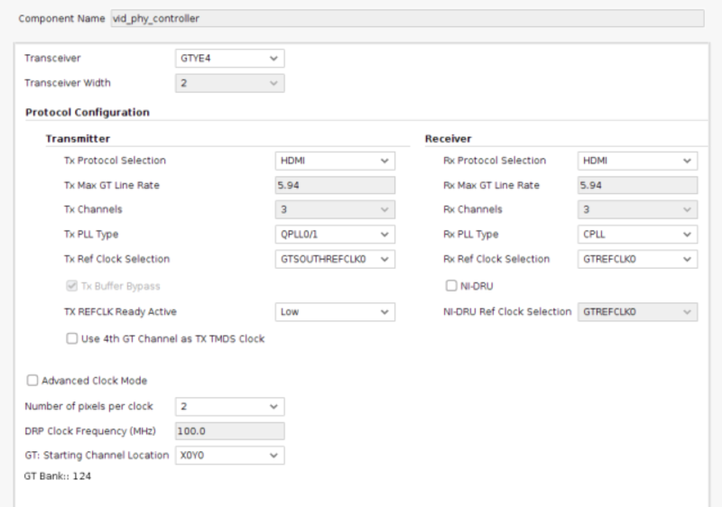

7. 鉴于当前项目目标为 VCU128 并且 IP 已升级,我们需要编辑 VPHY,设置正确的 bank 目标并使用正确的时钟。

通过 VCU128 文档可知,所使用的 GT 位于 bank 124 中。Bank 124 为 X0Y0。

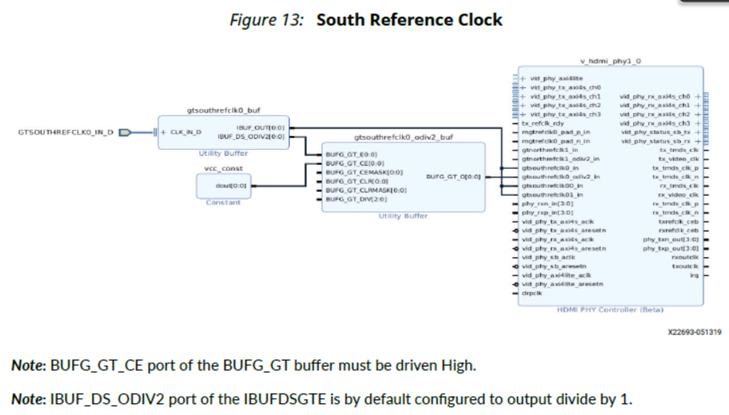

由于 GT 位于 bank 124 中,但当前使用的 TX reference0 时钟来自 bank 125,因此需要将参考时钟设置为 southrefclk0。

由于当前使用的是 North/South refclk,因此需根据 (PG230) 《Vivado PHY 控制器产品指南》中所述更新管脚。

8. 请核实连接状态,确保所有引脚均已连接,然后验证设计并运行综合。

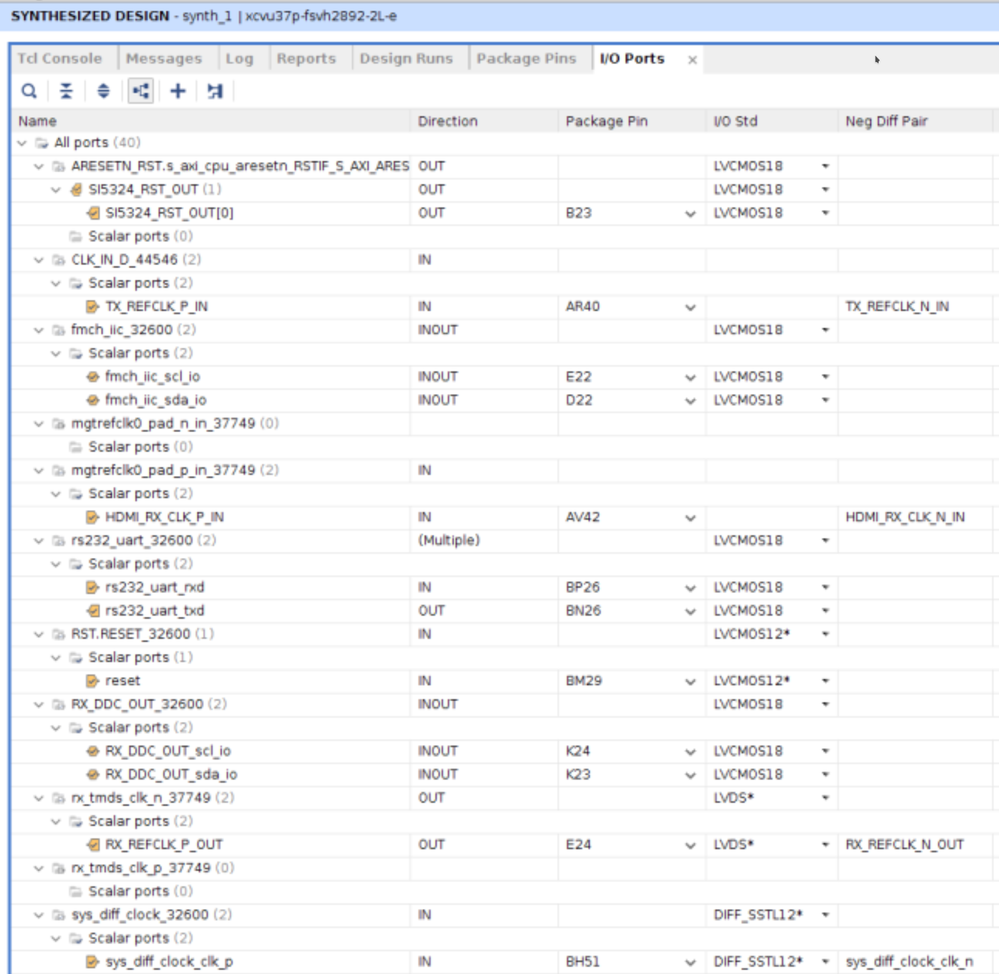

9. 完成综合后,即可更新约束。

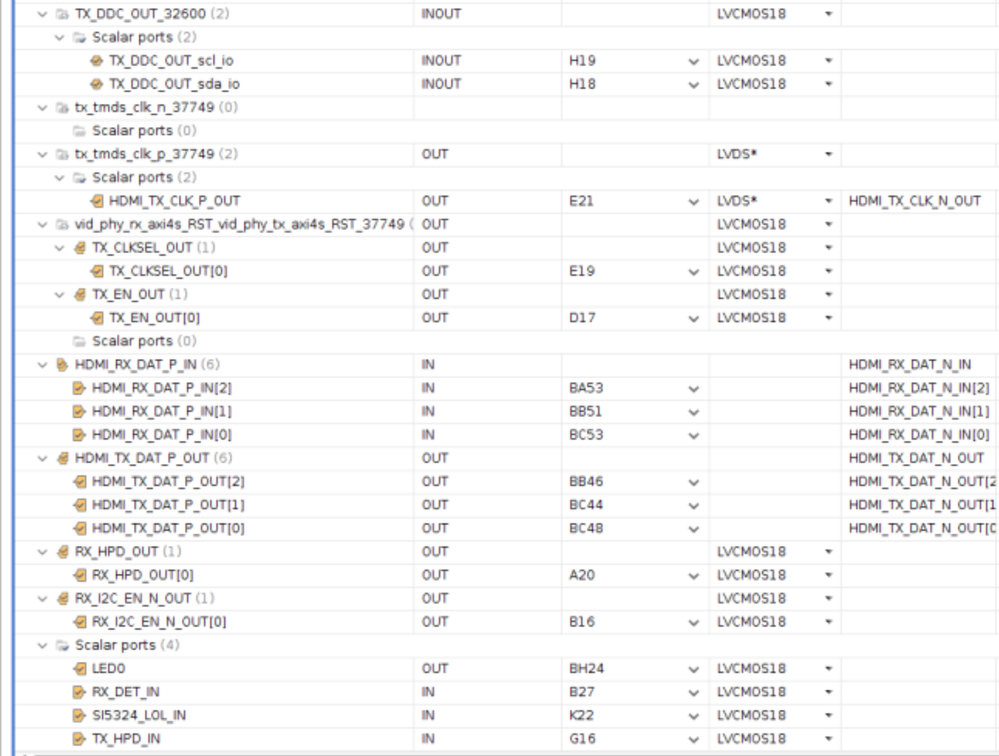

打开 Synthesized Design,依次单击“layout -> I/O planning”。

在此视图中,选择 I/O 端口,然后使用新管脚对其进行更新。(GT TX/RX 引脚将已填充完成)

完成操作后,请保存以便更新约束文件 (.xdc)。

10. 约束更新完成后,请运行实现并生成比特流。

11. 导出硬件用于 SDK。

单击“File -> Export Hardware

12. 最后,针对 VCU118 使用相同流程来构建应用示例设计。

打开 SDK

新建 BSP (File -> New SDK)

单击 MSS 标签,选中 HDMI 1.4/2.0 RX Subsystem 驱动程序,然后单击“Import Examples”。

在打开的标签中,单击“Passthrough MicroBlaze”。

这将生成软件项目。对其执行构建,这样即可创建 ELF。

13. 大功告成!在硬件中执行测试以验证移植的示例设计是否正常运行

编辑:hfy

-

S32K376 BMU与VCU集成方案:硬件、软件与调试全解析2025-12-24 726

-

VCU129评估板用户指南2023-09-13 574

-

AMD Xilinx MPSoC VCU使用要点2023-07-10 1720

-

EK-U1-VCU118-G 开发板的具体详情2021-12-22 2710

-

VCU(整车控制器)简介2021-08-31 5462

-

整车VCU技术和开发流程剖析VCU2021-08-27 2205

-

Vivado无法识别VCU118 JTAG的原因?2020-06-09 3240

-

VCU108 SATA PHY:3个板中有2个时钟不稳定2020-04-20 2546

-

vcu118评估板FPGA无法配置2019-10-21 6401

-

请问我可以在VCU118上使用相同的子卡吗?2019-10-14 1341

-

如何获取和添加vcu118板信息到工具?2019-10-10 3774

-

如何修改VCU118板包以使此端口可用?2019-10-09 3967

-

MPU6050传感器如何从战舰开发板移植到miniV3板详细步骤说明2019-09-05 1641

-

VCU信号的类型和VCU信号的应用2018-05-24 15010

全部0条评论

快来发表一下你的评论吧 !