FPGA逻辑中关于地址映射说明

电子说

描述

背景与问题

• CPU+FPGA架构,CPU做RC、FPGA做EP;

• FPGA逻辑(Vivado ->BD -> Address Editor)中如何设置PCIe to AXI Translation;

• FPGA逻辑中如何设置AXI to PCIe Address Translation。

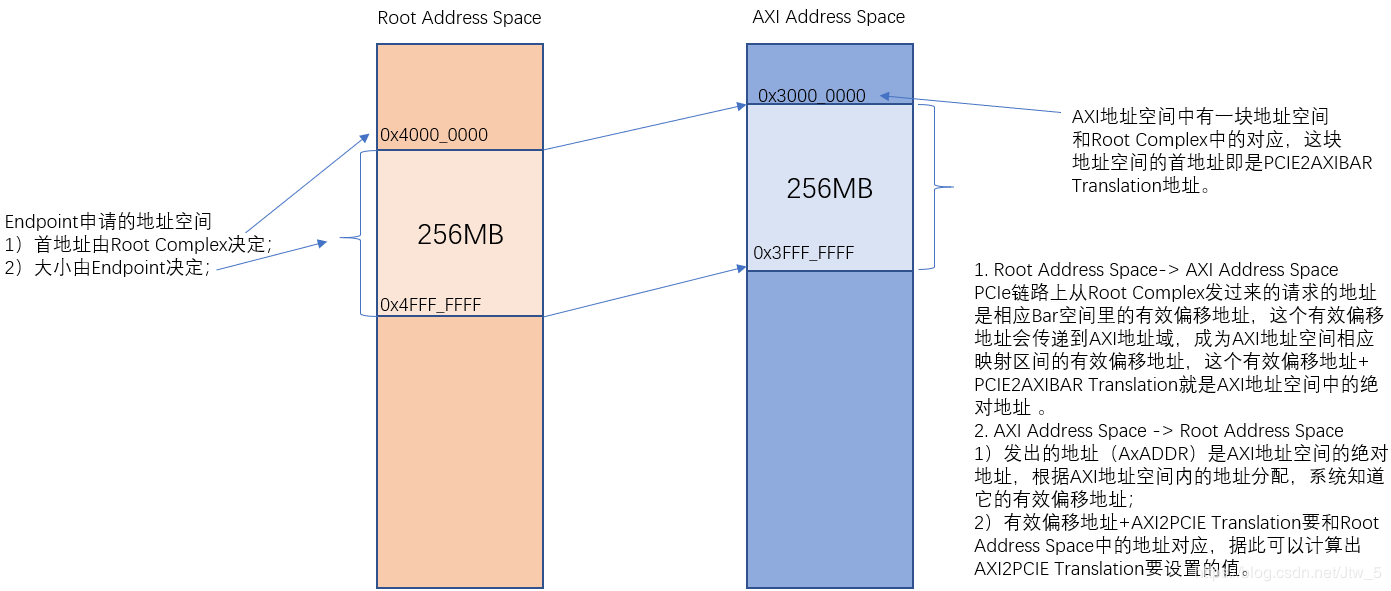

1. Root Complex到Endpiont

1.1 Root Complex到Endpiont,即PCIe域(Root Complex中的系统地址空间)到AXI域(FPGA逻辑中的AXI地址空间)。PCIe发起的对Endpoint的访问应在Endpoint申请的BAR空间内,Endpoint申请BAR空间时申明了地址空间的大小(比如256M,而且我们假设这256M空间对应AXI域中0x3000_0000~0x3FFF_FFFF),而Root Complex则根据实际情况决定从某个地址开始分配一段地址空间给Endpoint(比如0x4000_0000~0x4FFF_FFFF)。

1.2 PCIe想对Endpoint中的0x3000_0010地址发起一次访问。PCIe发出访问的地址为0x4000_0010,FPGA的PCIe Core会收到相应BAR空间中的有效地址偏移0x10,PCIe Core使用有效地址偏移+ C_PCIEBAR2AXIBAR(根据1.1中的假设,这个值为0x3000_0000)作为其AXI总线访问的地址。

2. Endpiont到Root Complex

2.1 假设PCIe域和AXI域的映射跟1. Root Complex到Endpiont的设定相同。

2.2 来自映射地址为0x3000_0000~0x3FFF_FFFF的AX总线访问给出的地址0x3000_1234会被PCIe Core剥离出有效偏移地址0x1234,使用该偏移地址+C_AXIBAR2PCIEBAR作为PCIe TLP的地址发送给Root Complex。C_AXIBAR2PCIEBAR的值应该设为Root Complex给Endpoint分配的地址空间的首地址,即0x4000_0000。

3. 总结与疑问

3.1 总结

• 地址空间的有效偏移地址。

• 地址空间的首地址。

3.2 疑问

CPU发出的访问地址到FPGA的PCIe IP是如何被提取出有效偏移地址的? PCIe的配置空间里记录了CPU分配的BAR空间的首地址?

-

操作系统中的逻辑地址和物理地址2022-09-14 5132

-

Matlab算法映射至FPGA硬件逻辑2023-01-30 3080

-

Linux内核地址映射模型与Linux内核高端内存详解2018-05-08 3853

-

关于ARM地址映射的理解2016-12-08 6369

-

hyperlink地址映射方式不对2018-12-28 3105

-

C6678逻辑地址重映射问题2021-04-24 1476

-

地址映射和寄存器映射原理分别是什么2022-03-02 1311

-

ARM启动代码及地址映射2010-02-11 525

-

STM32核心在Cortex的地址映射说明2017-11-29 850

-

FPGA视频教程之FPGA设计中时序逻辑设计要点的详细资料说明2019-03-27 1549

-

可编程逻辑阵列fpga和cpld说明2021-03-30 1215

-

2020.4.14 第四次 寄存器地址名称映射2021-12-08 690

-

FPGA中关于SPI的使用2023-04-12 1688

-

STM32/CPU地址映射的概念2023-07-24 2097

-

Vivado中DDRX控制器(mig)ip核配置中关于命令序号选择和地址映射说明2024-11-27 5981

全部0条评论

快来发表一下你的评论吧 !