三种种创建ROM的方法解析

电子说

1.4w人已加入

描述

ROM是只读型存储器,写入数据之后就不能在对数据进行更改。下面提供3种创建ROM的方法:

一、自己动手通过readmemh或readmemb函数来将自己写的文件与ROM进行关联;有几点需要注意的地方:寄存器rom的大小(位宽和深度)如下面的代码中位宽为8,深度为1024

// An highlighted block

module myrom(

clk,

addr,

q

);

input clk;

input [9:0] addr;

output reg[9:0] q;

reg [7:0] rom [1023:0];

initial begin

$readmemh("./xxx.txt",rom,0,1023);

//读16进制的数据

//格式$readmemh("file_name",memory_name[,start_addr[,finish_addr]]);

//file_name:文件名;memory_name:ROM名;start_addr:开始地址;finish_addr:结束地址

//[]的内容为可选内容,

//readmemb 读2进制的数据

end

always(posedge clk)

q<=rom[addr];

endmodule

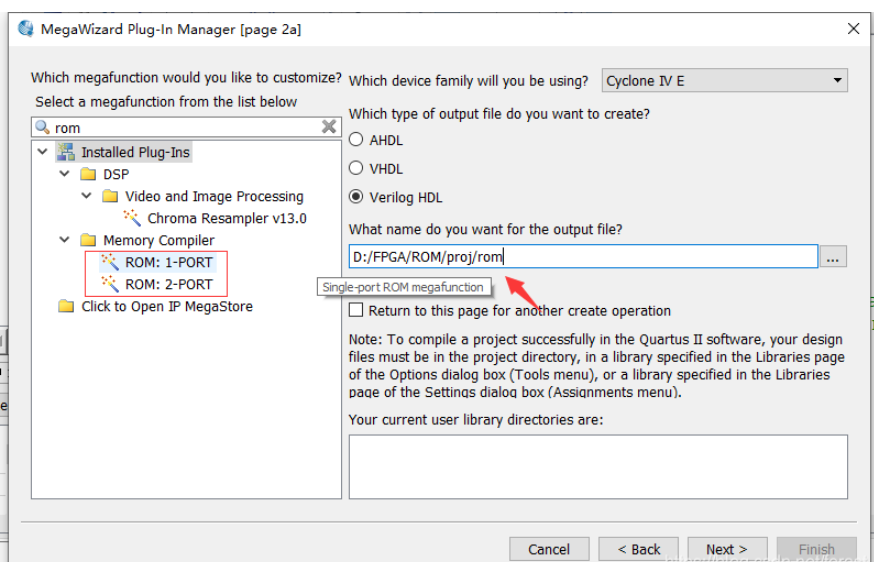

二、第二中方法是通过ip核创建rom。选择菜单栏中的Tools下的ip核配置工具,搜索rom,选着Verilog语言,并命名文件。点击下一步

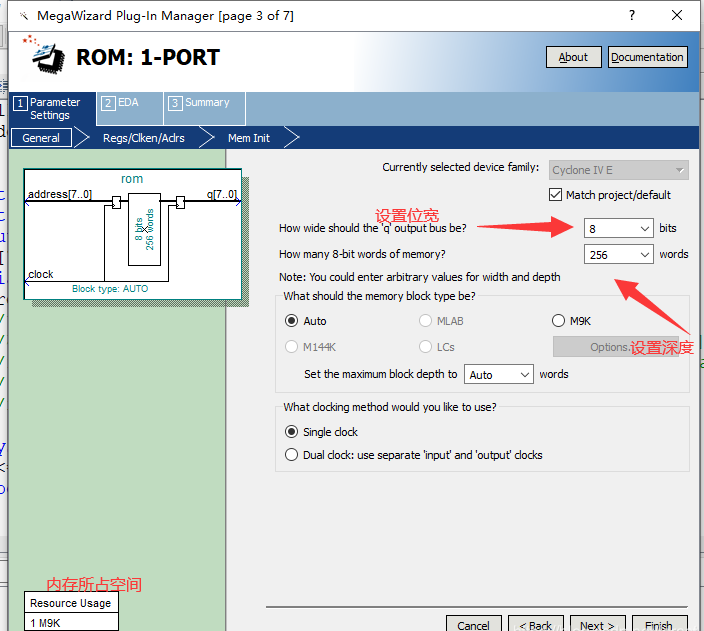

可以看到,在配置工具中依然需要设置位宽和深度。

在mem init中的文件名,这里需要注意的是文件必须是.mif和.hex文件。

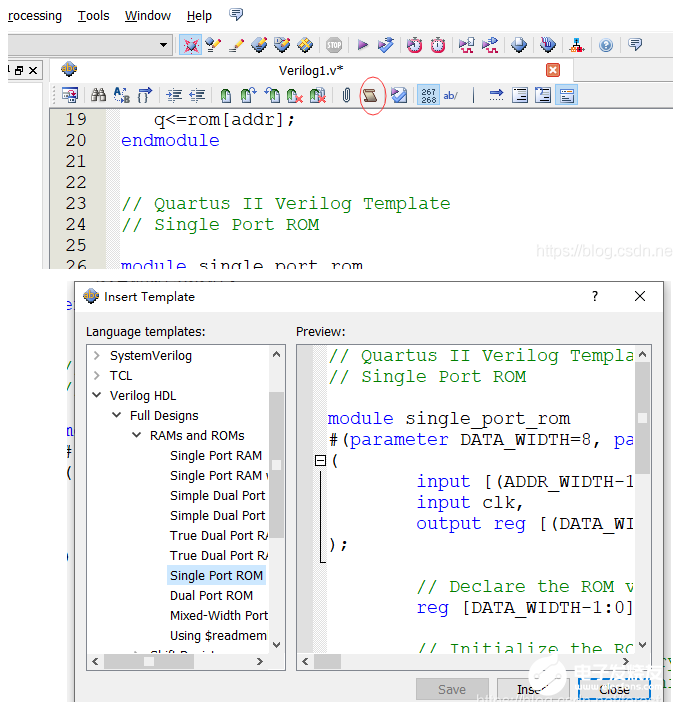

三、第三中方法是直接生成代码,在代码段上进行修改。

生成的代码段如下:这里需要修改的是两个参数DATA_WIDTH、ADDR_WIDTH。然后将对应的文件名修改了就可以了。

// Quartus II Verilog Template

// Single Port ROM

module single_port_rom

#(parameter DATA_WIDTH=8, parameter ADDR_WIDTH=8)

(

input [(ADDR_WIDTH-1):0] addr,

input clk,

output reg [(DATA_WIDTH-1):0] q

);

// Declare the ROM variable

reg [DATA_WIDTH-1:0] rom[2**ADDR_WIDTH-1:0];

// Initialize the ROM with $readmemb. Put the memory contents

// in the file single_port_rom_init.txt. Without this file,

// this design will not compile.

// See Verilog LRM 1364-2001 Section 17.2.8 for details on the

// format of this file, or see the "Using $readmemb and $readmemh"

// template later in this section.

initial

begin

$readmemb("single_port_rom_init.txt", rom);

end

always @ (posedge clk)

begin

q <= rom[addr];

end

endmodule

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

异步电机主要的三种调速方法解析2024-01-07 4561

-

继电保护的三种状态解析2023-09-27 4702

-

记录一下MCU存在ROM中的bootloader的三种方法2022-02-14 899

-

如何使用三种方式进行文件的创建2021-12-15 1499

-

直接进入TIVA系列MCU存在ROM中的bootloader的三种方法(转载)2021-12-09 771

-

三种IGBT驱动电路和保护方法2021-09-17 3592

-

python统计词频的三种方法2021-05-25 1182

-

启动Redis的三种方法2020-06-08 2573

-

用示波器快速捕获异常的三种方法2019-01-04 7045

-

铁损耗曲线的三种拟合方法比较2017-01-02 706

-

光电耦合器的三种检测方法2012-05-22 1099

-

三种不同的“防 Ping”技巧2010-04-14 1355

-

解决电池问题有三种方法2009-11-10 1174

-

噪声系数测量的三种方法2006-05-07 2470

全部0条评论

快来发表一下你的评论吧 !