ZYNQ进阶:PL端实现串口UART的接收设计

电子说

1.4w人已加入

描述

在ZYNQ进阶之路3中我们讲解了PL端UART 发送的设计,本节我们讲解PL端实现串口UART的接收设计;

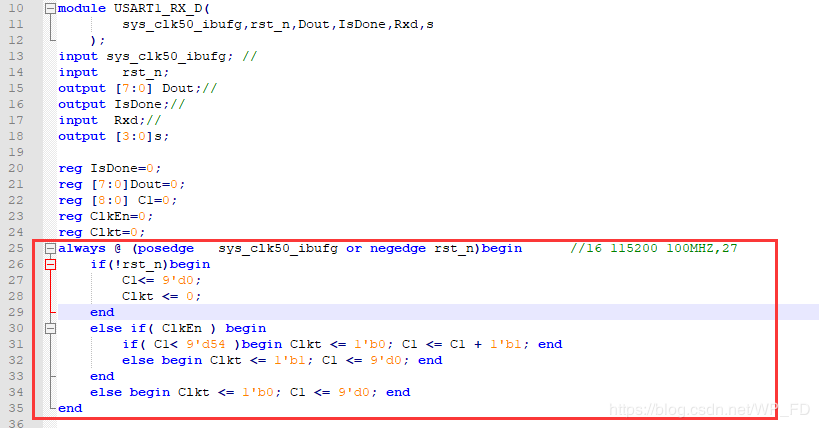

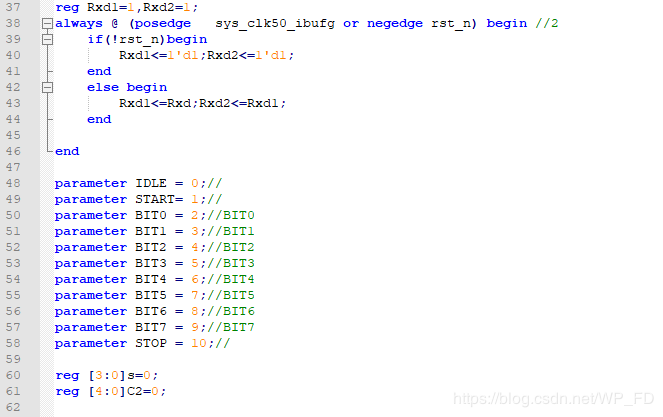

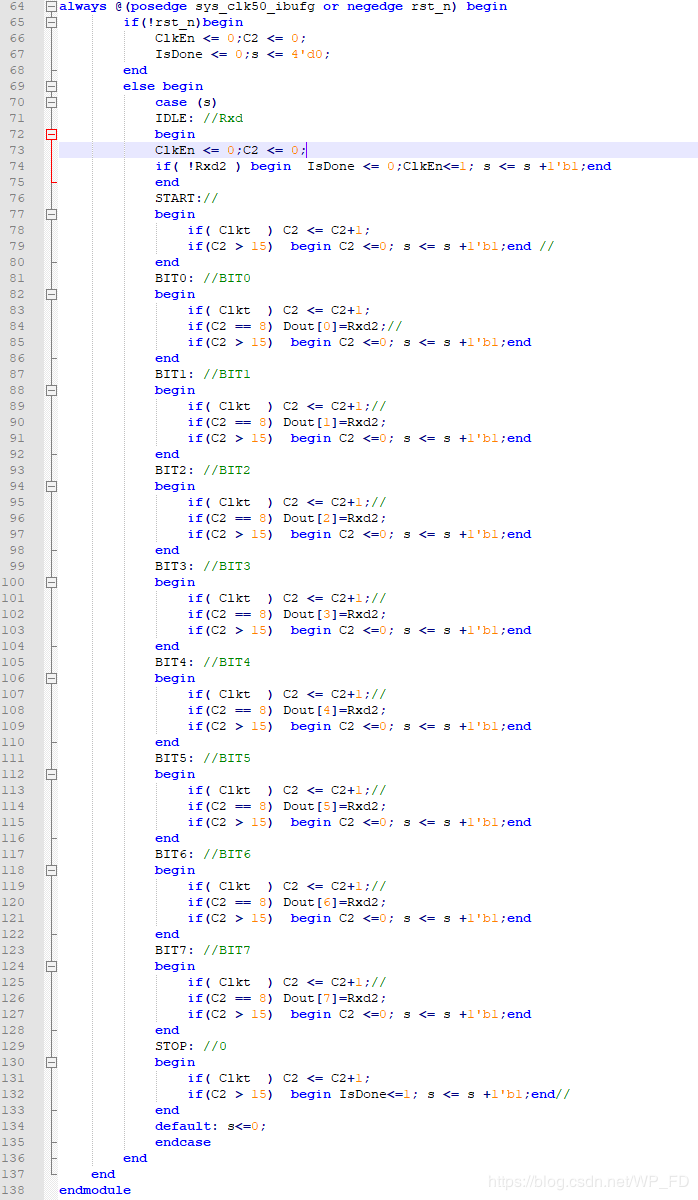

下面主要是uart接收模块的编码讲述,uart接收模块设计主要分为波特率控制计数逻辑和按位接收逻辑,其具体编码如下所示:

波特率控制计数逻辑:

其中325是根据主时钟频率为100Mhz,这里设置波特率为115200,所以计数值=100000000/115200/16=54;需要注意的是在串口接收中需要将一个波特率周期分成16份然后再一个波特率周期的第8份是进行采样,所以需要进行16分频;

按位接收逻辑:

通过检测IsDone上升沿到来来检测串口数据接收是否完成。读者可自行将上一节中的串口发送模块和本节的接收模块组合成一个工程,实现通过USB转串口电路模块实现PC端发送数据相应返回同样的数据给PC,实现回环测试功能。

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

UART串口通信协议是什么?2024-03-19 3528

-

AD9681是否可被zynq-7020的pl端驱动?2023-12-04 659

-

如何实现串口数据的接收呢?2023-06-05 5065

-

Xilinx Zynq7035 PL Cameralink回环实现2023-02-24 1057

-

ZYNQ7020的PS端的基本开发流程2022-07-24 13138

-

PS端实现FreeRTOS嵌入式系统2021-12-22 1395

-

【FPGA ZYNQ Ultrascale+ MPSOC教程】33.BRAM实现PS与PL交互2021-02-22 10101

-

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十九章PL端AXI GPIO的使用2021-02-01 8196

-

ZYNQ实战之PL端LED流水灯设计2020-11-25 2481

-

【正点原子FPGA连载】第十四章UART串口通信实验-领航者ZYNQ之FPGA开发指南2020-09-23 3222

-

请问zynq 怎么实现PS与PL数据交互,然后通过UART串口打印出来?2020-08-03 4831

-

怎么在Petyninux 2014.4上使用Zynq上的PL UART?2020-04-08 3026

-

关于Zynq-7000 PL端HDMI的显示控制的性能分析和应用介绍2019-09-15 4364

-

PL2303 USB转UART串口模块的PcbDoc文件免费下载2019-08-29 2733

全部0条评论

快来发表一下你的评论吧 !