硬件接口协议技术:JTAG内部状态机——TAP控制器

描述

本文主要介绍JTAG总线的引脚定义、接口标准、边界扫描和TAP控制器。

JTAG(Joint Test Action Group;联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如ARM、DSP、FPGA等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

JTAG最初是用来对芯片进行测试的,JTAG的基本原理是在器件内部定义一个TAP(TestAccess Port;测试访问)通过专用的JTAG测试工具对进行内部节点进行测试。JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。现在,JTAG接口还常用于实现ISP(In-System Programmable;在线编程),对Flash等器件进行编程。

JTAG内部有一个状态机,称为TAP控制器。TAP控制器的状态机通过TCK和TMS进行状态的改变,实现数据和指令的输入。

1、引脚定义

含有JTAG口的芯片种类较多,如CPU、DSP、CPLD等。都有如下JTAG引脚定义(信号方向都是针对CPU来说的):

TCK——测试时钟输入。TMS和TDI的数据在TCK的上升沿被采样。数据在时钟的下降沿输出到TDO。建议下拉。

TDI——测试数据输入。输入到指令寄存器(IR)或数据寄存器(DR)的数据出现在TDI输入端,在TCK的上升沿被采样。建议上拉,上拉电阻阻值不能小于1K。

TDO——测试数据输出。来自指令寄存器或数据寄存器的数据在时钟的下降沿被移出到TDO。不用上下拉,悬空时,尽量引出测试点,同时应避免将TDO作为I/O使用。

TMS——测试模式选择。TMS用来设置JTAG口处于某种特定的测试模式,用于控制TAP状态机。必须上拉。

VTref——目标板参考电压,接电源。用来确定CPU的JTAG接口使用的逻辑电平。

可选引脚TRST——测试复位,输入引脚,低电平有效。TRST可以用来对TAP Controller进行复位(初始化)。因为通过TMS也可以对TAPController进行复位(初始化)。所以有四线JTAG与五线JTAG之分。

可选引脚RTCK——测试时钟返回信号。RTCK由目标端反馈给仿真器的时钟信号,用来同步TCK信号的产生,不使用时直接接地。

可选引脚nSRST——目标系统复位信号。与目标板上的系统复位信号相连,可以直接对目标系统复位。同时可以检测目标系统的复位情况,为了防止误触发应在目标端加上适当的上拉电阻。

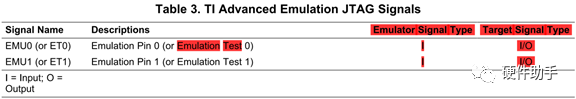

另外还有一些控制器会有如下一些额外信号:

TDIS

PD或TVD——(Presence Detect, Target Voltage Detect),和VTref的功能一样。

EMU[0:n]或ET[0:n]——(EMUlation, Emulation Test)

EMU pins are bi-directional multifunctional pinsthat provide support for the following features:

Boot Modes

Cross Triggers

Core Trace

System Trace

HS-RTDX (high speed RTDX,deprecated functionality)

In the case of Boot Modes, the EMU0/1 pin state is driven by the XDS. HS-RTDX provides bi-directional data transport. Both Core and System Trace transport event history and timing data from the target to the XDS. Crosstriggers are bi-directional triggers that allow an event in one device to causea debug action in other devices.

2、JTAG接口标准

目前JTAG接口的连接有三种标准,即10针、14针接口和20针接口,其定义分别如下所示。

★由于JTAG经常使用排线连接,为了增强抗干扰能力,在每条信号线间加上地线,偶数针脚都是地信号。

3、边界扫描(Boundary-Scan)

边界扫描技术的基本思想是在靠近芯片的输入输出管脚上增加一个移位寄存器单元。因为这些移位寄存器单元都分布在芯片的边界上(周围),所以被称为边界扫描寄存器(Boundary-Scan Register Cell)。

当芯片处于调试状态的时候,这些边界扫描寄存器可以将芯片和外围的输入输出隔离开来。通过这些边界扫描寄存器单元,可以实现对芯片输入输出信号的观察和控制。对于芯片的输入管脚,可以通过与之相连的边界扫描寄存器单元把信号(数据)加载到该管脚中去;对于芯片的输出管脚,也可以通过与之相连的边界扫描寄存器“捕获”该管脚上的输出信号。在正常的运行状态下,这些边界扫描寄存器对芯片来说是透明的,所以正常的运行不会受到任何影响。这样,边界扫描寄存器提供了一个便捷的方式用以观测和控制所需要调试的芯片。另外,芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。一般的芯片都会提供几条独立的边界扫描链,用来实现完整的测试功能。边界扫描链可以串行的输入和输出,通过相应的时钟信号和控制信号,就可以方便的观察和控制处在调试状态下的芯片。

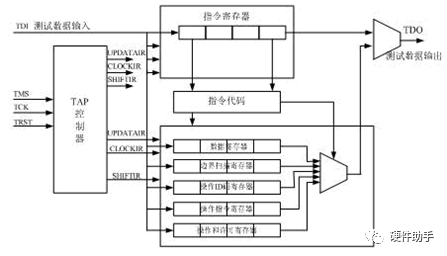

4、TAP(TEST ACCESS PORT)

TAP是一个通用的端口,通过TAP可以访问芯片提供的所有数据寄存器(DR)和指令寄存器(IR)。对整个TAP的控制是通过TAP Controller来完成的。TAP总共包括5个信号接口TCK、TMS、TDI、TDO和TRST:其中4个是输入信号接口和另外1个是输出信号接口。一般,我们见到的开发板上都有一个JTAG接口,该JTAG接口的主要信号接口就是这5个。

通过保持TMS为高电平(逻辑1)并在TCK端输入至少5个选通脉冲(变高后再变低)后TAP逻辑被复位。这使TAP状态机的状态从任何其它状态转到测试逻辑复位状态对,JTAG口和测试逻辑复位,该状态不复位CPU和外设。

通过TAP接口,对数据寄存器(DR)进行访问的一般过程是:

通过指令寄存器(IR),选定一个需要访问的数据寄存器。

把选定的数据寄存器连接到TDI和TDO之间。

由TCK驱动,通过TDI,把需要的数据输入到选定的数据寄存器当中去;同时把选定的数据寄存器中的数据通过TDO读出来。

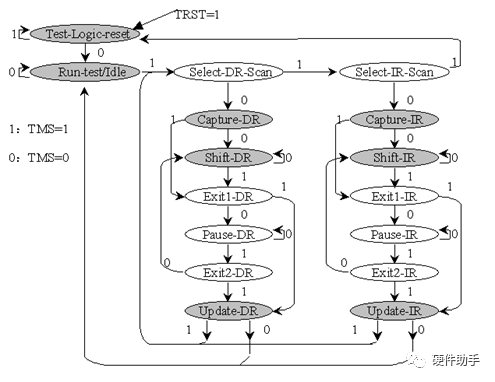

下图是TAP控制器的16-states有限状态机图示:

TAP控制器的状态在TCK的上升沿变化。

在上电时进入逻辑复位状态(Test-Logic Reset),在该状态下,测试部分的逻辑电路全部被禁用,以保证芯片核心逻辑电路的正常工作。通过TRST信号也可以对测试逻辑电路进行复位,使得TAP Controller进入Test-Logic Reset状态。前面我们说过TRST是可选的一个信号接口,这是因为在TMS上连续加5个TCK脉冲宽度的“1”信号也可以对测试逻辑电路进行复位,使得TAP Controller进入Test-Logic Reset状态。所以,在不提供TRST信号的情况下,也不会产生影响。

Shift-DR state扫描DR,TDO输出有效。

Shift-IR state扫描IR,TDO输出有效。

其他状态下TDO输出无效。

如果需要捕获芯片某个管脚上的输出,首先需要把该管脚上的输出装载到边界扫描链的寄存器单元里去,然后通过TDO输出,这样我们就可以从TDO上得到相应管脚上的输出信号。如果要在芯片的某个管脚上加载一个特定的信号,则首先需要通过TDI把期望的信号移位到与相应管脚相连的边界扫描链的寄存器单元里去,然后把该寄存器单元的值加载到相应的芯片管脚。

指令寄存器的访问过程:系统上电,TAP Controller进入Test-Logic Reset状态,然后依次进入:Run-Test/Idle→Select-DR-Scan→Select-IR-Scan→Capture-IR→Shift-IR→Exit1-IR→Update-IR,最后回到Run-Test/Idle状态。在Capture-IR状态中,一个特定的逻辑序列被加载到指令寄存器当中;然后进入到Shift-IR状态。在Shift-IR状态下,通过TCK的驱动,可以将一条特定的指令送到指令寄存器当中去。每条指令都将确定一条相关的数据寄存器。然后从Shift-IR→Exit1-IR→Update-IR。在Update-IR状态,刚才输入到指令寄存器中的指令将用来更新指令寄存器。最后,进入到Run-Test/Idle状态,指令生效,完成对指令寄存器的访问。

数据寄存器的访问:当前可以访问的数据寄存器由指令寄存器中的当前指令决定。要访问由刚才的指令选定的数据寄存器,需要以Run-Test/Idle为起点,依次进入Select-DR-Scan→Capture-DR→Shift-DR→Exit1-DR→Update-DR,最后回到Run-Test/Idle状态。在这个过程当中,被当前指令选定的数据寄存器会被连接在TDI和TDO之间。通过TDI和TDO,就可以将新的数据加载到数据寄存器当中去,同时,也可以捕获数据寄存器中的数据。具体过程如下。在Capture-DR状态中,由TCK的驱动,芯片管脚上的输出信号会被“捕获”到相应的边界扫描寄存器单元中去。这样,当前的数据寄存器当中就记录了芯片相应管脚上的输出信号。接下来从Capture-DR进入到Shift-DR状态中去。在Shift-DR状态中,由TCK驱动,在每一个时钟周期内,一位新的数据可以通过TDI串行输入到数据寄存器当中去,同时,数据寄存器可以通过TDO串行输出一位先前捕获的数据。在经过与数据寄存器长度相同的时钟周期后,就可以完成新信号的输入和捕获数据的输出。接下来通过Exit1-DR状态进入到Update-DR状态。在Update-DR状态中,数据寄存器中的新数据被加载到与数据寄存器的每个寄存器单元相连的芯片管脚上去。最后,回到Run-Test/Idle状态,完成对数据寄存器的访问。

以上就是针对JTAG的相关介绍,详细可参见标准《IEEE Std 1149.1 Test Access Port and Boundary-Scan Architecture》。

编辑:hfy

-

什么是JTAG接口2011-09-21 6084

-

【转】JLINK与JTAG的区别2012-03-01 7958

-

基于状态机的电源控制器设计数字电源2018-10-09 1800

-

JTAG调试接口的四个引脚介绍2019-06-12 5188

-

JTAG的基本原理与测试总结2022-02-17 1688

-

如何完成arm调试协议(JTAG)的转换呢2022-05-24 5724

-

MAXQ微控制器中JTAG接口引脚的复用2009-04-23 1216

-

CAN控制器状态机的分析与实现2016-03-22 1244

-

jtag接口是什么_jtag接口定义2018-01-11 32909

-

状态模式(状态机)2021-12-16 1004

-

JTAG与SWD的含义与引脚2021-12-22 1635

-

关于TAP控制接口的各状态2023-02-01 5000

-

SoC接口技术之低速接口分析(下)2023-04-04 3091

-

什么是状态机?状态机的种类与实现2023-10-19 13159

-

JTAG标准的状态机实现2025-08-21 2967

全部0条评论

快来发表一下你的评论吧 !