I2C总线相关的基本概念和通信流程解析

描述

本文主要介绍I2C总线相关的一些基本概念、通信流程、同步和仲裁、模式切换等。

I2C总线是PHILIPS公司推出的一种串行总线,是具备多主机系统所需的包括总线仲裁和高低速器件同步功能的高性能串行总线。

I2C物理上包括2条双向串行线,一条数据线SDA,一条时钟线SCL。均为OD结构,需要外部上拉,具体选取可参见之前的文章《硬件电路设计之“上下拉电阻”》。

SDA传输数据是大端传输(字节高位先传),每次传输8bit,即一字节。支持多主控(multi master),任何时间点只能有一个主控。总线上每个设备都有自己的一个addr,7bit或10bit,广播地址为全0。

1、基本概念

I2C总线上常用的一些基本概念如下:

主机:初始化发送,产生时钟信号和终止发送的器件。

从机:被主机寻址的器件。

发送器:发送数据到总线的器件。

接收器:从总线接收数据的器件。

多主机:同时有多于一个主机尝试控制总线,但不破坏报文。

仲裁:是一个在有多个主机同时尝试控制总线,但只允许其中一个控制总线并使报文不被破坏的过程。

同步:两个或多个器件同步时钟信号的过程。

总线空闲状态:I2C总线的SDA和SCL同时处于高电平时,规定为总线的空闲状态。此时各个器件的输出级场效应管均处在截止状态,即释放总线,由两条信号线各自的上拉电阻把电平拉高。

开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

结束信号:SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。

数据传输:SCL为高电平时,SDA线必须保持稳定,SDA上传输一个bit数据(电平采样);

数据改变:SCL为低电平时,SDA线才能改变电平。

I2C应答信号:主控每发送完8bit数据后等待从设备ACK。即在第9个CLK,若从设备发回ACK,SDA会被拉低(ACK信号为‘0’)。若没有ACK,SDA会被置高(NAK信号为‘1’),这会引起主控发生RESTART或STOP流程。

★NAK主要有两个作用:一是表示接收器未成功接收数据字节;二是当接收器是主机时(主机读数据),它收到最后一个字节后,应发送一个NAK信号,以通知从机结束数据发送,并释放总线,以便主机发送一个停止信号STOP。

2、基本通信流程

一次完整的I2C通信流程如下:

主设备发出开始信号(Start)。

主设备发出1字节的从设备地址信息,其中最低位为读写控制码(0为写,1为读),高7位为从设备地址码。

从设备发出ACK信号。

主设备开始对从设备进行读写操作。如果是读操作,则每读取1字节,主设备会发送一个应答信号(ACK)给从设备,如果是写操作,则每写入1字节,从设备会发送一个应答信号(ACK)给主设备。

主设备发出结束信号(Stop)。

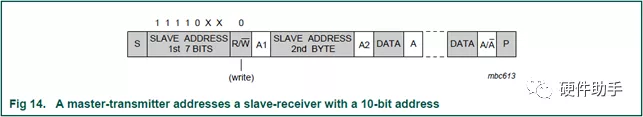

3、10bit地址的发送

10bit地址的发送分两次发送,第一次发送高2bit和读写信号(高5bit固定为识别码11110),第二次发送低8bit,每次都有ACK信号。I2C规范并没有强制规定发送端在发送接收端地址后接收端非要做出响应不可,也可以默不作声,即便默不作声,发送端还是会继续工作,开始进行数据传输及读/写指令;

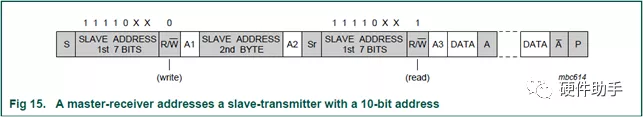

实际使用中10bit地址的寻址有两种方式:一种是只进行一次寻址,10bit地址的发送分两次发送,第一次发送高2bit和读写信号(实际读写操作),第二次发送低8bit。另一种是进行两次寻址,第一次寻址将10bit地址的发送分两次发送,第一次发送高2bit和读写信号,第二次发送低8bit;第二次寻址通过一个重复开始信号跟高2bit地址和读写信号(实际读写操作)进行二次寻址,第二次寻址只有第一次匹配上的从机会有应答。

主机发送数据时,当从机接收到开始条件后的10bit地址,从机就和它自己的地址比较从机地址的第一个字节(1111 0XX),并检查第八个bit(读写位)是否为0。有可能多个设备都匹配并产生应答(A1)。接下来所有从机开始匹配自己地址与第二个字节的8个bit(XXXXXXXX),这时就只有一个从机匹配并产生应答(A2)。被主机寻址匹配的从机会保持被寻址的状态直到接收到终止条件或者是重复开始条件后跟着一个不同的从机地址。

在第二个应答A2之前,处理过程与上面的一致。在重复开始条件(Sr)之后,匹配的从机会保持被寻址上的状态。这个从机会检查Sr之后的第一个字节的前7bit是否正确,然后测试第8bit是否为1(读)。如果这也匹配的话,从机就认定它被作为一个发送器被寻址到了并产生应答A3。从机会保持被寻址的状态直到接收到终止条件(P)或者重复开始条件(Sr)跟着一个不同的从机地址。然后这个时候的重复开始条件下,所有的从机会比较它们的地址与11110XX比较并测试第八位(读写位)。然而它们不会寻址到,因为对于10bit设备。读写位是1,或者对于7bit的设备,1111 0XX的从机地址不匹配。

4、同步和仲裁

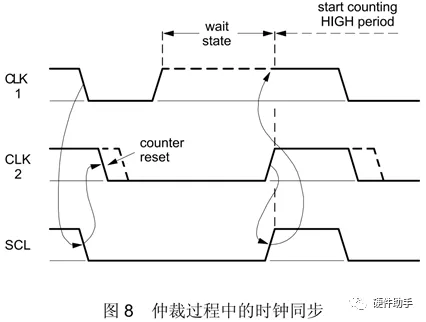

所有主机在SCL线上产生它们自己的时钟来传输I2C总线上的报文。数据只在时钟的高电平周期有效。因此,需要一个确定的时钟进行逐位仲裁。

时钟同步通过线与连接I2C接口到SCL线来执行。这就是说:SCL线的高到低切换会使器件开始数它们的低电平周期,而且一旦器件的时钟变低电平,它会使SCL线保持这种状态直到到达时钟的高电平。但是,如果另一个时钟仍处于低电平周期,这个时钟的低到高切换不会改变SCL线的状态。因此,SCL线被有最长低电平周期的器件保持低电平。此时,低电平周期短的器件会进入高电平的等待状态。

当所有有关的器件数完了它们的低电平周期后,时钟线被释放并变成高电平。之后,器件时钟和SCL线的状态没有差别,而且所有器件会开始数它们的高电平周期。首先完成高电平周期的器件会再次将SCL线拉低。

这样,产生的同步SCL时钟的低电平周期由低电平时钟周期最长的器件决定,而高电平周期由高电平时钟周期最短的器件决定。

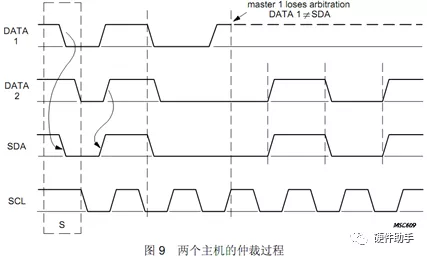

主机只能在总线空闲的时侯启动传输。两个或多个主机可能在起始条件的最小持续时间(tHD;STA)内产生一个起始条件,结果在总线上产生一个规定的起始条件。

当SCL线是高电平时,仲裁在SDA线发生。这样,在其他主机发送低电平时,发送高电平的主机将断开它的数据输出级,因为总线上的电平与它自己的电平不相同。

仲裁可以持续多位。它的第一个阶段是比较地址位。如果每个主机都尝试寻址相同的器件,仲裁会继续比较数据位(如果是主机)或者比较响应位(如果是主机)。因为I2C总线的地址和数据信息由赢得仲裁的主机决定,在仲裁过程中不会丢失信息。

丢失仲裁的主机可以产生时钟脉冲直到丢失仲裁的该字节末尾。

由于Hs模式的主机有一个唯一的8位主机码,因此一般在第一个字节就可以结束仲裁。

如果主机也结合了从机功能,而且在寻址阶段丢失仲裁,它很可能就是赢得仲裁的主机在寻址的器件。因此,丢失仲裁的主机必须立即切换到它的从机模式。

产生DATA1的主机的内部数据电平与SDA线的实际电平有一些差别,如果关断数据输出,这就意味着总线连接了一个高输出电平。这不会影响由赢得仲裁的主机初始化的数据传输。

由于I2C总线的控制只由地址或主机码以及竞争主机发送的数据决定,没有中央主机,总线也没有任何定制的优先权。

在串行传输时,当重复起始条件或停止条件发送到,I2C总线的时侯,仲裁过程仍在进行。如果可能产生这样的情况,有关的主机必须在帧格式相同位置发送这个重复起始条件或停止条件。也就是说,仲裁不能在下列情况之间进行:

重复起始条件和数据位

停止条件和数据位

重复起始条件和停止条件

从机不被卷入仲裁过程。

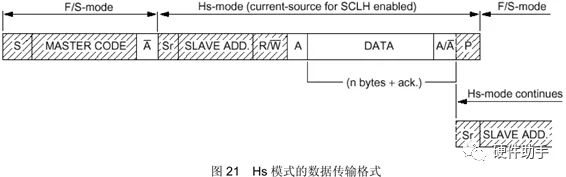

5、高速模式切换

Hs模式的串行数据传输格式符合标准模式I2C总线规范,Hs模式只能在下面的情况下(所有都在F/S模式)启动:

起始条件(S)

8位的主机码(00001XXX)

不响应位(A/)

主机码有两个主要的功能:

它允许在F/S模式速度下竞争主机之间仲裁和同步,结果得到一个获胜的主机。

它表示Hs模式传输的开始。

Hs主机码是保留的8位代码,它不用于从机寻址或其他目的。而且,由于每个主机都有唯一的主机码,I2C总线系统最多可以有8个Hs模式主机(主机码0000 1000应保留作测试和诊断用)。Hs模式主机器件的主机码是软件可编程的,由系统设计者决定。

以上就是针对I2C总线的一些基本介绍。

编辑:hfy

-

i2c总线ppt(I2C总线器件应用)2008-08-13 1363

-

i2c总线技术 (非常详细)2009-03-25 831

-

i2c总线的特点2009-08-05 2657

-

基于I2C总线的单主多从单片机之间的通信2009-12-19 864

-

I2C总线在Linux系统中的驱动设计2010-12-29 1015

-

什么是i2c总线2007-11-05 4143

-

基于CPLD的I2C总线接口设计2011-02-12 1405

-

i2c总线相关知识2017-12-06 4572

-

I2C总线模块解析2020-08-10 4790

-

关于I2C总线的读写操作流程详解2020-11-29 37593

-

I2C总线的基本通信总结2021-08-26 20367

-

基于单片机的I2C总线与AT24C01实验 I2C总线通信原理讲解2023-07-27 5755

-

I2C串行总线协议是什么?I2C总线有哪些优点?2023-09-12 3271

-

物联网嵌入式软件中的I2C总线设计详解2024-09-29 2000

-

I2C总线通信原理 如何设计I2C总线电路2025-01-31 2667

全部0条评论

快来发表一下你的评论吧 !