DRAM的矩阵存储电路设计方案

描述

DRAM(Dynamic Random Access Memory)

即动态随机存取存储器,它和 SRAM(静态随机存取存储器)一样都是常见的系统内存,也就是说我们个人电脑里的内存条通常都是DRAM。但是DRAM和 SRAM 两者之间有着很大的区别。其中最大的区别就是DRAM的地址总线接口与 SRAM 的不同。DRAM使用了dram 地址复用技术。也就是行地址与列地址分时复用技术,这就是dram 的关键技术所在。主要原因是由它的硬件电路决定的。

DRAM与 CPU 的接口(寻址方式)

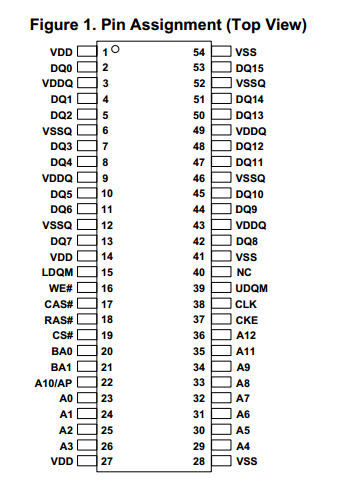

举个栗子,EM63A165TS 是 EtronTech 公式的一款 DRAM 芯片,容量为 16M*16Bit,分成四个 Bank,每一个 Bank 为 4M*16Bit。但是,观察它的芯片管脚图,你就会发现它的地址线只有 13 根(A0-A12)和两根 Bank 控制线。13 根的控制线按照 SRAM 的寻址方法,每个 Bank 只有 2^13=8K,远远没有达到 4M。这是为什么呢?

原因在于,DRAM 普遍采用的是行与列地址分时复用技术进行寻址。在 DRAM 的矩阵存储单元中,地址可以分成行地址和列地址。在寻址时,必须先进行行寻址然后在进行列寻址,这是由 DRAM 的硬件电路所决定的。所以,对行地址线和列地址线进行共用,既节省了地址线,也不会降低 DRAM 原有的工作速率(因为 DRAM 的行地址和列地址就是要分时传送的)。而,如果是 SRAM 采用这种寻址方式的话,则会大大降低其工作速度。

那么,EM63A165TS 只有 13 根地址线也就可以理解了,在其数据手册上可以知道,A0-A12 是行地址线,同时 A0-A8 复用为列地址线,那么就有了 22 根地址线,2^22=4M。

DRAM硬件电路

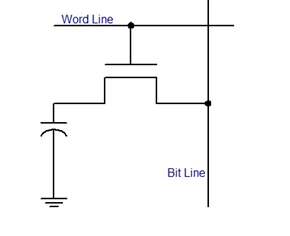

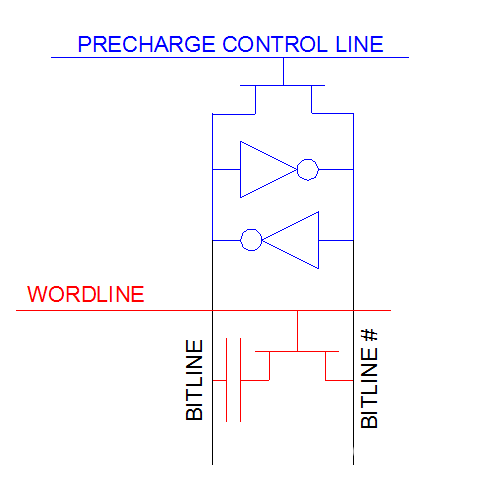

下图所示是 DRAM 一个位的存储单元电路,信息存储在电容之中,电容有电荷则为 1,没电则为 0。当字线为高时,该 MOS 管导通,若电容有电荷,则会在位线上产生电流,反之则无。因为是用电容存储信息,而电容会存在漏电流,所以必须要配合周期刷新电路来维持电容的电荷。

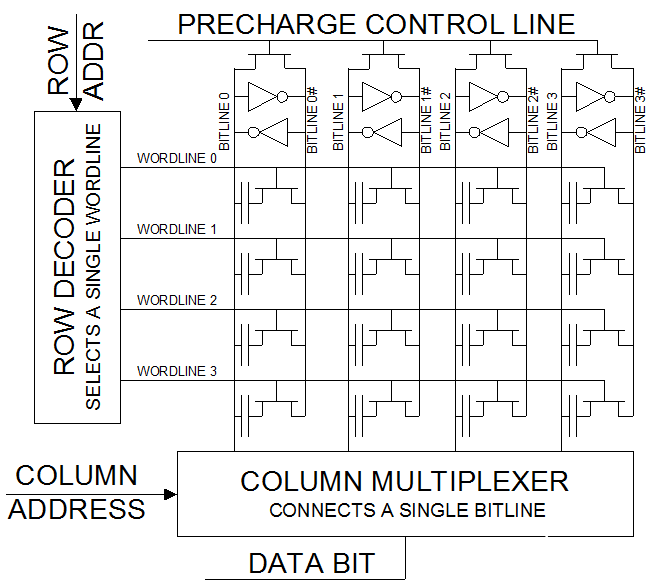

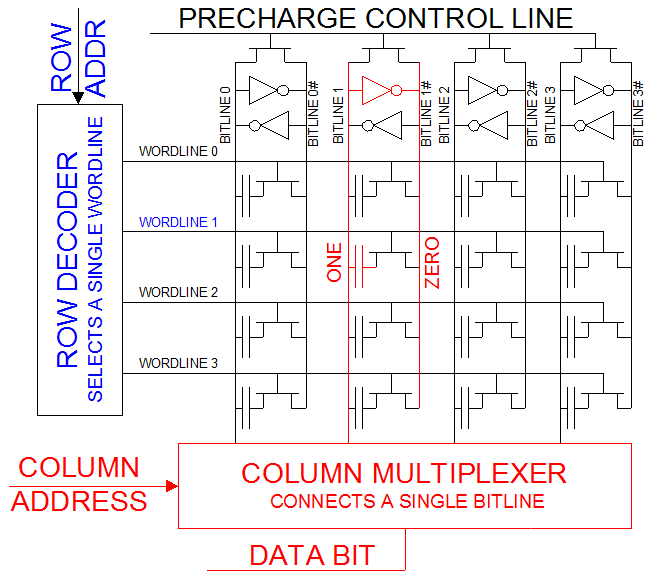

下图所示则是一个 DRAM 的矩阵存储电路。

在读写操作前必须先选择行,相应 MOS 管导通。

选定行后,再选择列。然后就可以对某一位进行读写操作。

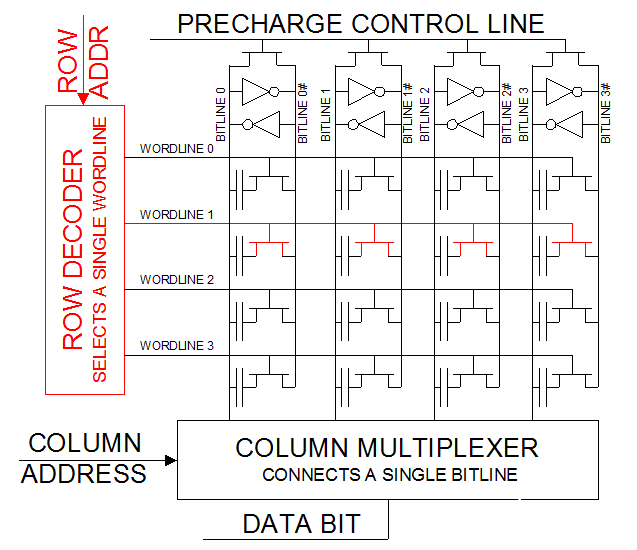

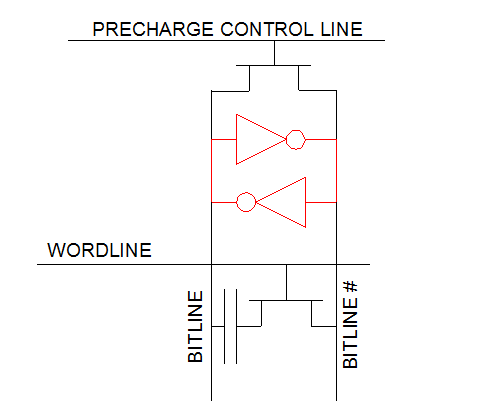

读过程中可以通过下图的感应放大器电路来保持电容的电荷不变。该电路由两个反相器组成。

当预充电线为高时,刷新电路导通,然后维持电容中的电荷量不变。由两个反相器和一个 MOS 管组成。

编辑:hfy

-

LED路灯驱动电路设计方案2023-11-14 721

-

小信号放大电路设计方案汇总2021-09-14 3535

-

CAN总线接口EMC标准电路设计方案2021-07-12 3760

-

基于电流传输器的检测电路设计方案2021-06-15 1398

-

SSS1530电路设计方案2021-06-10 1413

-

带NFC管理的移动通信终端电路设计方案2021-06-07 1371

-

卡拉OK人声增效电路设计方案2021-03-25 2255

-

485接口EMC电路设计方案2020-02-05 7863

-

电子电路设计方案的步骤和注意事项2019-04-12 17025

-

基于FPGA的调焦电路设计方案资料下载2018-05-07 1393

-

乘法器电路设计方案汇总(五款模拟电路设计原理及仿真程序分享)2018-01-17 63876

-

精密光电检测电路设计方案2016-12-15 1128

全部0条评论

快来发表一下你的评论吧 !