Xilinx zynq AXI总线全面解读

描述

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一种总线协议, Xilinx从 6 系列的 FPGA 开始对 AXI 总线提供支持,目前使用 AXI4 版本。

AXI总线

ZYNQ有三种AXI总线:

(A)AXI4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允许最大256轮的数据突发传输;

(B)AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元。

(C)AXI4-Stream:(For high-speed streaming data.)面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。

AXI4总线和AXI4-Lite总线具有相同的组成部分:

① 读地址通道,包含ARVALID, ARADDR, ARREADY信号;

② 读数据通道,包含RVALID, RDATA, RREADY, RRESP信号;

③ 写地址通道,包含AWVALID,AWADDR, AWREADY信号;

④ 写数据通道,包含WVALID, WDATA,WSTRB, WREADY信号;

⑤ 写应答通道,包含BVALID, BRESP, BREADY信号;

⑥ 系统通道,包含:ACLK,ARESETN信号。

而AXI4-Stream总线的组成有:

① ACLK信号:总线时钟,上升沿有效;

② ARESETN信号:总线复位,低电平有效

③ TREADY信号:从机告诉主机做好传输准备;

④ TDATA信号:数据,可选宽度32,64,128,256bit

⑤ TSTRB信号:每一bit对应TDATA的一个有效字节,宽度为TDATA/8

⑥ TLAST信号:主机告诉从机该次传输为突发传输的结尾;

⑦ TVALID信号:主机告诉从机数据本次传输有效;

⑧ TUSER信号 :用户定义信号,宽度为128bit。

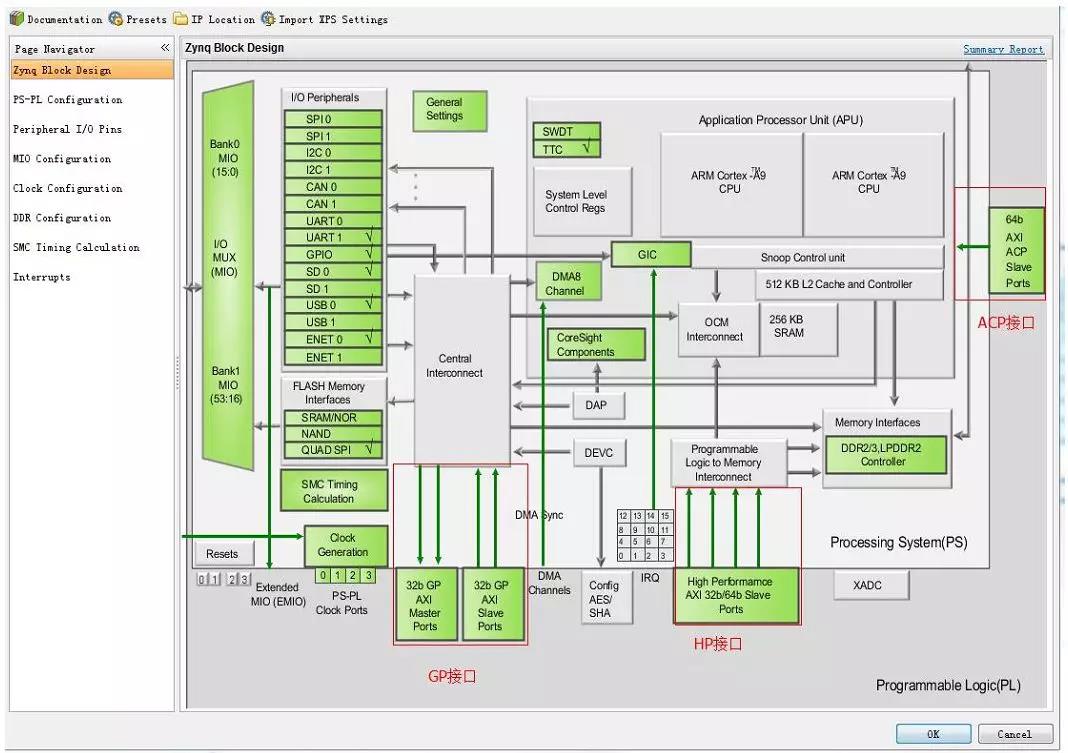

AXI接口

AXI有三种接口:

(A)AXI-GP接口(4个):是通用的AXI接口,包括两个32位主设备接口和两个32位从设备接口,用过该接口可以访问PS中的片内外设。

(B)AXI-HP接口(4个):是高性能/带宽的标准的接口,PL模块作为主设备连接(从下图中箭头可以看出)。主要用于PL访问PS上的存储器(DDR和On-Chip RAM

(C)AXI-ACP接口(1个):是ARM多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理DMA之类的不带缓存的AXI外设,PS端是Slave接口。

AXI协议

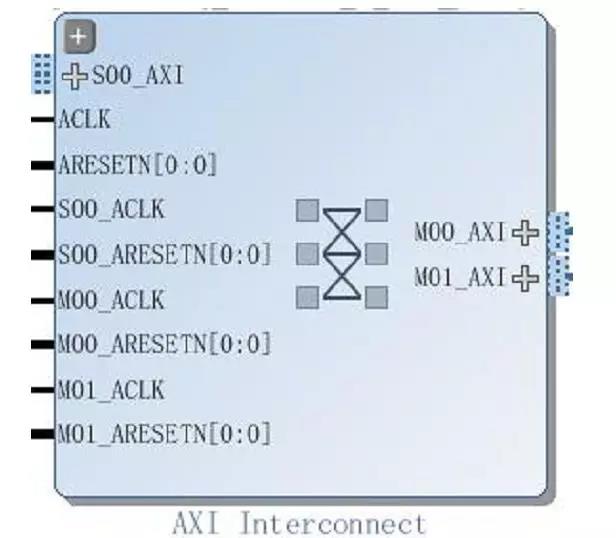

协议的制定是要建立在总线构成之上的。因此说AXI4,AXI4-Lite,AXI4-Stream都AXI4协议。AXI总线协议的两端可以分为分为主(master)、从(slave)两端,他们之间一般需要通过一个AXI Interconnect相连接,作用是提供将一个或多个AXI主设备连接到一个或多个AXI从设备的一种交换机制。

AXI Interconnect的主要作用是,当存在多个主机以及从机器时,AXIInterconnect负责将它们联系并管理起来。由于AXI支持乱序发送,乱序发送需要主机的ID信号支撑,而不同的主机发送的ID可能相同,而AXI Interconnect解决了这一问题,他会对不同主机的ID信号进行处理让ID变得唯一。

AXI协议将读地址通道,读数据通道,写地址通道,写数据通道,写响应通道分开,各自通道都有自己的握手协议。每个通道互不干扰却又彼此依赖。这是AXI高效的原因之一。

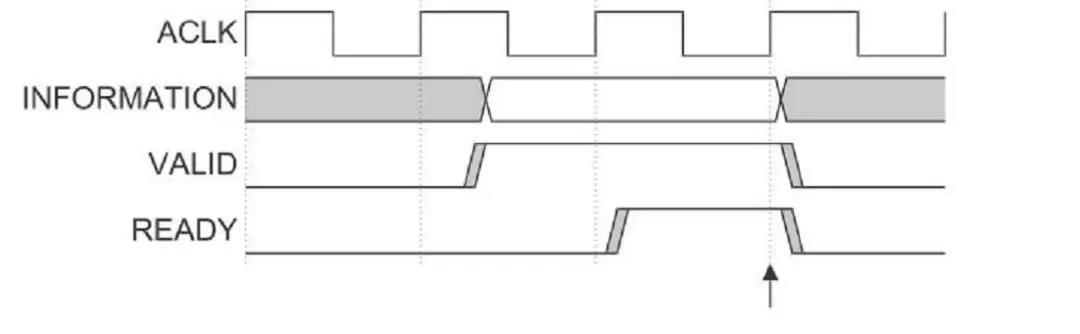

01:AXI握手协议

AXI4 所采用的是一种 READY,VALID 握手通信机制,简单来说主从双方进行数据通信前,有一个握手的过程。传输源产生 VLAID 信号来指明何时数据或控制信息有效。

而目地源产生READY信号来指明已经准备好接受数据或控制信息。 传输发生在VALID和 READY信号同时为高的时候。

如下图中的一种实例:

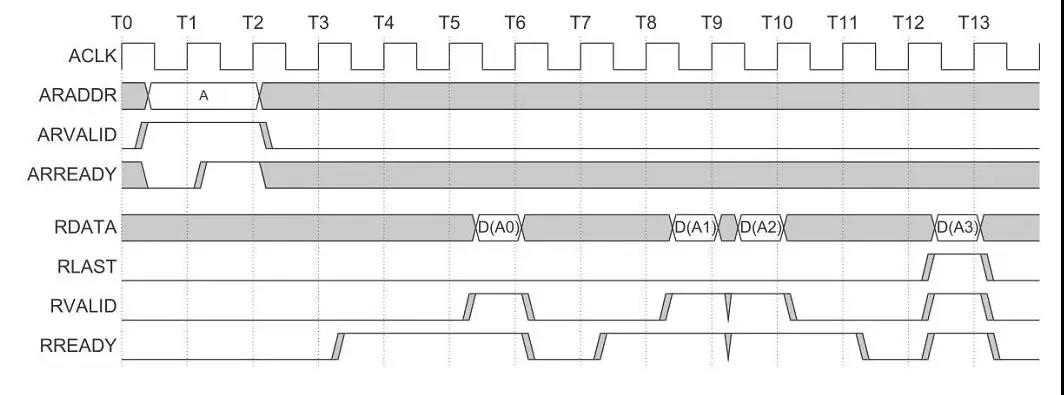

02:突发式读写

突发式读的时序:

当地址出现在地址总线后,传输的数据将出现在读数据通道上。设备保持VALID 为低直到读数据有效。为了表明一次突发式读写的完成,设备用 RLAST 信号来表示最后一个被传输的数据。

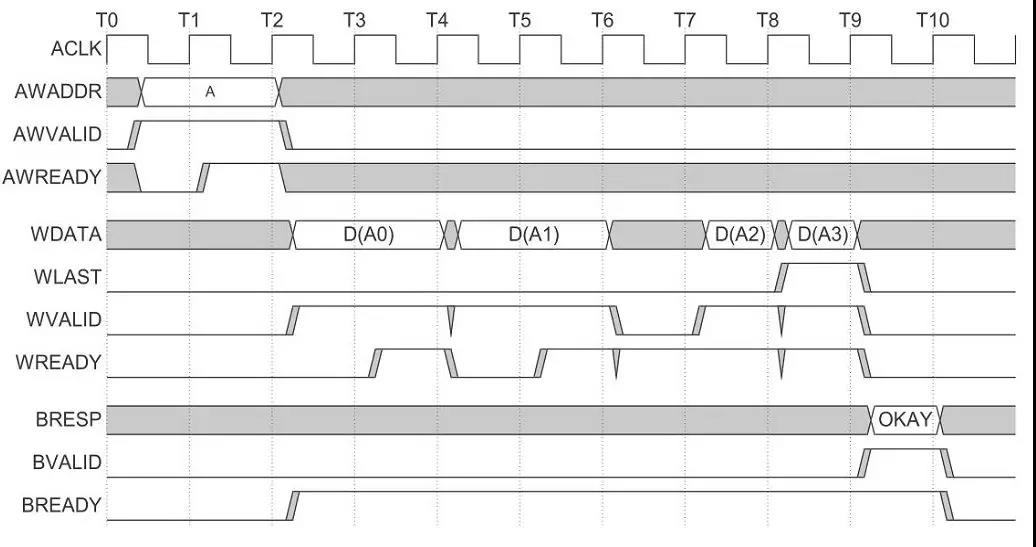

突发式写的时序:

这一过程的开始时,主机发送地址和控制信息到写地址通道中,然后主机发送每一个写数据到写数据通道中。当主机发送最后一个数据时,WLAST 信号就变为高。当设备接收完所有数据之后他将一个写响应发送回主机来表明写事务完成。

编辑:hfy-

玩转Zynq连载3——AXI总线协议介绍12019-05-06 2792

-

玩转Zynq连载34——[ex54] 基于Zynq的AXI GP总线的从机接口设计2019-11-12 5360

-

玩转Zynq连载37——[ex56] 基于Zynq的AXI HP总线读写实例2019-11-26 4195

-

玩转Zynq连载38——[ex57] Zynq AXI HP总线带宽测试2019-11-28 4916

-

从应用角度详解什么是AXI2018-07-13 12933

-

如何使用Xilinx AXI进行验证和调试2018-11-20 4863

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 7562

-

ARM+FPGA开发:基于AXI总线的GPIO IP创建2020-12-25 6998

-

ZYNQ中DMA与AXI4总线2020-11-02 5300

-

对AXI总线知识详解解析2021-04-09 7529

-

全面介绍ZYNQ-AXI互联IP2021-05-11 8182

-

AXI总线协议的简单知识2022-07-15 4300

-

AXI总线协议简介2022-10-10 11470

-

AXI总线工作流程2023-05-25 2007

-

ZYNQ基础---AXI DMA使用2025-01-06 4235

全部0条评论

快来发表一下你的评论吧 !