Vivado设计中生成VPSS时出现的常见问题解析

描述

Video Processing SubSystem (VPSS) IP 核简介

赛灵思系列 Video Processing Subsystem IP 核是为了便于使用而被封装到单个 IP 中的一组系列处理 IP。该核是基于 HLS 的 IP。这就是说当您将 IP 添加到设计中后,此核用 C/C++ 编写,然后在后台由 Vivado 转换为 RTL(VHDL/Verilog)。

VPSS IP 支持多种系列处理功能,例如:

- 去交织

- 系列缩放(向上和向下缩放)

- 色彩空间转换

- 帧速率转换

VPSS IP 随附 Vivado 2018.3 及更高版本免费提供。

有关 VPSS IP 的文档,请参阅《Video Processing Subsystem 产品指南》 (PG231)。

建议 #1:从(硬件)示例设计开始

本系列条目旨在为任何即将使用 VPSS IP 的用户提供指导。

正如我先前提到过的,VPSS IP 基于 HLS 并有多个核。

这就会涉及到用户需要遵循的一些复杂规则。操作并不复杂,但要快速启动,最好的方法是参考硬件和软件设计的示例设计。

生成硬件 (Vivado) 示例设计非常简单。

(注意:这些步骤记录在《Video Processing Subsystem 产品指南》 (PG231) 第 67 页的“详细示例设计”中)

1. 打开 Vivado(我使用的是 2018.3 版)

2. 为支持的一个电路板(KC705、ZCU102、ZCU104 或 ZCU106)创建一个新工程

- 注 1:如果您使用的是 Vivado webpack 版,则只能使用 ZCU104 电路板。

- 注 2:您是否有此电路板并不重要。示例设计仅用作参考。您可以重新创建自己的电路板。

3. 创建块设计 (BD) 并添加 Video Processing SubSystem IP。保存块设计。

4. 在源窗口中,右键单击 IP 并选择“Generate Example Design”。

5. 选择要生成示例设计的路径

注意:生成 VPSS 时出现的常见问题是使用 Windows 操作系统时的路径问题。如果您使用的是 Windows 主机操作系统,请确保使用最短路径进行示例设计(和任何一般项目)。

在 Vivado 设计中,最重要的是要看来自 VPSS 的复位信号(该信号控制上游 (TPG) 和下游 (AXI4S 到系列输出) IP)。

此信号主要用于拖延上游 IP 发送数据(直到配置了 VPSS 且做好了接受新数据的准备时)。由于 VPSS 是基于 HLS 的 IP,因此至关重要的是要确保进来的第一个数据是帧的第一个像素。

注意:由于此复位信号,每当 VPSS IP 中的配置被更改时,可能会需要重新配置通过此复位连接的上游 IP。

此外,值得注意的是,示例设计不会在电路板上输出系列数据。设计检查 VPSS 是否在正常工作的方式是确认 AXI4-Stream 到系列输出 IP 已锁定,这就意味着 VTC 中设置的分辨率和 VPS S 输出的像素/行数相匹配。

注意:系列时钟未调整为系列分辨率,而且固定为 150 MHz。因此,在电路板上输出系列数据将无法正常工作。但是,这个时钟足以表明 VPSS 足够快,可以容纳每个时钟 1 个像素 (PPC) 1080p 个像素的流的配置。

如果需要生成软件应用示例设计,则需要为 BD 生成 BD 输出产品(在源窗口中右键单击“BD > generate output products”)并选择导出到硬件(文件导出硬件)。

注意:如果要在电路板上运行设计,还需要为设计生成比特流,并在导出硬件时检查“include bitstream”选项。

建议 #2:查看软件示例应用

在编写自己的应用之前,最好先将 VPSS 应用示例设计作为参考。

要生成此应用示例设计:

1. 打开 SDK 并将工作空间设置到示例设计的 .sdk 文件夹。

2. 创建新的硬件平台规格:

- “File > New > Other > Xilinx > Hardware Platform Specification”

- 单击“浏览”并选择从 VPSS Vivado 示例设计生成的 .hdf 文件,然后单击“Finish”。

注意:如果您从 Vivado VPSS 示例工程启动 SDK,则不需要此步骤 (2.) (此步骤会自动完成)。

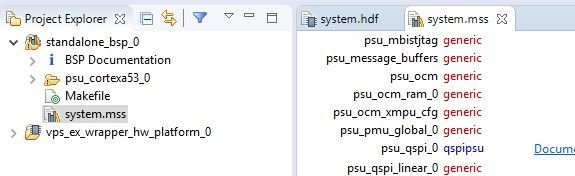

3. 创建一个新的 BSP:单击“File > New > Board Support Package”。保留 BSP 的默认设置,然后单击“Finish”。

4. 在 BSP 文件夹下,双击 system.mss 文件打开它(如果尚未打开的话)。

5. 在 system.mss 文件中,找到与系列处理器子系统对应的行,然后单击“Import Examples”。

6. 在“Examples”窗口中,选择系列处理器子系统示例(xv_procss_example),然后单击“OK”。

运行应用

7. 将 USB 电缆从主机 PC 连接到 USB JTAG 端口。确保安装了相应的器件驱动。

8. 将第二根 USB 电缆从主机 PC 连接到 USB JTAG 端口。确保已安装 USB UART 驱动。

注意:在 ZCU104 电路板上,UART 和 JTAG 只需要一根 USB 电缆。

9. 将评估板连接到电源插槽。

10. 打开电路板。

11. 使用以下标准 COM 端口设置在主机 PC 上启动终端程序(例如,超级终端):

- 波特率:115200

- 数据比特:8

- 奇偶校验:无

- 停止位:1

- 流量控制:无

12. 右键单击项目资源管理器中的应用,然后选择“Build Project”。

13. 右键单击应用,然后选择“Run As… > Run Configurations”。

14. 在“Run Configurations”窗口中,右键单击 Xilinx C/C++应用(系统调试器)并选择“New”。

15. 启用”Program FPGA”。如果以 ZCU102/ZCU104/ZCU106 电路板为目标,请确保已启用“Run psu_init”。

16. 单击“Run”对 FPGA 进行编程并在电路板上启动应用。

示例应用将运行两个用例,并应该会报告测试成功。

建议 #3:参阅 API 文档

预计将使用驱动 API 对 Video Processing Subsystem IP 进行配置和控制(即使在 (PG231) 中为了调试目的记录了寄存器映射,也不支持直接访问寄存器)。

通过查看 API 文档,确保您熟悉所有可用的 API 并了解其用途。要打开文档,单击与 system.mss 文件中的 VPSS 相对应的“Documentation”链接(在 BSP 下)

建议 #4:使用 VPSS 日志进行调试

示例应用中很重要的一行是显示 UART 中的日志的那一行:

XVprocSs_LogDisplay(VpssPtr);

如果您遇到 VPSS 方面的问题,您真的需要使用此功能,因为它会让您清楚地了解到 VPSS 无法正常工作的原因(配置错误、系统停止等)

编辑:hfy

-

Keystone NDK常见问题解答2024-10-11 513

-

TFPxxx常见问题解答2024-09-29 455

-

光耦失效的几种常见问题解析2023-12-25 10156

-

CLOCK常见问题解答2023-11-23 659

-

CAN总线常见问题解答2021-12-27 2807

-

PDIUSBD12常见问题解答资料下载2021-05-14 1260

-

AN-1291:数字电位计:常见问题解答2021-03-19 1198

-

英飞凌IGBT应用常见问题解答2018-12-13 10329

-

labview入门常见问题解答2013-06-20 3731

-

Linux的常见问题解答和管理技巧2012-08-19 2758

-

PLL常见问题解答2012-08-12 2532

-

PC 音质常见问题解答2010-08-02 652

-

新手-iPhone/touch常见问题解答2010-02-02 608

-

VxWorks常见问题解答2009-03-28 598

全部0条评论

快来发表一下你的评论吧 !