基于FPGA的实时图像处理仿真实验方案实现

电子说

描述

对CMOS图像传感器采集图像过程中的噪声预处理问题,提出一种在FPGA中实现的可配置的自适应加权均值滤波模块设计方案。该模块通过检测滤波窗口内不同方向的方差来确定纹理方向,从而自动生成相应的加权系数,可以对宽度不超过4 094像素的图像进行流水线式的加权均值滤波处理,达到去噪保边的目的。最后经过实验验证,当图像宽度为2 048时,输入输出延时仅为42.04 μs,满足实时性要求,且滤波后的图像噪点明显减少,纹理边缘毛刺消失,能较好地改善图像质量。

0 引言

CMOS图像传感器相较于传统的CCD而言,具有更高的集成度,更灵活的图像捕获方式,更宽的动态范围,加上其低成本、低功耗的特点,越来越受到人们的重视并得到广泛的应用。但是CMOS图像传感器在采集图像过程中由于暗电流和放大器偏差等原因导致其抗噪声能力较差,引起图像噪点增多,质量下降[1],这会直接影响图像的后期处理工作。为方便图像的后续处理,在图像采集过程中,对图像进行预处理是十分必要的。

1 降噪方法

高斯噪声是数字图像中最常见的噪声[2],消除图像高斯噪声一般考虑使用均值滤波方法。传统的邻域均值滤波法对高斯噪声可以起到抑制作用[2],但是会引起图像边缘部分细节的丢失。针对图像噪声与纹理边缘的相似性,文献[2]提出一种基于置信区间的自适应加权均值滤波方法。该方法利用高斯噪声的正态分布特性,将灰度值处于置信区间内的像素点判断为噪声,能在滤除噪声的同时,保证图像边缘不受影响。但该方法需要对噪声图像的灰度均值及噪声的标准差预先进行估计,实时性较差。文献[3]提出一种基于灰度值相似度和空间邻近度的加权均值滤波算法,不仅考虑到滤波窗口中像素值的灰度值差异,也考虑到距离对中心像素点的影响,根据其两个参数局部邻域灰度因子和局部邻域空间因子,生成加权系数。该方法相比于传统的高斯滤波方法有更好的去噪效果,但运算量较大,处理速度较慢。

文献[4]设计了一种基于极值点的加权均值滤波方法。该方法可以根据图像的灰度值,自适应调整加权系数。通过4个方向上的方差计算,可以确定滤波窗口与纹理边缘是否重合,并判断出纹理的方向,据此生成不同的权重。这样就可以达到较好的去噪保边的效果。但如果使用上位机实现该算法,无法保证实时性。

通常上位机处理速度较慢,无法与图像采集、传输与存储系统形成一套流水线,而FPGA具有高速、并行、数据吞吐量大的特点,因此针对以上问题,提出一种基于FPGA实现的自适应加权均值滤波方法。该方法将文献[4]提出优化算法映射到FPGA中,实现实时的图像处理。

2 算法分析及其FPGA映射

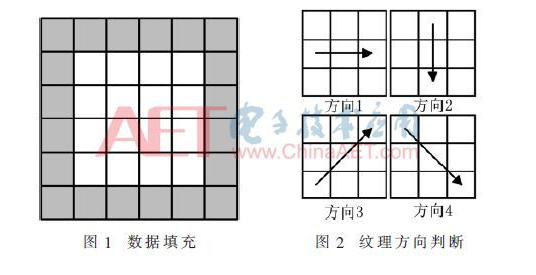

高斯噪声是基于像素点的噪声,因此考虑使用3×3的滤波窗口[5]。采用3×3的窗口对图像进行均值滤波时,图像第1行和第1列及最后1行和最后1列的像素点会由于数据不足而无法参与运算。为保证数据的完整性,可以采用填充法[6],在处理前先对图像进行2×2的扩展。扩充后数据如图1所示,白色部分为图像原始数据,阴影部分为填充的数据。

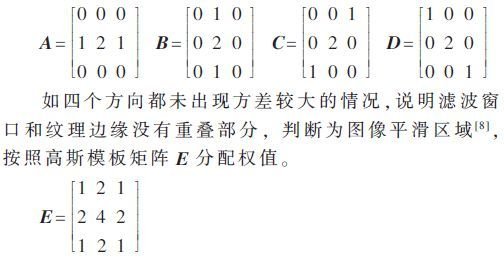

滤波模板生成,首先需要检测窗口中心点是否为极值点,如果是则可能是噪声点或纹理边缘[7]。通过窗口4个方向上3个点方差计算确定该点是噪声还是纹理边缘,如图2所示。如果滤波窗口与纹理边缘重合,4个方向中与纹理边缘有交叉的方向,由于灰度值跳变,会出现方差较大的情况。

而与纹理边缘平行的方向上,灰度值不会出现大幅跳变,因此方差较小。根据4个方向的方差,确定纹理边缘的方向,再确定其加权系数,在穿越图像纹理边缘的方向上,不做滤波处理。方向1到4上生成加权系数分别为A、B、C、D。

A=0 0 0

以上权重的模版矩阵都符合正态分布的规律,且矩阵所有元素的和为2的整数次幂,在后续的归一化运算中,可以通过移位寄存器代替除法器实现,节省大量FPGA资源。

3 FPGA实现

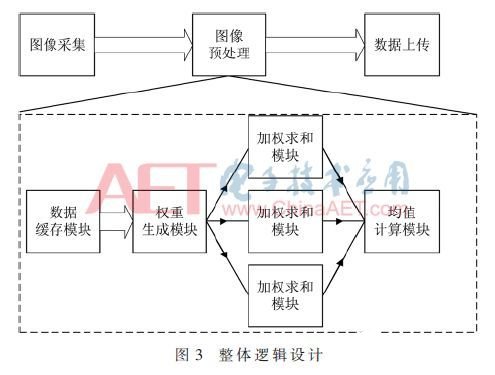

本设计选用Xilinx FPGA XC6SLX45作为主控芯片,以模块化设计理念为指导,设计了分辨率可配置的加权均值滤波模块。该模块由4个部分组成,包括数据缓存模块、权重生成模块、加权求和模块以及求均值模块,四个子模块采用流水线的方式工作,保证数据能够实时处理,整体逻辑设计如图3所示。

3.1 数据缓存模块设计

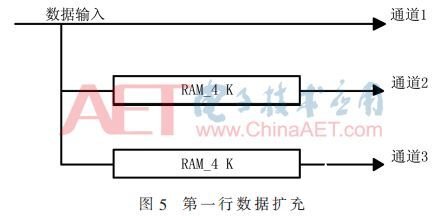

数据缓存模块的功能是将1路12 bit数据流,经过缓存和时序调整调整为3路并行的12 bit数据流。该模块使用两个深度为4 K,宽度为12 bit的读优先RAM,分别用来存储一行有效图像数据。根据行同步信号Hsync和场同步信号Vsync来判断传感器采集回的数据是否有效。

每当Hsync的一个上升沿到来时,锁存输入的数据,得到每行数据的第一个像素。经过计数后,再次锁存每行数据的最后一个像素。输入的数据延时一个时钟,同时把锁存的首位数据和末位数据与输入数据组合,形成一路新的数据流,如图4所示。由于RAM_4 K用于缓存一行扩充数据,因此图像数据的宽度需要小于4 094,否则会造成数据丢失。

数据缓存模块的一个关键信号是行计数信号,当一帧图像数据到来即Vsync的一个上升沿到来时,行计数信号清零,每次Hsync的上升沿到来时,行计数加1。由于需要对数据进行扩充,因此第一行和最后一行数据做特殊处理。当第一行组合数据到来时,同时存储进两个RAM中,此时3个输出通道无输出。当第二行组合数据到来时,1通道输出第二行数据,2通道和3通道输出第一行数据,如图5所示。

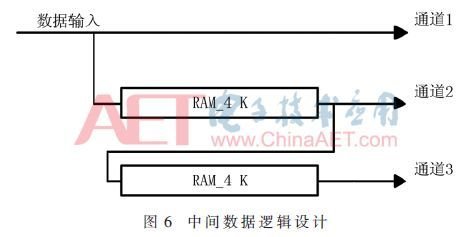

中间数据到来时,延时后输入1通道,且作为RAM1的输入。RAM1的输出同时输入至RAM2中。在数据输入的同时,将上次存入RAM的数据读出。这样当第N行数据到来时,1通道输出第N行数据,2通道输出第N-1行数据,3通道输出N-2行数据,即完成三行数据的同步输出,逻辑图如图6所示。

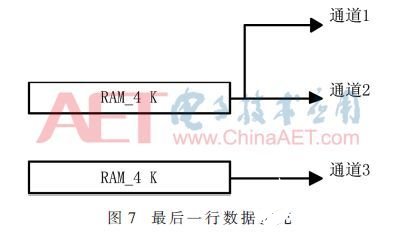

当最后一行数据输入完成后,开始对其进行扩充。此时Data_in为无效输入,并且RAM1输出为最后一行数据,同时赋值给1通道和2通道,RAM2输出倒数第二行数据,赋值给3通道,完成最后一行数据的扩充,如图7所示。

经过RAM缓存后的数据输出受RAM使能控制,由于RAM缓存的图像数据是扩展后的数据,RAM的使能信号要在行同步信号的基础上扩展两个时钟。三个通道的信号要经过适当的延时实现数据的同步。

3.2 权重生成模块设计

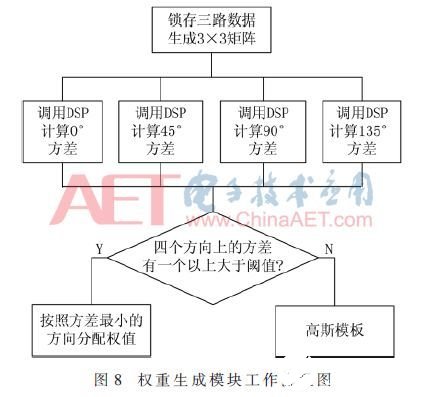

权重生成模块的目的是检测滤波窗口的中心像素点是平滑区域还是边缘区域,并根据检测结果生成相应的加权系数[6],其工作流程如图8所示。

该模块由加法器、减法器和乘法器构成,数据缓存模块输出的三行数据分别进行三次锁存,得到窗口内9个像素点的灰度值Pix0~Pix8。其中Pix3~Pix5作为水平方向;Pix2、Pix4、Pix6作为45°方向;Pix1、Pix4、Pix7作为90°方向;Pix0、Pix4、Pix8作为135°方向,分别计算方差。求灰度和时,中心像素点Pix4权重为2,另外两个点权重为1。这样计算标准差时,只需将灰度和通过两个移位寄存器即可。方差计算完成后,根据方差生成相应的权重模板及归一化系数,作为后续处理的参数。为保证处理过程流水线化,此模块通过四路并行计算方差,因此占用了较多DSP资源。

3.3 加权求和模块设计

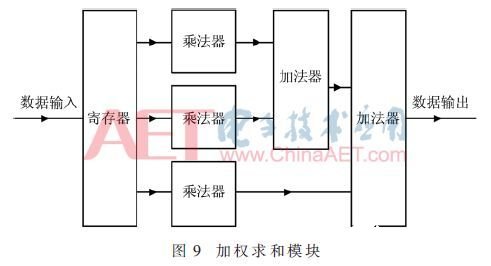

加权求和模块的功能实现同一行的三个像素点的加权运算。该模块由3个乘法器及两个加法器组成,如图9所示。一路数据输入后,经过三次锁存,得到同一行的3个相邻像素点。同时输入乘法器,进行加权运算,权重由权重生成模块给出。运算完毕后把两个乘法器的运算结果输入加法器进行求和运算,再把得到的结果与另一个乘法器得到的结果输入下一级加法器进行求和,得到同行3个像素点的加权求和输出,如图9所示。加权求和模块共调用三次,完成三路数据的同步加权求和运算。

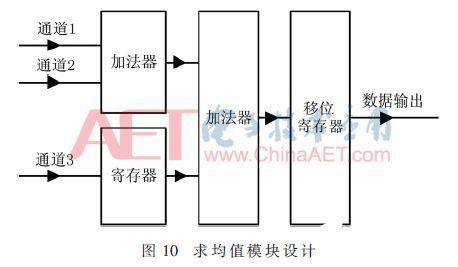

3.4 求均值模块设计

求均值模块调用了两个加法器实现三路同步数据的求和运算。通过移位寄存器来计算输出的均值。当归一化系数分别为4和16时,加法器输出数据经过2个或4个向右的移位寄存器输出,如图10所示。

12 bit数据经过乘法器、加法器的运算后,变成24 bit数据,但是有效数据位不变,只需取低12 bit即可。

4 仿真及实验结果分析

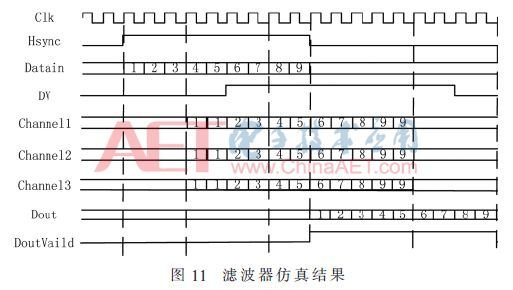

在ISE逻辑仿真时赋值给该模块不同的图像参数,验证模块的正确性和可配置性。以9×5分辨率的图像为例:输入图像有效数据为1~9,数据缓存模块输出应为扩充后的并行3行数据,经过权重生成后,加权求和输出,如图11所示。

在仿真过程中,根据数据输入与数据输出的延迟判断,在输入图像宽度为2 048像素情况下,处理延时为42.04 μs,满足实时性要求。

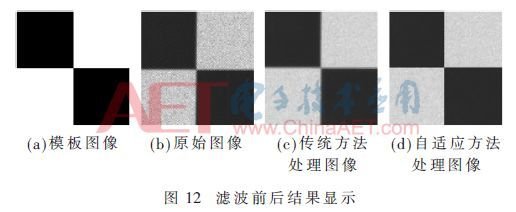

实验对象选择ON公司的CMOS图像传感器MT9P031,对采集到的2 048×1 944分辨率的图像进行预处理。结果如图12所示,其中图12(a)为模板图像,图12(b)为采集回的原始图像,图12(c)为传统加权均值滤波处理过的图像,图12(d)为本文方法处理后的图像。可以看到未处理图像的噪点较多,且纹理边缘有毛刺;经过传统加权均值滤波处理后,图像的噪点减少,纹理边缘毛刺消失,但比较模糊;使用本文方法处理后的图像噪点较少,同时边缘也更加清晰,图像质量得到明显改善。通过MATLAB对处理结果及原始图像进行均方差MES与峰值信噪比PSNR计算比较,结果见表1。

从表1中图像的客观指标可以看到,通过本文方法处理后的图像相较于传统加权均值滤波处理后的图像,其峰值信噪比提高1.04 dB。说明本文方法优于传统的加权均值滤波方法。

FPGA资源占用率见表2。由表2数据可知,除DSP资源外,本设计的资源占用率低,而一般图像采集系统对DSP需求不高,因此可以方便嵌入CMOS图像采集系统设计中。

5 结论

针对传统均值滤波处理图像时实时性差等特点,结合FPGA并行处理数据的高效性,实现图像的自适应加权均值滤波处理,具有可配置、低延时的特点。实验结果表明,本设计能够在不影响数据传输速度的情况下,嵌入图像采集系统中,形成一套流水线,并有效提高CMOS图像传感器采集图像的质量。

参考文献

[1] 徐琳亮.CMOS图像传感器预处理数字电路的设计与实现[D].成都:电子科技大学,2017.

[2] 陈家益,黄楠,熊刚强,等.基于置信区间的自适应加权均值滤波算法[J].南京理工大学学报,2017,41(3):307-312.

[3] 张文娟,康家银.一种用于图像降噪的自适应均值滤波算法[J].小型微型计算机系统,2011,32(12):2495-2498.

[4] 杨樊,韩艳丽.一种基于极值的自适应均值滤波算法[J].红外与激光工程,2006(S4):116-120.

[5] 彭宏,赵鹏博.边缘检测中的改进型均值滤波算法[J].计算机工程,2017,43(10):172-178.

[6] 张文娟,康家银.一种用于图像降噪的自适应均值滤波算法[J].小型微型计算机系统,2011,32(12):2495-2498.

[7] 郭贝贝,易三莉,贺建峰,等.改进的非局部均值滤波算法[J].计算机工程,2016,42(7):227-231.

[8] 李佐勇,汤可宗,胡锦美,等.椒盐图像的方向加权均值滤波算法[J].中国图象图形学报,2013,18(11):1407-1415.

作者信息:

武昊男,储成群,任勇峰,焦新泉

(中北大学 电子测试技术国家重点实验室,山西 太原030051)

-

解决方案丨EasyGo新能源系统实时仿真应用2024-10-18 1398

-

基于FPGA的实时边缘检测系统设计,Sobel图像边缘检测,FPGA图像处理2024-05-24 3452

-

基于FPGA的图像实时处理系统设计2023-06-15 3387

-

FPGA设计中 Verilog HDL实现基本的图像滤波处理仿真2021-07-13 3739

-

如何使用FPGA实现顺序形态图像处理器的硬件实现2021-04-01 1196

-

如何使用FPGA实现实时图像预处理技术在汽车夜视系统中的应用2021-03-18 1106

-

如何使用FPGA和DSP实现CCD图像相关处理系统2021-02-05 1259

-

如何使用FPGA实现实时图像增强算法2021-02-03 1468

-

FPGA实时视频图像处理系统的原理是什么?2019-08-22 3436

-

一种基于FPGA的实时视频图像处理算法研究与实现2019-06-28 4007

-

基于FPGA的小波图像实时处理方法2016-09-22 796

-

实时图像增强算法改进及FPGA实现2016-09-17 695

-

MATLAB信号处理仿真实验代码包2013-09-23 1333

-

实时图像边缘检测的设计及FPGA实现2011-12-22 608

全部0条评论

快来发表一下你的评论吧 !