基于Digilent的Arty Artix-35T FPGA开发板的DDR3读写控制

描述

将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。

本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。

软件使用Vivado 2018.1。

参考工程:ddr3_test。

第五篇:mig读写时序下板实现

1顶层文件和约束文件

ddr3_test.v

参见参考工程:ddr3_test。

ddr3.xdc

1. set_property PACKAGE_PIN E3 [get_ports clk]

2. set_property IOSTANDARD LVCMOS33 [get_ports clk]

3. set_property PACKAGE_PIN D9 [get_ports reset]

4. set_property PACKAGE_PIN E1 [get_ports init_calib_complete]

5. set_property IOSTANDARD LVCMOS33 [get_ports init_calib_complete]

6. set_property IOSTANDARD LVCMOS33 [get_ports reset]

2 下板实现读写时序

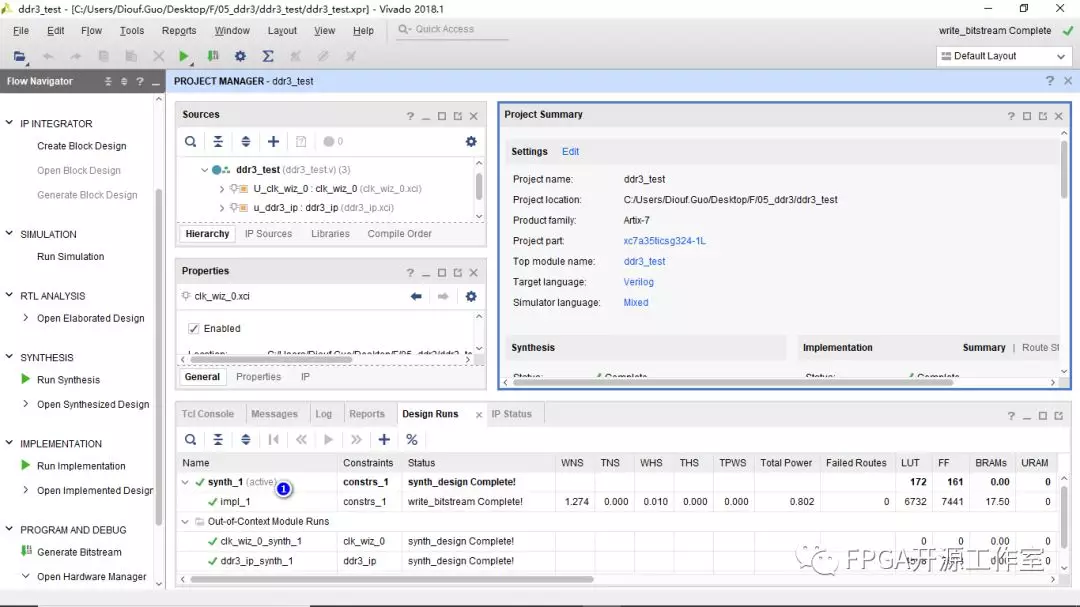

1>①完成综合和实现

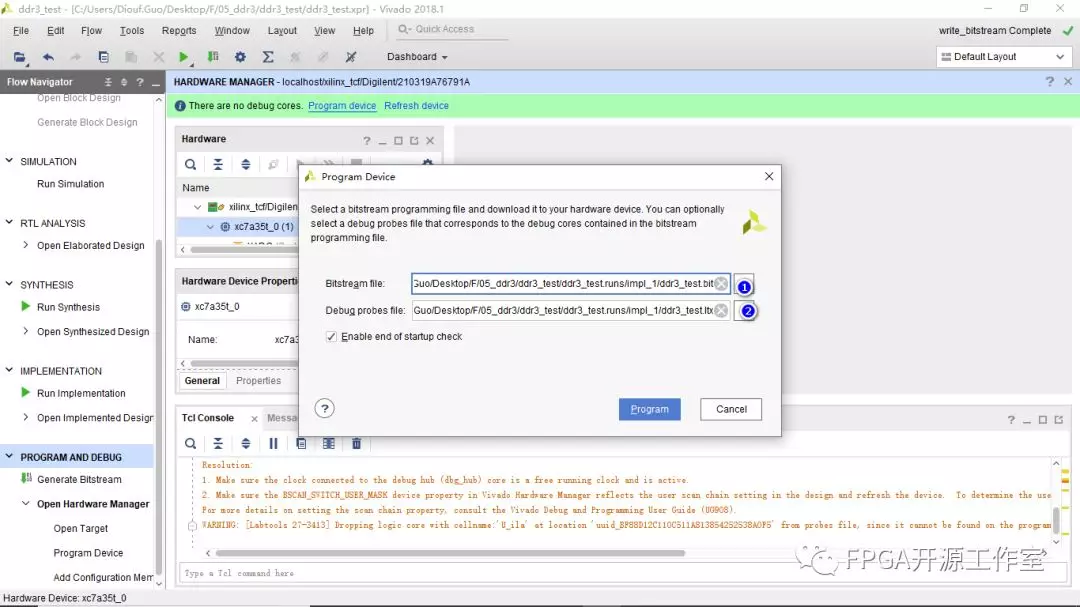

2>下载bit文件和debug文件。

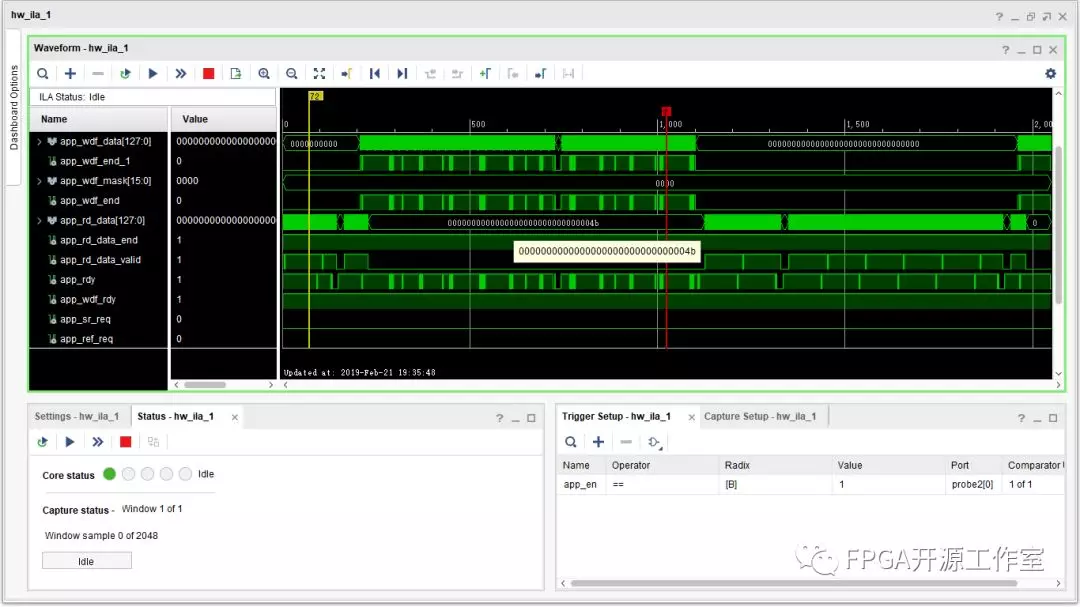

3>下载完成,查看波形。

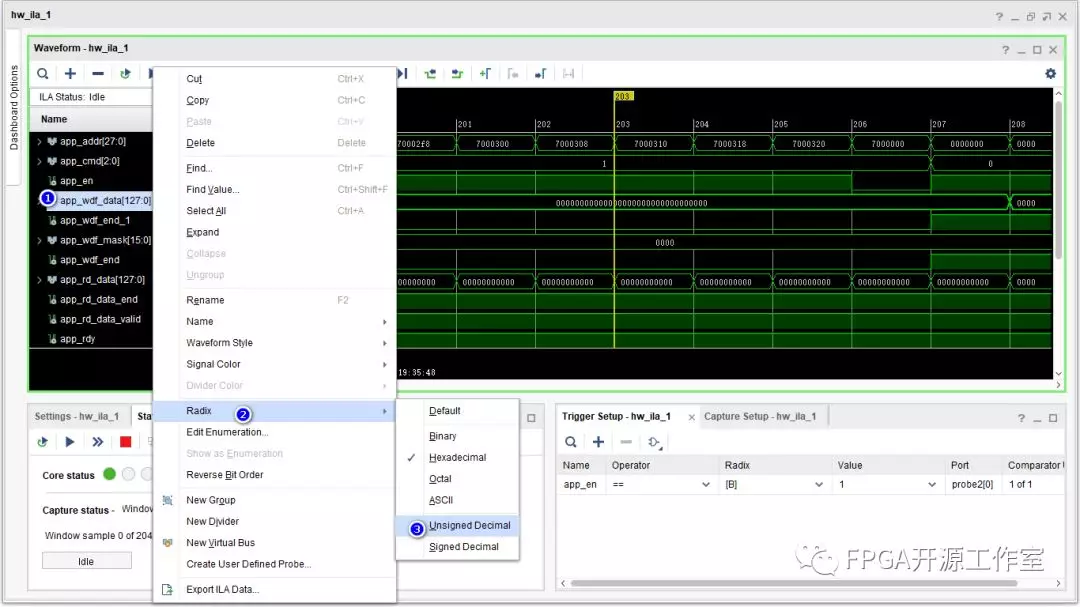

4>将app_wdf_data数据格式改为Unsigned Decimal。

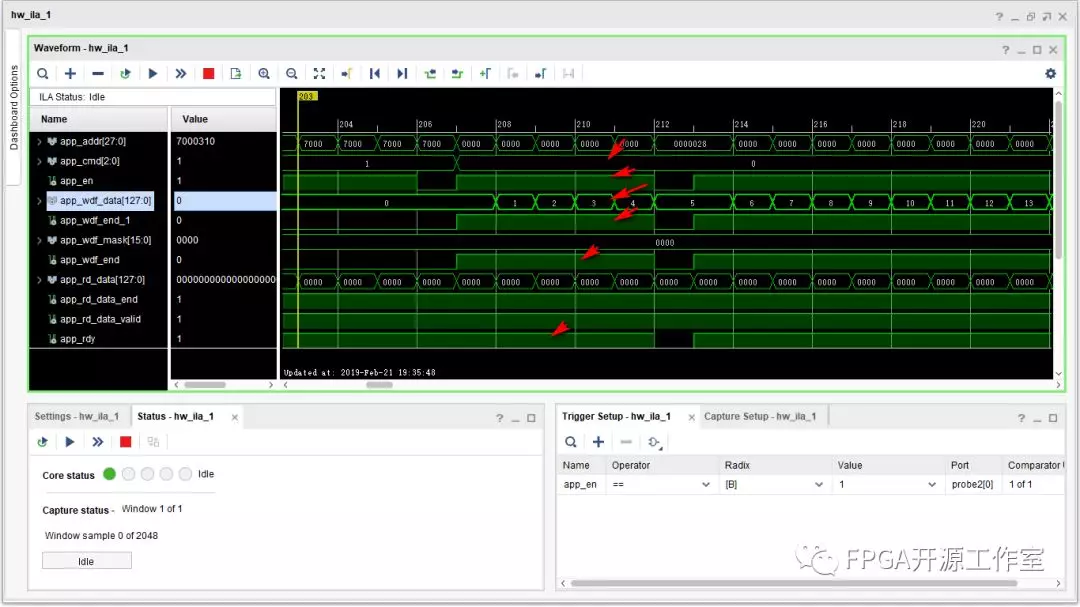

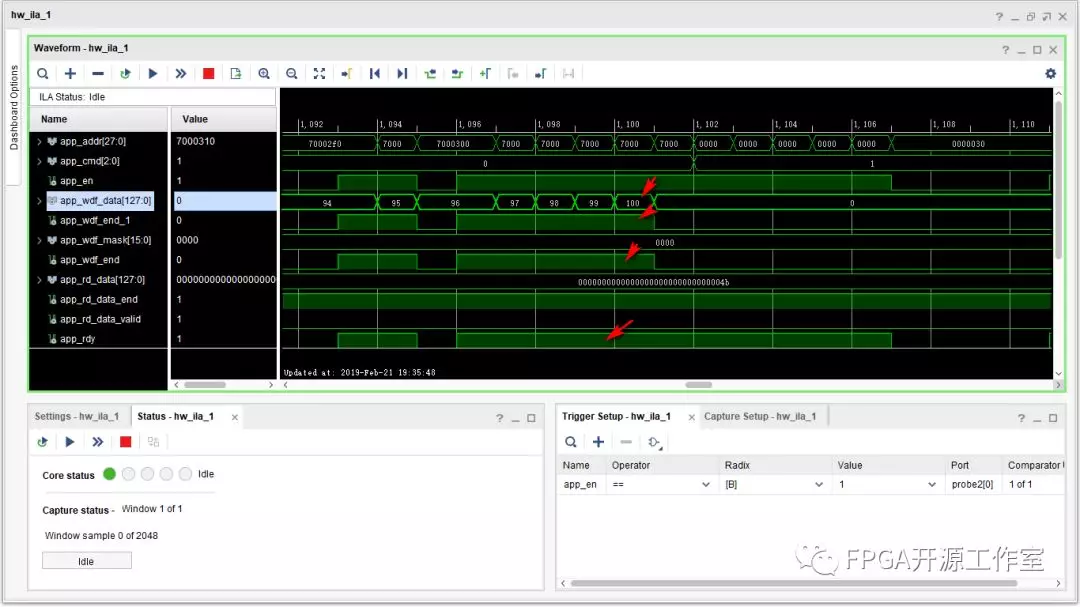

5>查看写时序。

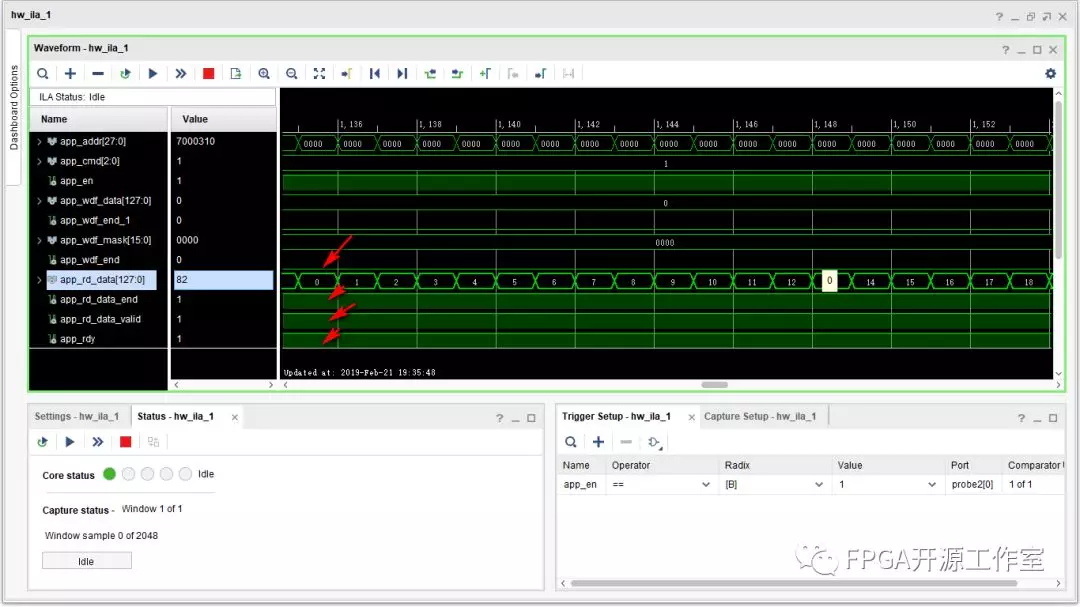

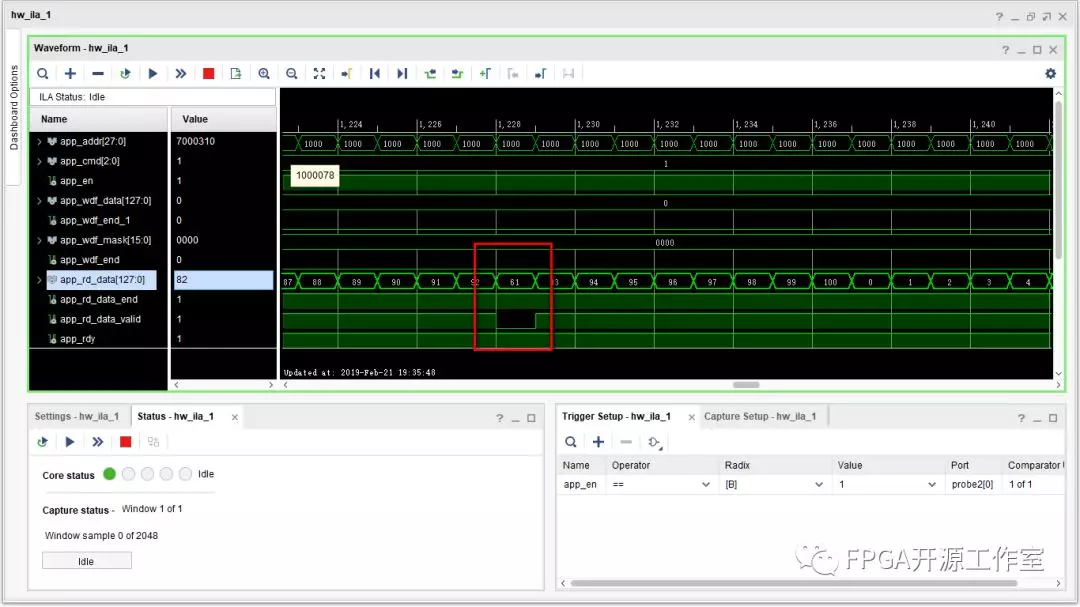

6>查看读时序。

基于xilinx mig ip对ddr3读写验证完成。

编辑:hfy

-

fpga开发板 璞致Artix-7系列之PA-Starlite Artix7 A735T 75T 100T 200T开发板用户手册-学习板2025-10-14 3155

-

基于AXI总线的DDR3读写测试2023-09-01 7934

-

【Combat FPGA开发板】配套视频教程——DDR3的读写控制2021-05-06 3152

-

基于Arty Artix-35T FPGA开发板的DDR3和mig介绍2021-01-01 5647

-

通过Arty Artix-35T FPGA开发板创建mig IP2020-12-16 2903

-

digilent Spartan-7开源创客开发板介绍2019-11-19 3705

-

基于Artix-7 35T的评估套件的ARTY介绍2018-11-27 3151

-

基于FPGA的DDR3多端口读写存储管理的设计与实现2017-11-18 8212

-

开发者福利 一文带你了解Digilent Arty S7 FPGA开发板2017-09-27 9237

-

【DIGILENT挑战赛】+电子相框2017-05-03 3563

-

Digilent公司发布新款FPGA开发板2017-02-09 1871

-

7 Arty开发板上实现四核8051处理器2017-02-08 714

-

Arty Board Artix-7 FPGA开源创客开发板用户手册2016-08-04 2616

全部0条评论

快来发表一下你的评论吧 !