通过Arty Artix-35T FPGA开发板创建mig IP

描述

讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。

本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。

软件使用Vivado 2018.1

第二篇:mig IP的创建

1 DDR3

Digilent的Arty Artix-35T FPGA开发板板载MT41K128M16JT-125 DDR3基本信息如下表所示。

2 mig IP的创建

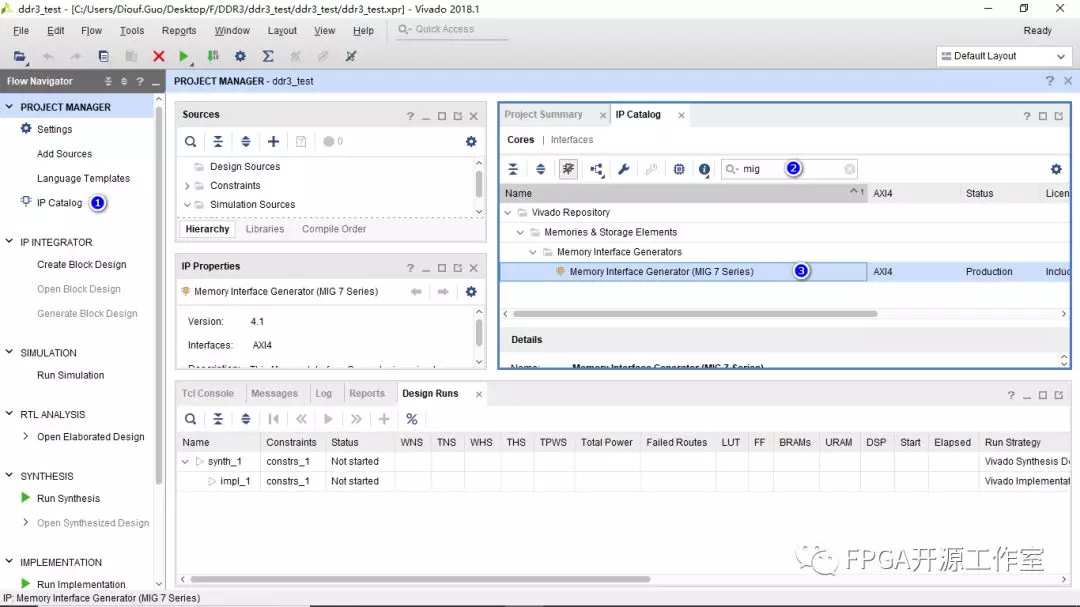

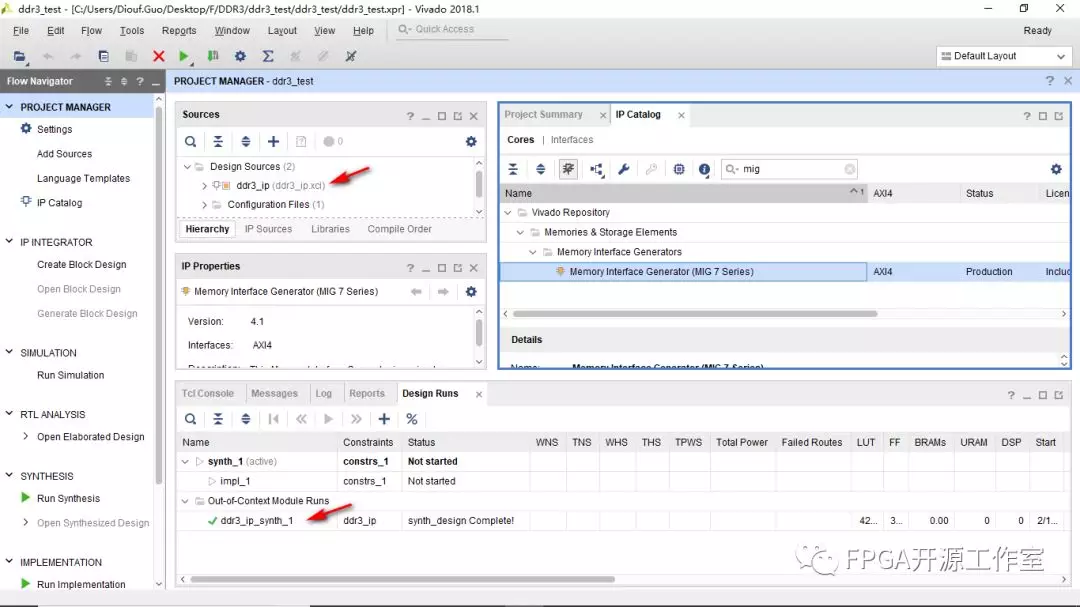

1>点击IP Catalog ->搜索mig->双击Memory Interface Generator(MIG 7 Series)

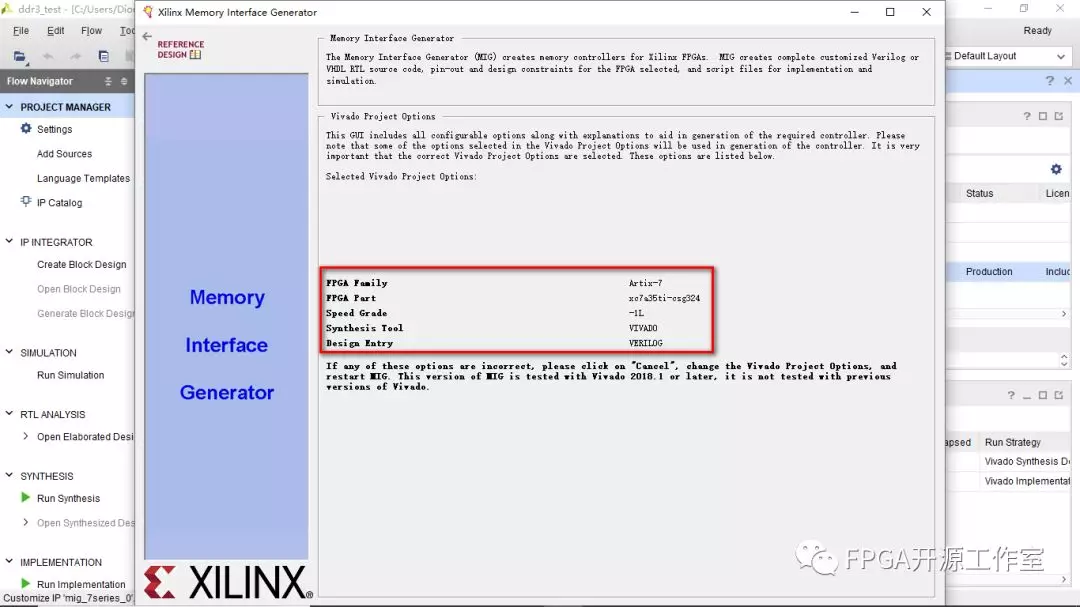

2>打开后可以看到一些基本信息

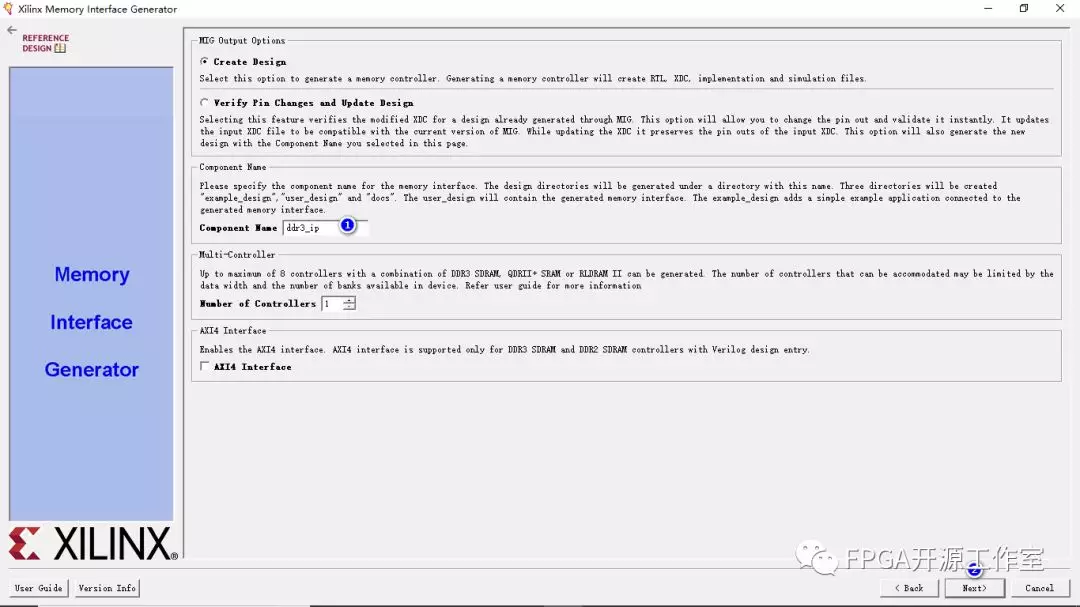

3> Enter a component name in the Component Name field ->Next

Component name(组件名称):ddr3_ip

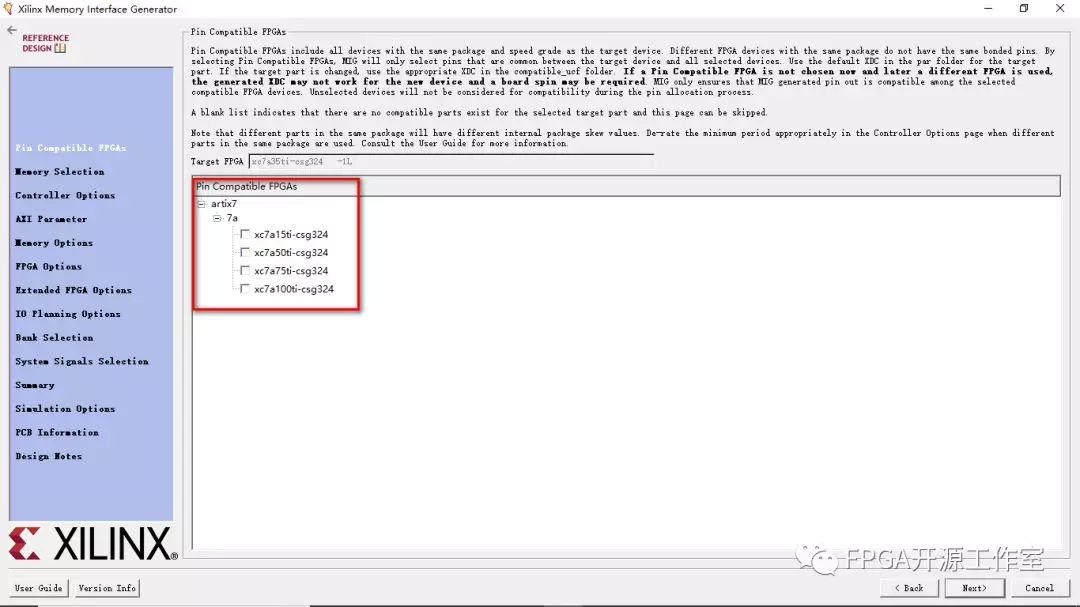

4>这里我们不做兼容性选择,直接下一步

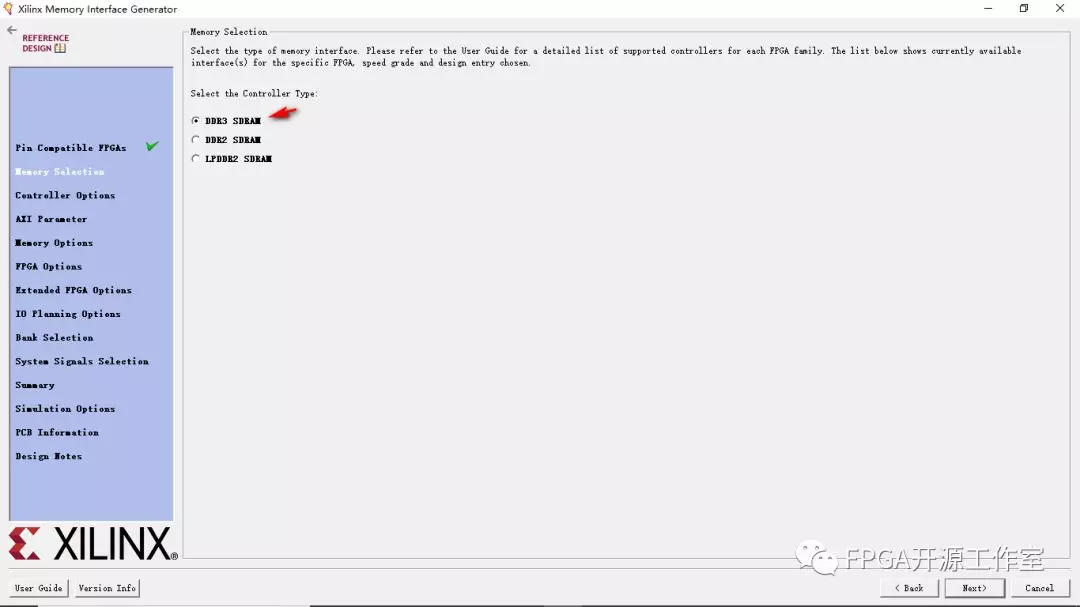

5>控制类型选择DDR3 SDRAM

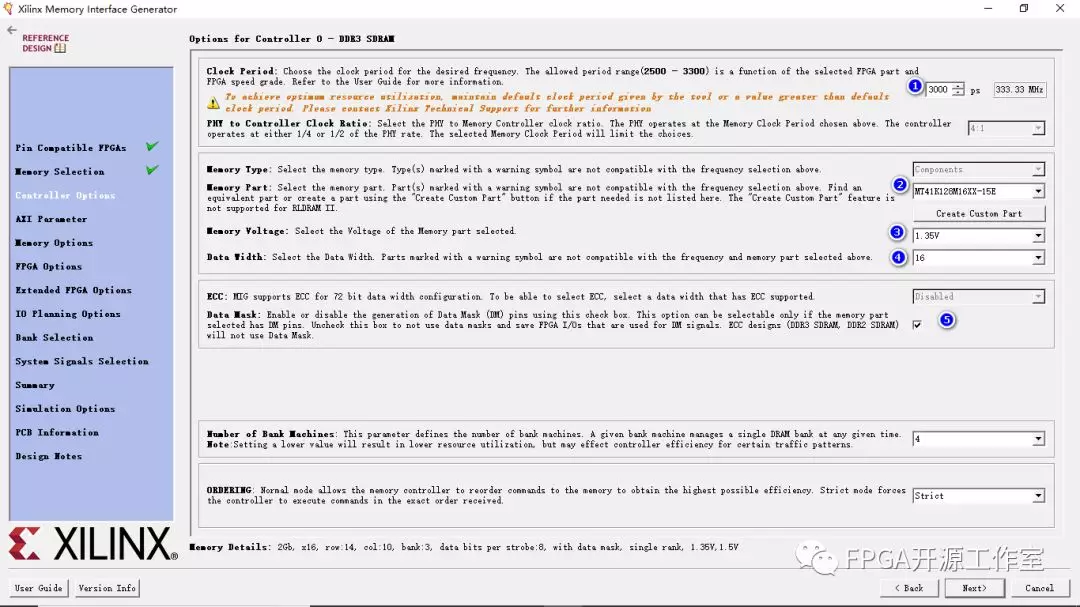

6>①Clock Period:(此功能表示所有控制器的工作频率,频率模块受所选FPGA和器件速度等级等因素的限制。) 3000ps(333.33MHZ)。

②PHY to Controller Clock Ratio :(此功能确定物理层(存储器)时钟频率与控制器和用户界面时钟频率的比率。 由于FPGA逻辑时序限制,2:1比率会降低最大存储器接口频率。 2:1比率的用户界面数据总线宽度是物理存储器接口宽度宽度的四倍,而4:1比率的总线宽度是物理存储器接口宽度的八倍。 2:1比率具有较低的延迟。 4:1的比率是最高数据速率所必需的)4:1。

③Memory Type:此功能选择设计中使用的内存部件类型。

④Memory Part :此选项为设计选择内存部件。 选择可以从列表中创建或者可以创建新部件。MT41K128M16XX-15E。

⑤Memory Voltage:根据设计原理图1.35V。

⑥Data Width:(可以根据之前选择的存储器类型在此处选择数据宽度值。 该列表显示所选部件的所有支持的数据宽度。 可以选择其中一个数据宽度。 这些值通常是各个器件数据宽度的倍数。 在某些情况下,宽度可能不是精确倍数。 例如,16位是x16组件的默认数据宽度,但8位也是有效值。)16。

⑦Data Mask:(选择时,此选项会分配数据屏蔽引脚。 应取消选择此选项以释放数据屏蔽引脚并提高引脚效率。 此外,对于不支持数据掩码的内存部分禁用此功能。)勾选。

NXET。

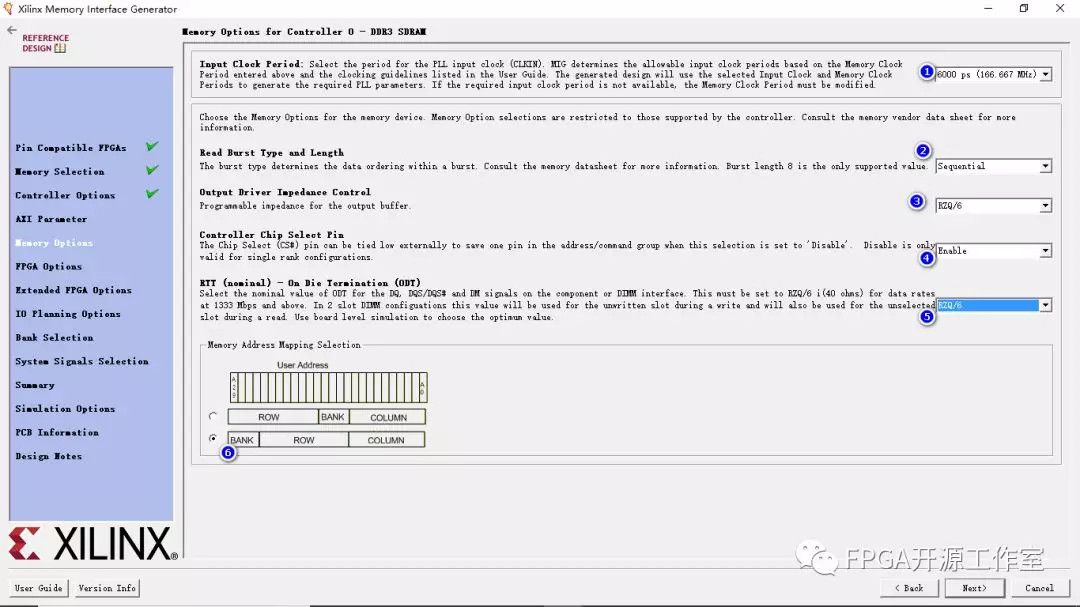

7>①Input clock Period:6000ps(166.667MHZ)。

②Read Burst Type and Length:Sequential。

③Output Driver Impedance Control:RZQ/6。

其他默认,NEXT。

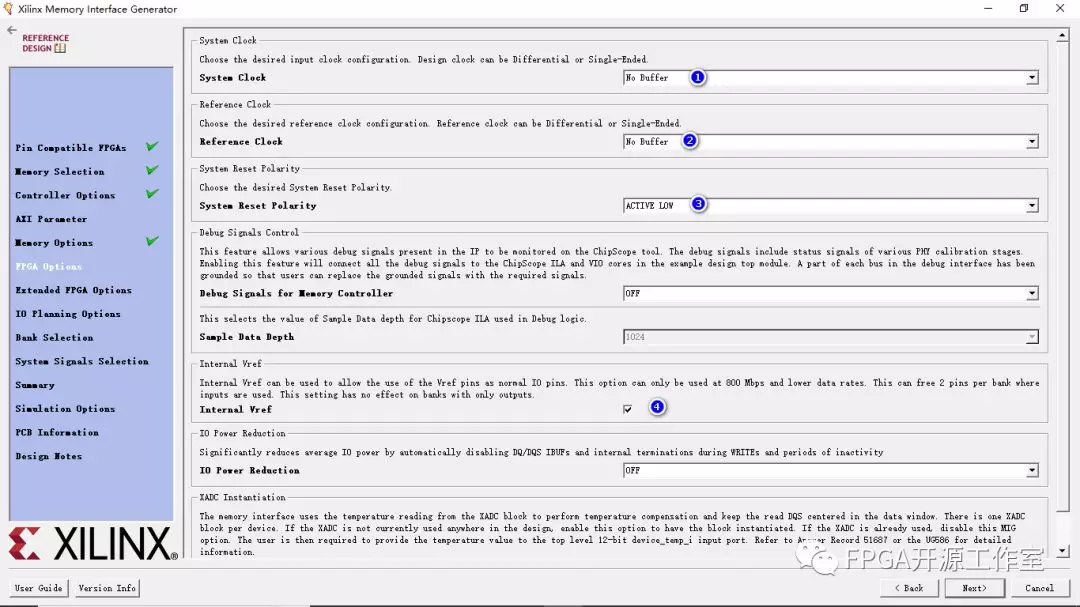

8>①System Clock :(此选项为sys_clk信号对选择时钟类型(单端,差分或无缓冲)。 选择No Buffer选项时,IBUF原语不会在RTL代码中实例化,并且不会为系统时钟分配引脚。 )No Buffer。

②Reference Clock :(此选项为clk_ref信号对选择时钟类型(单端,差分,无缓冲或使用系统时钟)。 当输入频率介于199和201 MHz之间时(即输入时钟周期介于5,025 ps(199 MHz)和4,975 ps(201 MHz)之间),将显示Use System Clock(使用系统时钟)选项。参考时钟频率基于数据速率 并注意添加MMCM以创建高于1,333 Mb / s的适当ref_clk频率。当选择No Buffer选项时,IBUF原语不会在RTL代码中实例化,并且引脚不会分配给参考时钟。)No Buffer。

③System Reset Polarity:(可以选择系统复位(sys_rst)的极性。 如果选项选择为低电平有效,则参数RST_ACT_LOW设置为1,如果设置为高电平 - 高,则参数RST_ACT_LOW设置为0。)ACTIVE LOW。

④Debug Signals Control:选择此选项可以将校准状态和用户端口信号端口映射到example_top模块中的ILA和VIO。 这有助于使用Vivado Design Suite调试功能监控用户界面端口上的流量。 取消选择Debug Signals Control选项会使example_top模块中的调试信号保持未连接状态,并且IP目录不会生成ILA / VIO模块。 此外,始终禁用调试端口以进行功能仿真。OFF。

⑤Sample Data Depth:此选项选择Vivado调试逻辑中使用的ILA模块的样本数据深度。 当“内存控制器的调试信号”选项为“开”时,可以选择此选项。

⑥Internal Verf:(内部VREF可用于数据组字节,以允许使用VREF引脚进行正常的I / O使用。 内部VREF仅应用于800 Mb / s或更低的数据速率。)勾选。

其他默认,NEXT。

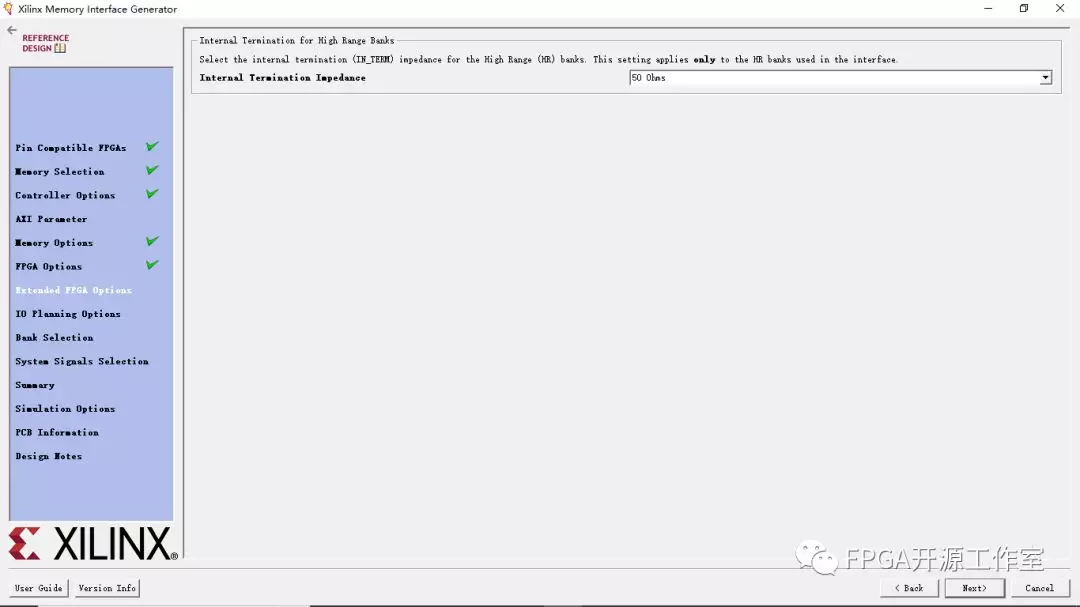

9>默认,NEXT。

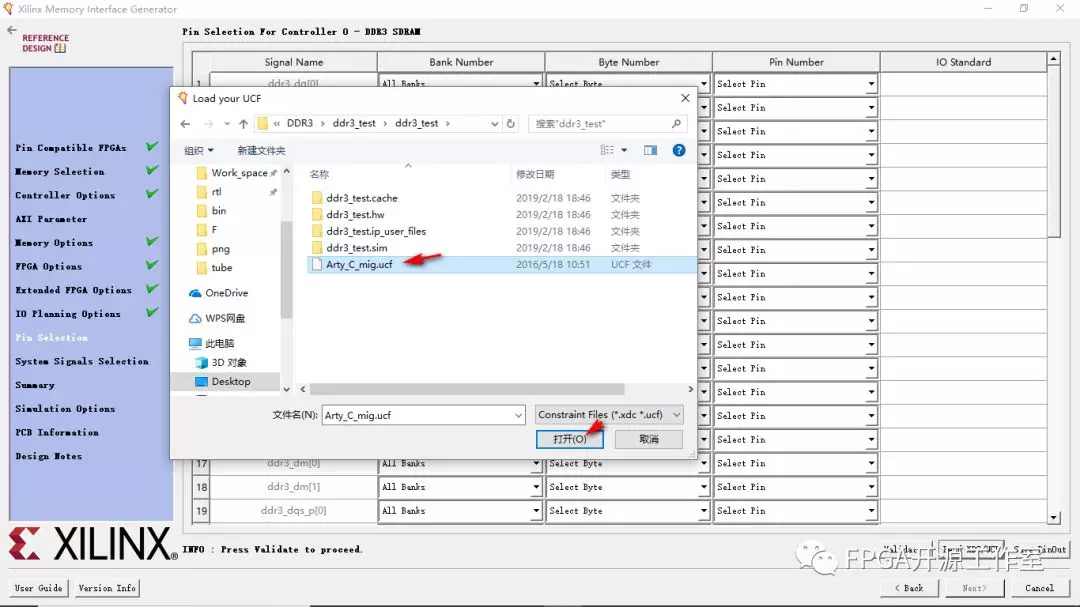

10>选择Fixed Pin Out。我们的原理图管脚已经确定无需从新设计。

11>点击Read XDC/UCF,这里DDR3管脚支持两种约束文件。

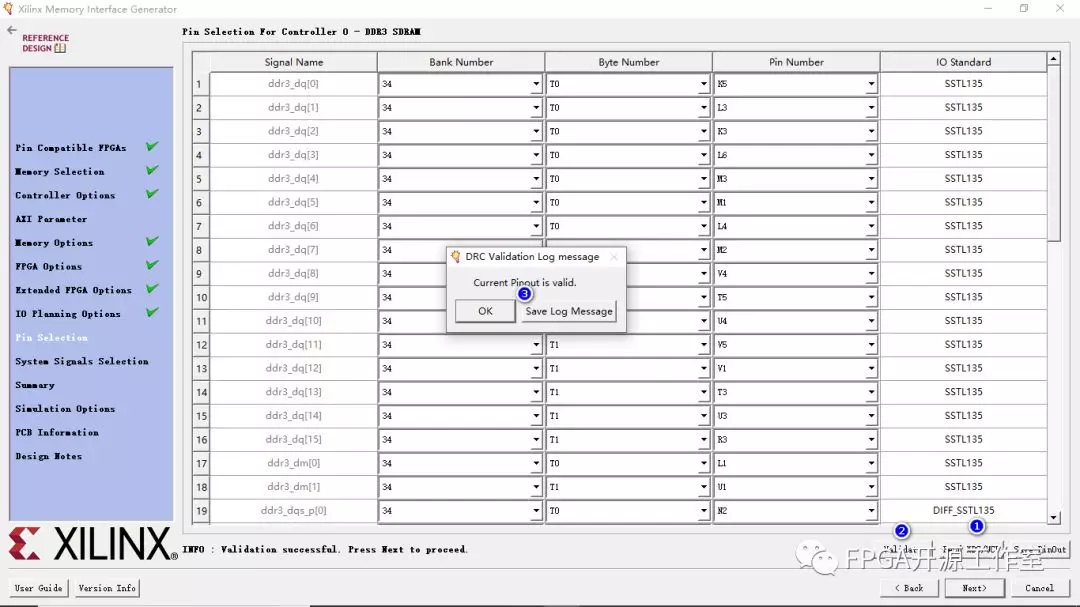

12>点击Validate验证管脚约束是否有错误。验证通过NEXT。

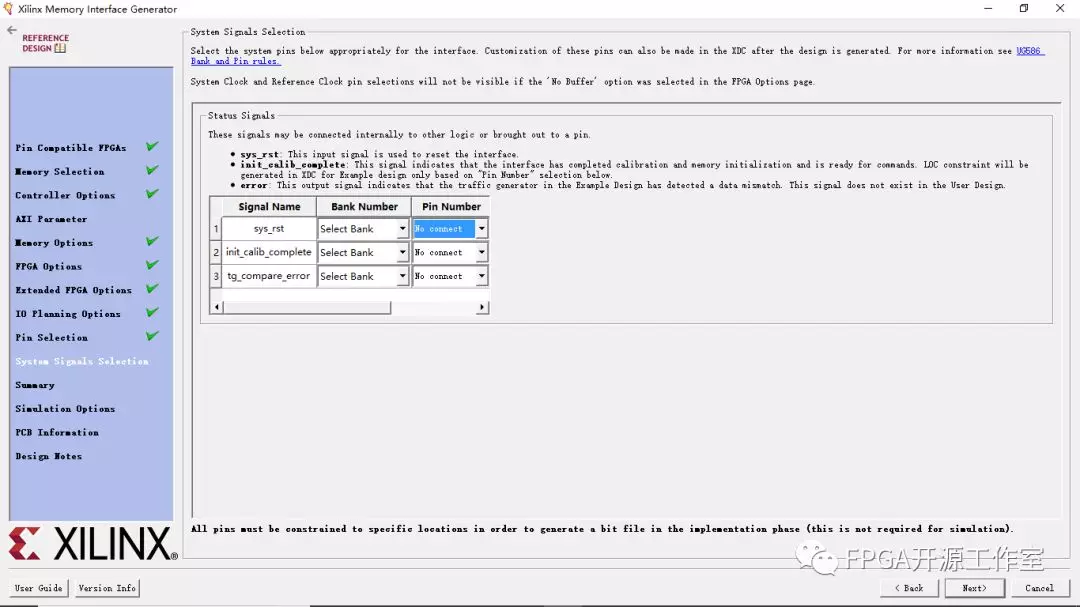

13>默认,NEXT。

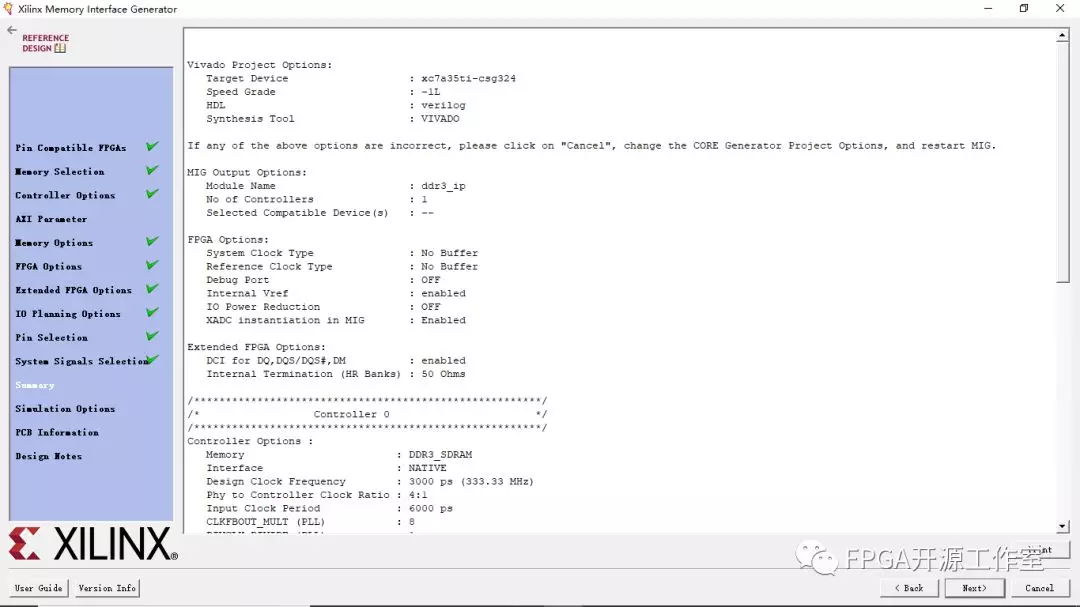

14>Next。

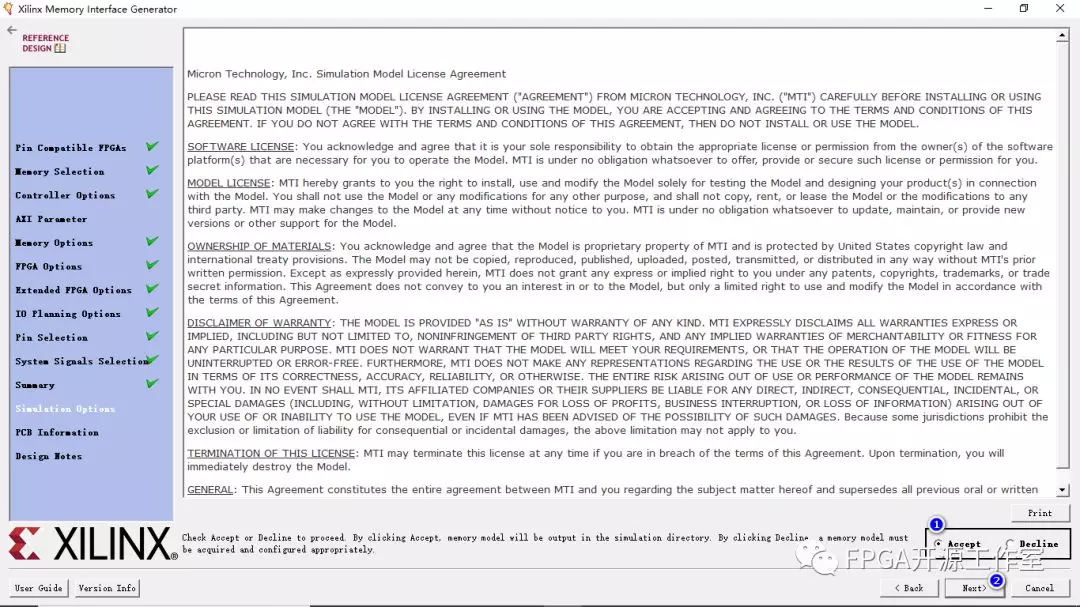

15>Accept,Next。

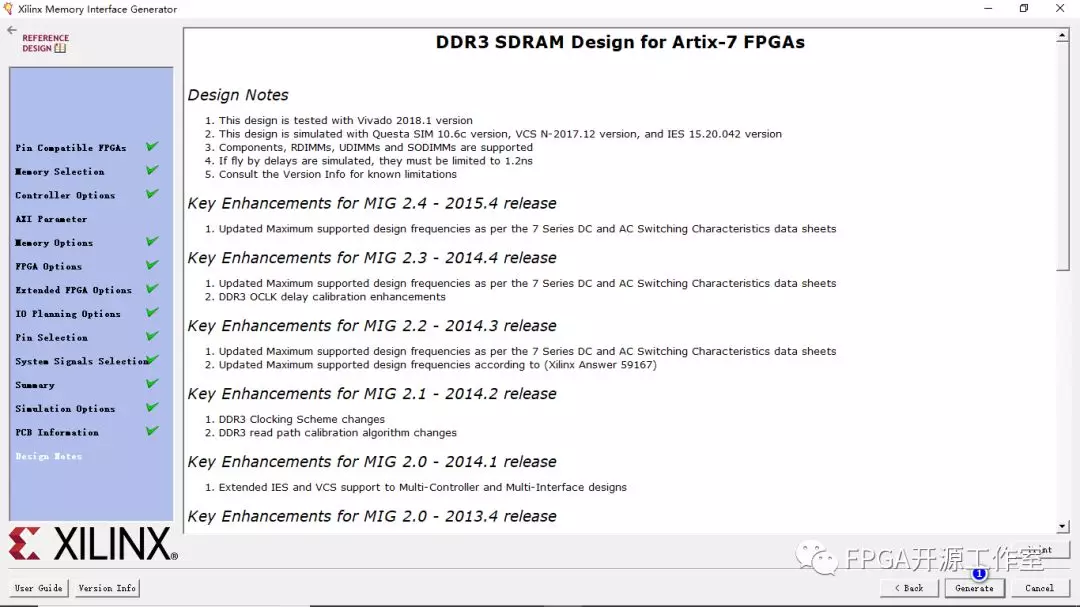

16>Generate

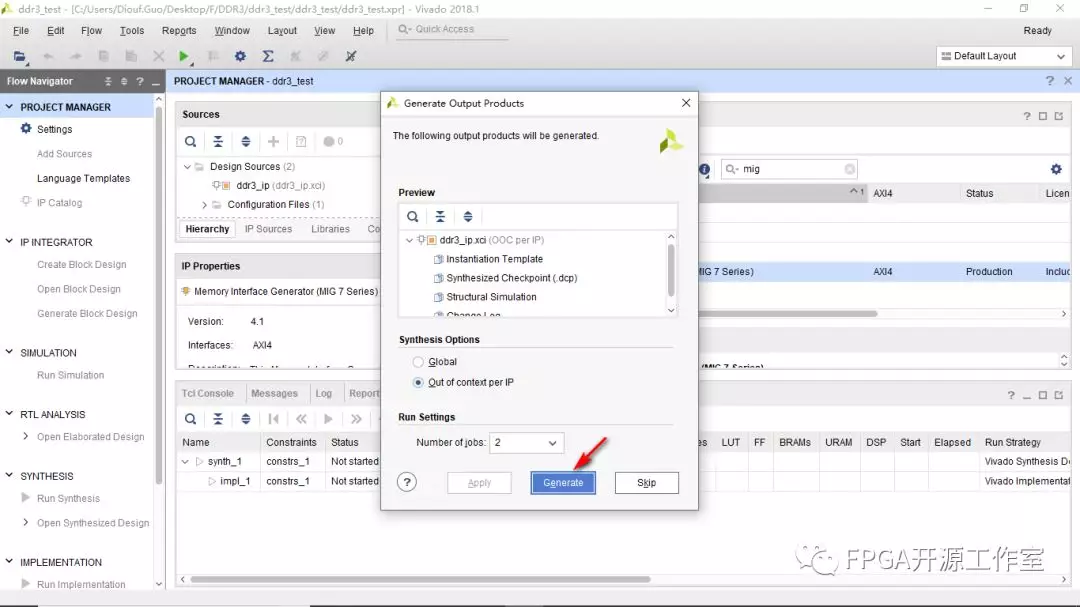

17>Generate

18>至此我们的mig IP创建完成。

编辑:hfy

-

fpga开发板 璞致Artix-7系列之PA-Starlite Artix7 A735T 75T 100T 200T开发板用户手册-学习板2025-10-14 3034

-

FPGA核心板 Xilinx Artix-7系列XC7A100T开发平台,米尔FPGA工业开发板2024-05-31 1441

-

arty A7 35T开发板用nuclei studio下载程序出错是为什么?2023-08-16 558

-

一款售价约280美元的Xilinx Artix-7100T FPGA开发板2022-11-17 2416

-

基于Arty Artix-35T FPGA开发板的DDR3和mig介绍2021-01-01 5613

-

基于Digilent的Arty Artix-35T FPGA开发板的DDR3读写控制2020-12-15 3903

-

基于Artix-7 35T的评估套件的ARTY介绍2018-11-27 3120

-

开发者福利 一文带你了解Digilent Arty S7 FPGA开发板2017-09-27 9196

-

7 Arty开发板上实现四核8051处理器2017-02-08 700

-

Artix-7 FPGA AC701开发板-板载Debug Checklist2016-08-08 2179

-

Arty Board Artix-7 FPGA开源创客开发板用户手册2016-08-04 2600

-

Nexys™4_Artix-7_FPGA_开发板原理图2016-08-03 1865

-

Meet ARTY@$99:Artix-7 35T开发套件开箱视频2016-07-26 3823

全部0条评论

快来发表一下你的评论吧 !