多用途软件无线电系统的5G设计解决方案

描述

本文旨在让无线电工程师熟悉一种现成的多用途软件无线电(COTS SDR)平台,该平台可以缩短5G的开发时间。

COTS SDR传统上一直用于军用雷达和通信应用中,以获得高性能和设计灵活性。最新的COTS SDR产品提供了含有集成化I/O、ARM处理器和大型FPGA的解决方案,还含有用于访问、路由和处理数字数据的知识产权(IP)。这些特性,与优越的信号完整性、相位相干采样和多信道收发机相结合,使得COTS SDR系统成为5G开发平台的一种理想选择。

COTS SDR的定义

为清晰起见,本文的每一节都划分成了讨论硬件、固件和软件的各小节。硬件包括SDR印制电路板(PCB)和支持组件;固件包括用于逻辑和数字信号处理(DSP)功能的FPGA内部代码;软件是用固件控制FPGA并执行任意额外DSP功能的C代码。

硬件

SDR取代了由RF滤波器、模拟下变频器(即本振和混频器)、带通滤波器和解调器构成的传统模拟系统(见图1a)。这些固定的模拟系统局限于特定的功能,如AM或FM无线电。

图1 传统模拟通信接收机(a)与SDR接收机(b)、SDR发射机(c)的对比

而SDR利用了可编程DSP技术,可以灵活应对当今无线通信中日益增长的复杂性、精度和带宽问题。要使用SDR,接收和发射功能都需要在天线和DSP之间进行数据转换1。SDR接收机使用一只模数转换器(ADC)将来自天线的RF信号转换成数字采样,并使用后续的DSP运算从信号中提取所需的信息(见图1b)。SDR发射机接收要发射的数字信息,并执行必要的DSP运算以生成用于数模转换器(DAC)的数字采样,DAC的输出驱动一只功放以传送到天线(见图1c)。因为这些无线电是软件定义的,它们能够在传输过程中在数微秒内用新的参数完成编程,或者通过从内部或外部存储器简单地加载新的固件实现针对不同目的的新配置。

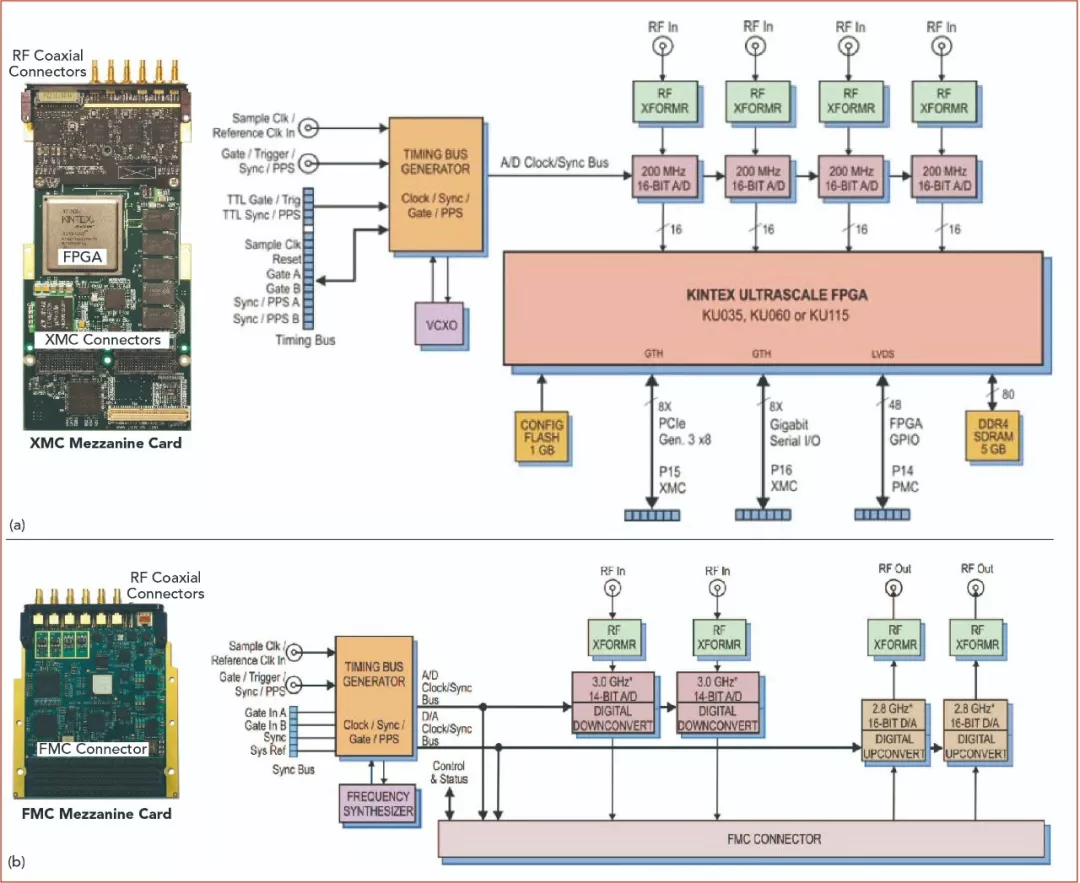

SDR通常是在一种称之为“夹层卡(mezzanine card)”的特种PCB上实现的。当前一代是织构交变的夹层卡(XMC)或FPGA夹层卡(FMC)。图2显示了XMC和FMC及其相应的功能框图。图2a是有4个200MHz ADC通道的一块XMC卡,图2b是有2个3GHz ADC通道和2个2.8GHz DAC信道的FMC卡。每块板都有一个用于可变采样率的含多bit分数合成器的精确定时系统,定时系统被锁定到一只板上的温控晶振(OCXO)或一个参考输入信号。这些定时系统通常接收来自网络时间协议服务器或GPS接收机的外部同步信号,以满足雷达或蜂窝系统的精确定时要求。ADC的相位相干采样、FPGA DSP数据同步和DAC信号传输也需要精确定时。

图2 XMC(a)、FMC(b)夹层卡及其功能框图

XMC ADC有200 MSPS的最大采样率,不用滤波即可捕获100 MHz的Nyquist带宽。数字无线电的一种常见技术是通过信号欠采样获得信道信息或中频(IF)带宽。欠采样允许一只较低采样率、较高动态范围的ADC捕获一个中心位于较高频率的窄带宽信号而不丢失信息。为了在这种情况下正确地工作,RF输入通道和ADC必须容下这些较高频率的信号。

在模数采样之后,下一级通常是数字下变频器(DDC),DDC进行频率转换和带宽缩减。DDC通常是在FPGA中以IP固件实现的。

固件

FPGA是由未连接的逻辑、算法和信号处理的构件组成的,这些构件用IP固件配置以执行特定的功能。虽然对于极端的编程灵活性很理想,但固件开发复杂。为了简化开发过程,一些COTS SDR制造商提供用于其电路板基本操作的FPGA IP。这通常包括了用于采集和传输数据的模拟和数字I/O功能,以及用于特定无线电功能的DSP IP,例如将数据传送到系统的DDC、滤波器、信道化器和引擎。

DDC功能需要3个IP构件:数控振荡器(NCO)本振、一个复数混频器和多个数字滤波器,以取代传统模拟无线电系统的功能(见图1)。DDC的调谐级使用一个复数数字混频器将感兴趣的频率转换到基带。由一只直接数字合成器(DDS) NCO驱动的一对乘法器,让用户能够将接收机“调谐”到所需的频率。采样信号接着通过一只低通有限脉冲响应(FIR)滤波器来对信号进行1/10抽取以适应一个有限的信道带宽。DDC的两个主要优点是:1/10抽取带来的更高的信噪比(SNR),以及调谐到信号窄带中心频率的能力。信号1/10抽取有效地降低了采样率并减少了不相关的白噪声,并且NCO能够精确地数字调谐到单个Nyquist区内的一个特定载波频率。

软件

尽管厂商提供的FPGA IP可能满足某个特定应用的指标,但系统的实现可能需要控制软件来操作无线电。FPGA IP需要从一个软件程序出发,跨过系统接口发出操作参数,软件程序通常被写成Windows或Linux环境下“C”可调用例程的电路板支持包(BSP)的函数。BSP包含库函数和预编译好的示例代码,可以运行它们来测试电路板功能。其中一个功能是命令ADC捕获数据并将其传输到FPGA,以便DDC中的进一步处理。处理后的数据可以存储在存储器中,或者传输到DAC以转换回一个模拟信号并输出以进行发射。这是使用BSP软件库函数和驱动程序开发的一个软件程序的一例。如果用户创建了任何新的FPGA IP,则必须编写其它的控制软件并将其纳入BSP包中。

最新的COTS SDR技术

硬件

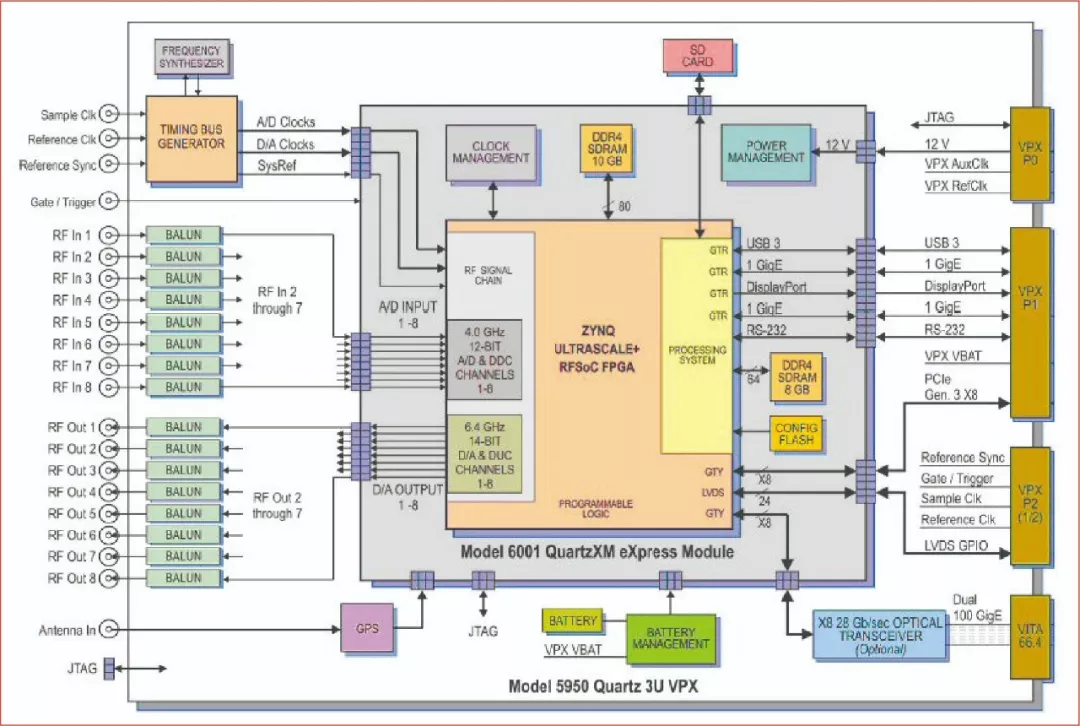

过去10年中,像Xilinx这样的FPGA制造商一直在通过减小硅工艺节点的尺寸来改进技术,减少了器件的尺寸、重量和功率(SWaP)。2008年底,Xilinx Virtex-6系列采用了一种40 nm工艺制造,每个FPGA上有平均2000个DSP切片。2017年,Ultrascale系列采用了20 nm工艺,FPGA DSP切片增加到了约5500个。Xilinx最新的片上系统(SoC) RFSoC,在同一块芯片上包含了FPGA结构和ARM处理器、ADC和DAC。16 nm工艺已经在每个器件上实现了超过4200个DSP切片、4个1.5 GHz的A53 ARM处理器、2个600 MHz的R5 ARM处理器、8个4 GHz的12位ADC和8个6.4 GHz的14位DAC。

图3显示了使用Xilinx RFSoC的一个COTS SDR实例的功能框图,Xilinx RFSoC是Pentek公司5950 3U VPX板的核心元件。包含RFSoC的中心区域是可以插入一个3U VPX载体的全连接的模块上系统(SoM)。同时,该器件可以像上一代FPGA一样通过千兆位以太网端口进行控制,板上ARM处理器允许自主操作并具有与本地/外部网络上的器件通信/控制的能力3。

图3 Pentek公司基于Xilinx RFSoC的COTS SDR

固件

上一代FPGA使用如VeriLog或超高速集成电路描述语言(VHDL)的文本化硬件描述语言(HDL)编程。Xilinx的Vivado已包含了最新的符合AXI4标准的IP模块。Xilinx的IP Integrator工具有代表HDL代码的虚拟图形化模块,可以通过拖放布线相互连接。图4显示了一个VHDL编码案例(见图4a)以及相应的拖放图形模块(见图4b)。这种更直观的编程方式使得FPGA新手也能将表示FIR滤波器和DDC之类硬件的逻辑模块连接在一起,以创建一个SDR。这种编程方法支持将厂商提供的硬件专用IP模块与Xilinx的IP模块快速集成,以创建一个可以工作的SDR。两种类型的IP模块可以组合在一起,以创建一个共用库。

图4 Xilinx的IP Integrator工具,显示了VHDL编码(a)和直观的“拖放”图形化模块(b)

软件

这些IP编程的进步,为COTS SDR厂商提供了创建一种单一BSP模块的机会,该模块与有某个场景中全部所需FPGA程序参数的一个IP模块一致。一个案例是一种“时钟控制BSP模块”,它直接对应于一个“时钟控制IP模块”。

5G应用

最新一代的SDR技术正在改变游戏规则,COTS SDR制造商可以用它为开发5G无线电产品的工程师提供多通道SDR收发器。

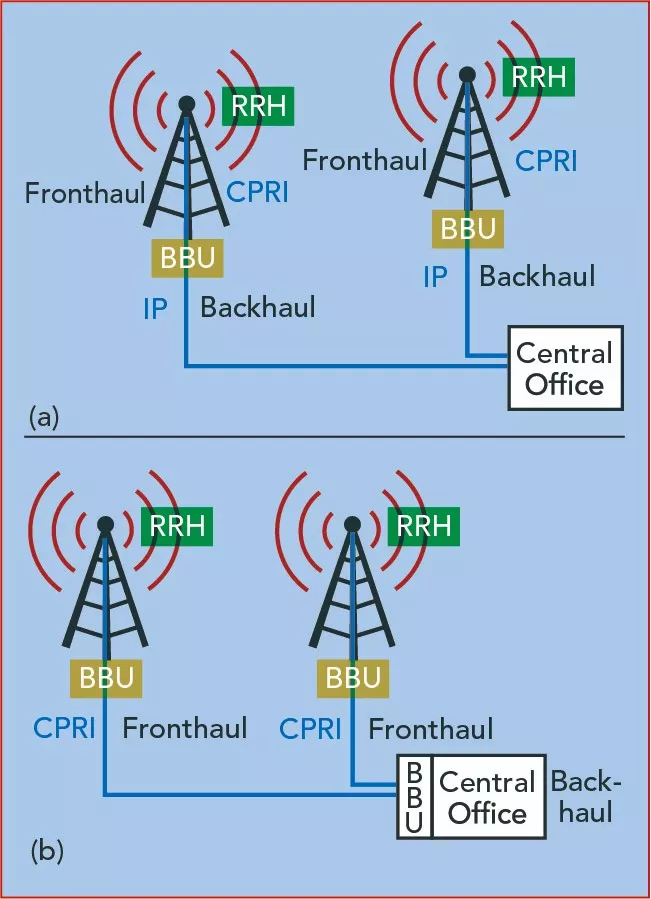

图5图示了分布式和集中式无线接入网络,即D-RAN和C-RAN,之间的区别。通过LTE,传统的D-RAN蜂窝站点正在被新的C-RAN取代,以提高数据传输效率、降低无线电成本。然而,由于RF路径损耗的增大,5G的毫米波大规模MIMO架构需要分离,以使远程无线电头端(RRH)更靠近终端用户。

图5 分布式(a)和集中式(b)的RAN

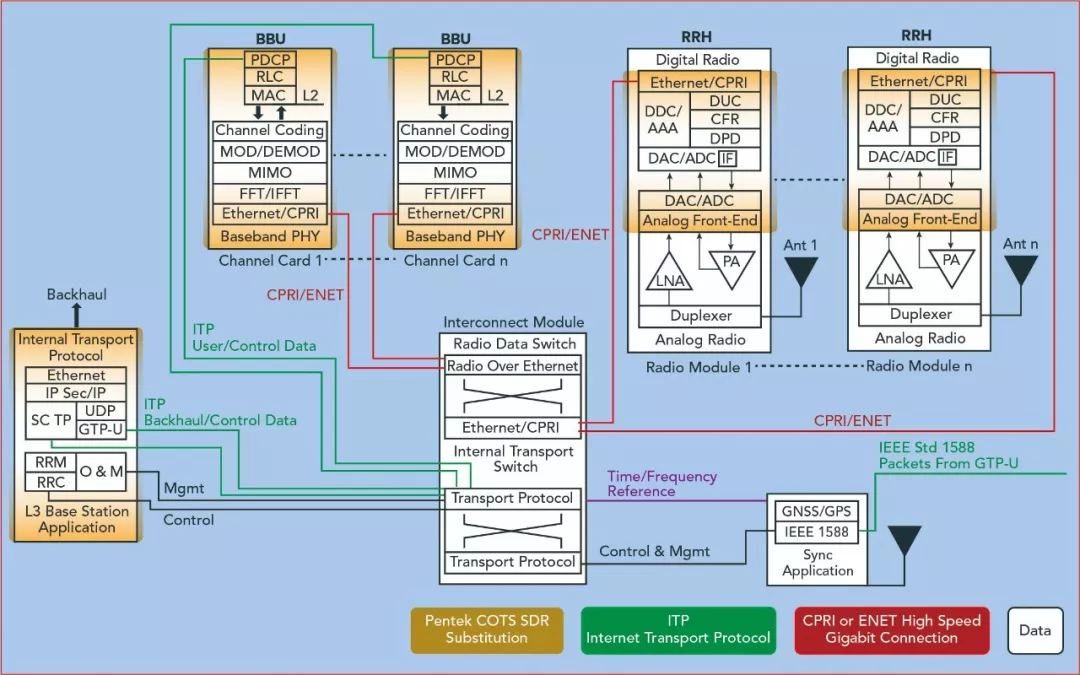

图6示出了由基带单元(BBU)、RRH、GPS时间/频率源和一个互连模块组成的一个C-RAN的功能框图。突出显示了几个模块,以提示COTS SDR的潜在应用。BBU位于一个中心局或“云中”的虚拟网络之中,可以访问用于回传的多条光纤数据线。RRH位于更靠近最终用户的外部位置。这个前传连接案例中的BBU和RRH,根据系统要求,可以使用一个普通的公共无线电接口(CPRI)、开放的基站架构倡议(OBSAI)或标准的以太网连接。新的前传概念,如可扩展的无线电接入网络(xRAN)和开放无线电接入网络(ORAN),未来将取代这些传统的接口。

图6 C-RAN的功能框图,显示了COTS SDR的用武之地

这些不同的传输模式选项与传统的蜂窝、Verizon 5G技术论坛(5GTF)或3GPP 5G新无线电(NR)规范相结合配置,形成了一个复杂的异构网络,需要一个灵活的开发平台4。

硬件

图7显示了采用一块COTS SDR板模拟C-RAN架构中的RRH的一个案例。含RRH的初始C-RAN的一部分示于图7a中,包含了图7b中的COTS SDR RRH。图7a中框选的区域可以用图7b所示的载波卡实现。定制的模块化载波卡,包含了接收和发射放大器、一个GPS接收机和一个光电收发模块。SoM内部包含了RFSoC以及用于电源管理、数据存储和模拟/数字I/O的全部连接。通过一个双工器将来自天线的输入RF信号连接到接收低噪声放大器,将其与功率放大器的高发送电平隔离,并将其连接到一个ADC通道。通过必要的IP,这个SoM和定制的载波组合件可以模拟初始RRH。

图7 RRH的功能框图(a),图示了可以用一个COTS SDR实现的功能(b)

固件

一旦进入了FPGA架构,数字采样将在DDC中进行1/10抽取、频率选择或调谐与滤波。DDC输出的采样,可以流向功率计模块进行测量,并在阈值检测器IP模块中进行分类。这些处理过的采样可以流向ARM处理器,以便在用于中继的数字上变频器(DUC)中进行上变频前的波峰因数降低和数字预失真运算。DUC与DDC相反,采用频率转换和插值替代1/10抽取。数字化的I/Q采样数据在数字无线电中打包,通过一个无线电数据交换机传输到BBU。由于信道和数据传输协议的多样化,必须了解信号的最大数据吞吐量并确保充足的网络容量。

软件

根据所需的控制等级,可以为新的IP和ARM处理器、或ARM处理器与FPGA创建BSP例程,编程实现自主运行。

结论

本文的目的是使传统无线电工程师熟悉COTS SDR供应商提供的最新硬件、固件、软件和设计工具,表明SDR可用作5G开发的平台。这些SDR平台提供了卓越的信号完整性、高测试重复性和模块化组件,可根据不断变化的5G设计要求进行调整。5G的演进将需要实验和优化的多轮开发迭代,采用COTS SDR系统作为起点将缩短产品上市时间。

编辑:hfy

-

瑞萨电子宣布与AMD携手 展示面向5G有源天线系统的完整RF和数字前端设计2023-02-21 1220

-

自制d-diot多用途物联网pcb2022-08-10 1514

-

一文详解5G网络模拟器的解决方案2020-10-21 1560

-

如何利用FPGA设计软件无线电平台?2019-08-02 2240

-

软件无线电设计解决方案2019-07-29 1774

-

基于软件无线电的3G和4G应用2019-07-26 1508

-

软件无线电助力3G通信发展2019-05-28 2334

-

软件无线电(SDR)平台带你从频谱共享到5G研发2018-10-23 5789

-

软件无线电、无线电的技术概述及应用2018-08-21 4372

-

多用途定位仪(程序)2017-06-16 1268

-

泰克推出用于搜索射频干扰的快速、多用途解决方案2012-09-27 1352

-

基于51单片机的低价型远程多用途无线遥控模块2012-08-08 2453

-

多用途台灯2009-04-21 1003

-

多用途讯响电路及制作2009-04-13 427

全部0条评论

快来发表一下你的评论吧 !