逻辑电平案例:从IO口结构分析电流倒灌的原因及解决措施

电子说

描述

在逻辑电平互连的过程中,经常会出现电流倒灌的现象。本篇从IO口的结构出发,分析电流倒灌的原因及解决措施。

1、IO口结构

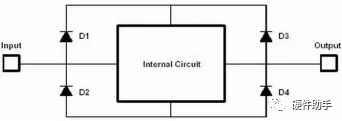

IO口根据接口类型的不同,分为高阻、三态、推挽、开漏等,但除了功能性区别外,几乎所有IO口都会存在如下结构所示的四个二极管。

D1在大多数CMOS集成电路中起着防静电功能,同时辅助起着输入端限幅作用。但是在ABT、LVT、LVC和AHC/AHCT类集成电路中无此二极管。

D2是半导体集成所产生的寄生二极管(存在于所有数字集成电路),其辅助功能为对线路反射的下冲信号进行限幅,提供一些放电保护功能。

D3用于保护CMOS电路在放电时的干扰。在大多数双极性器件中也存在此二极管,但为寄生二极管。在集电极开路和三态输出的双极性器件中无此二极管。

D4在所有集成电路中均存在此二极管。它是器件的集电极或漏极的二极管。在双极性器件中还附加了一个肖特基二极管对线路反射的下冲信号进行限幅。在CMOS电路中附加了二极管以增加防静电功能。

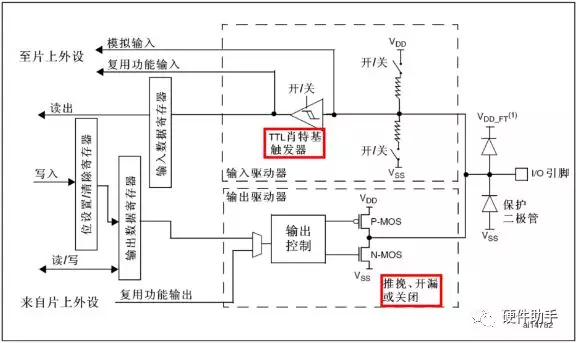

STM32的IO口结构

2、电流倒灌的原因及解决措施

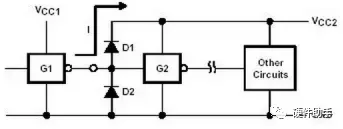

当使用CMOS型器件作为接口芯片时,如果Vcc2断电,Vcc1继续供给G1,G1的高电平输出电流将通过D1向Vcc2上的电容充电(该充电电流将使D1迅速过载并使其损坏。CMOS器件中D1只能承受20mA的电流)并在Vcc2上建立一电压,该电压使使用Vcc2供电的其它电路工作不正常,特别是可编程器件。

针对上述现象,解决措施如下:

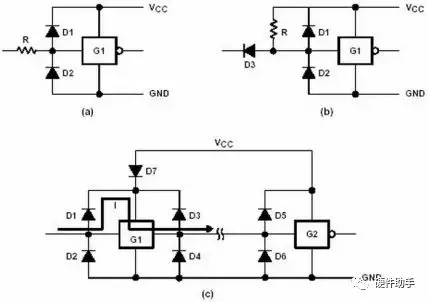

如图(a):在信号线上加一个几欧姆的限流电阻,可防止过流损坏二极管D1,但不能解决灌流在Vcc上建立电压;

如图(b):在信号线上加二极管D3及上拉电阻R,D3用于阻断灌流通路,R解决前级输出高电平时使G1的输入保持高电平。此方法既可解决灌流损坏二极管D1的问题,又可解决灌流在Vcc上建立电压。缺点是二极管D3的加入降低了G1的低电平噪声容限;

如图(c):在G1的电源上增加二极管D7。缺点是前级输出高电平时,G1通过D1获得电压并输出高电平给后级电路。同时降低了G1的供电电压,使其在正常使用时高电平输出电压降低。

最有效的解决方法是使用双极型的器件(如LS系列器件,ABT系列器件)作为接口(即采用没有D1二极管的器件),由于双极型器件没有保护二极管D1存在,故不存在灌流通路。需要注意的是这时接口的输入、输出信号线上不能加上拉电阻(双极型器件输入悬空当高电平对待)。

编辑:hfy

-

硬件设计必读:电流倒灌解决方案2024-12-12 4345

-

电流倒灌揭秘:IO口损坏与系统故障的真相2024-12-11 2251

-

嵌入式笔记 | 非常容易被忽略的电流倒灌2024-12-09 2692

-

单片机接口电路设计中的电流倒灌和电平转换问题2023-09-27 3057

-

9.1 单片机IO口的结构2022-01-13 1729

-

单片机检测IO口高电平、低电平、悬空三种状态。2021-12-23 5031

-

从数电的角度去分析几种IO口模式2021-12-07 981

-

电流倒灌产生的原因2021-11-11 3199

-

怎样去解决电流倒灌的问题2021-09-28 7258

-

互联逻辑电平之电流倒灌原因和解决措施2021-09-10 1297

-

逻辑电平互连出现电流倒灌的原因及解决措施2021-01-07 2199

-

51单片机IO口的使用方法2020-08-25 2417

-

51单片机IO口输入输出方式_IO口的四种使用方法2018-04-26 69937

-

51单片机、AVR单片机和PIC单片机的IO口操作2018-02-20 11580

全部0条评论

快来发表一下你的评论吧 !