PYNQ学习案例——Zynq中断应用及编程思路

电子说

描述

作者:Mculover666

在实际玩Zynq中断之前,先扯一扯中断这个神奇的东西~

实时性是一个嵌入式系统很重要的性能,实时性体现在一个系统对外部事件的响应能力和处理能力上,而CPU对一个事件的响应及处理主要依托于 —— 中断。

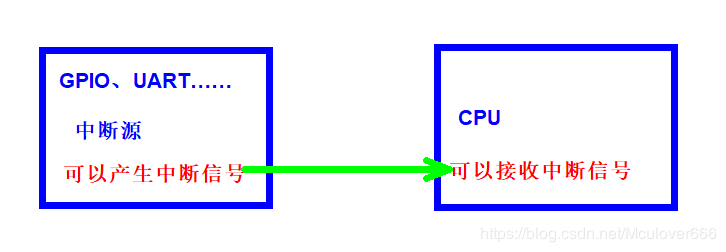

通俗的来说,中断的一个基本过程就是:当一个事件发生时(比如按键按下),产生一个可以发送到CPU的中断信号(上升沿或下降沿无所谓,是个信号就行),当CPU接收到这个中断信号后,对这个中断信号所表示的事件进行处理(跳转去执行中断服务程序,对按键按下这个事件进行处理)。

对这个基本过程抽象出来一个中断系统模型如图所示:

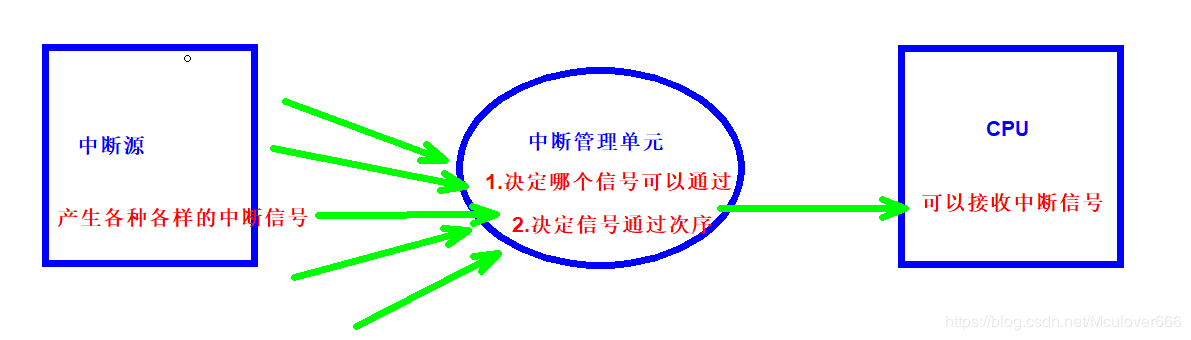

在上图中只是一个中断信号,那么当这个系统中存在很多中断信号时,群龙无首,整个系统就会乱套,CPU会像一只无头苍蝇一样到处去执行中断服务程序,结果可想而知,最后CPU肯定什么也干不了~

为了解决这个问题,需要派一个领导去管理这些各种各样的中断,这个管理者就是 —— 中断管理单元!所以,它只有一个功能 —— 管理这些中断信号!比如使能与失能 —— 让哪个中断信号通过或者让哪些信号不通过;“优先级” —— 谁先通过谁后通过,改进模型如下图:

这样一来,CPU永远只能接收到一个中断信号,所以CPU可以很舒服的去做他该做的事情了~

总结一下中断的编程思路:

配置外设可以产生中断信号

配置中断管理单元,使能信号通过,( 配置信号优先级 )

配置中断服务程序 ,确保CPU接收到中断信号可以及时处理

接下来依托这个抽象的中断模型玩一玩Zynq的中断,具体化这个模型~

1.实验目的

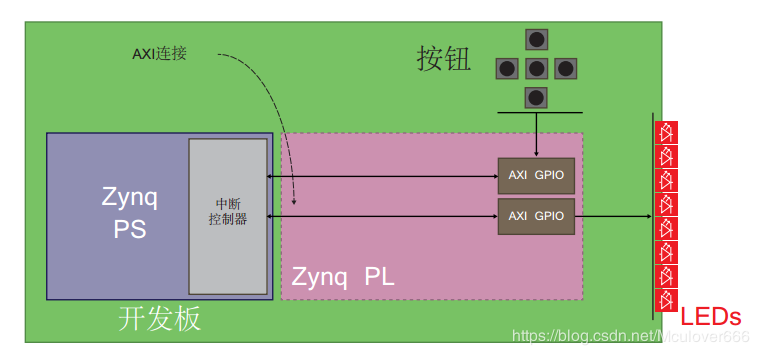

探索Zynq中PL->PS的中断,按下按键产生一个中断,这个中断被通用中断管理单元所处理,然后传递给Zynq PS,将变量值递增然后将值显示在led上。

2.实验步骤

2.1.新建基于Pynq-Z2的工程

2.2.创建硬件块设计

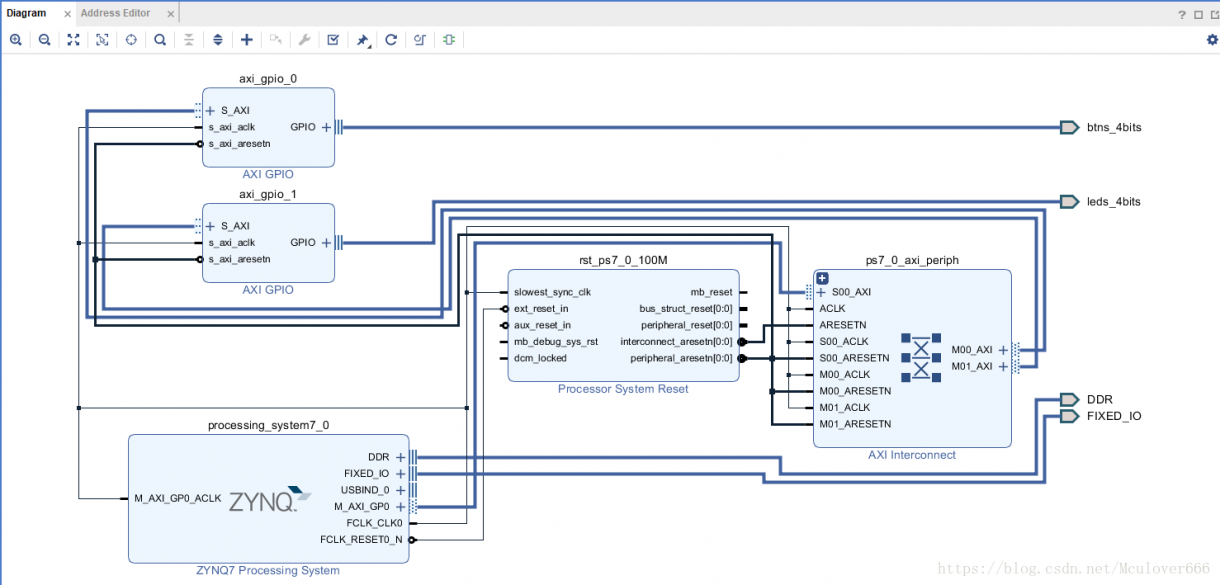

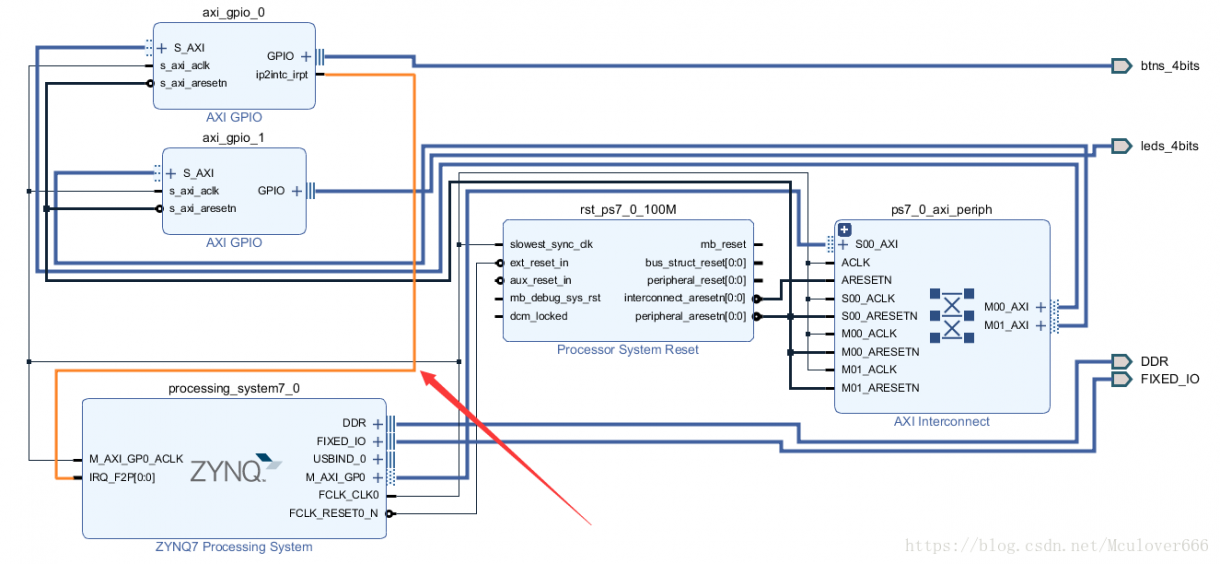

2.2.1.添加所用ip并自动连线

添加两个AXI_GPIOip核,一个连接板载4个按钮,一个连接板载4个led

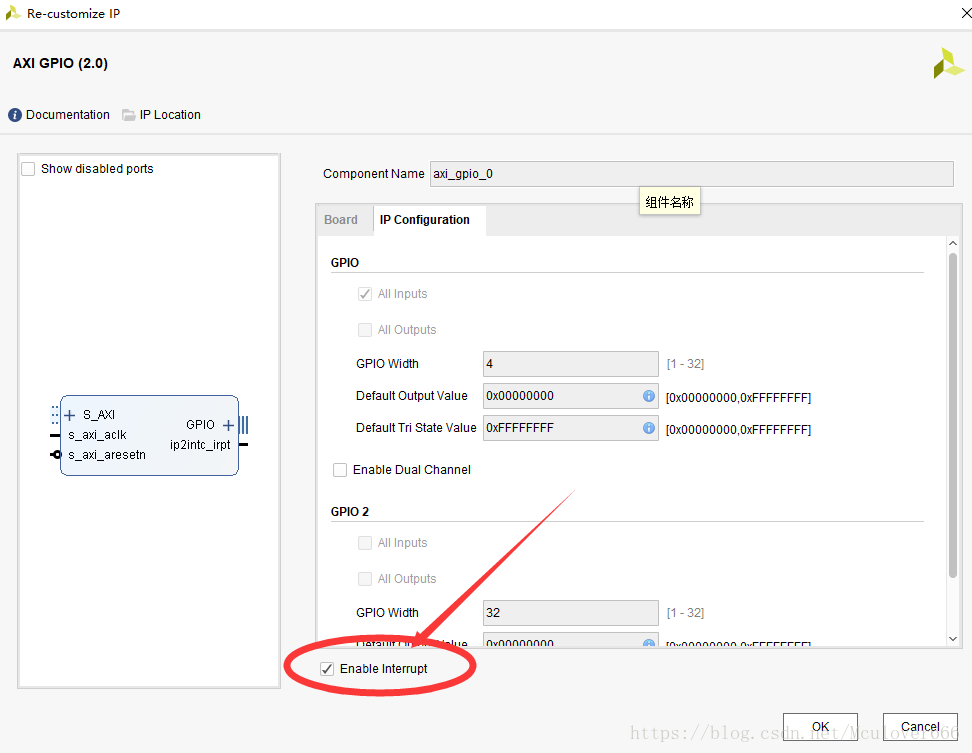

2.2.2.配置AXI_GPIO使能中断

这里因为4个按键是连接在axi_gpio_0上的,所以双击axi_gpio_0 ip核进行配置,如图,选择使能中断:

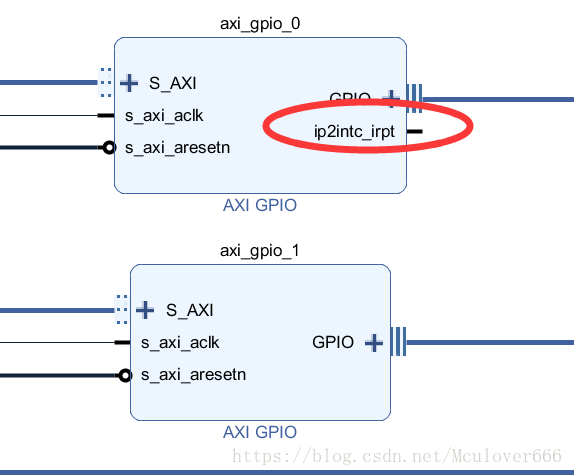

可以看到与未配置中断的axi_gpio_1有区别:

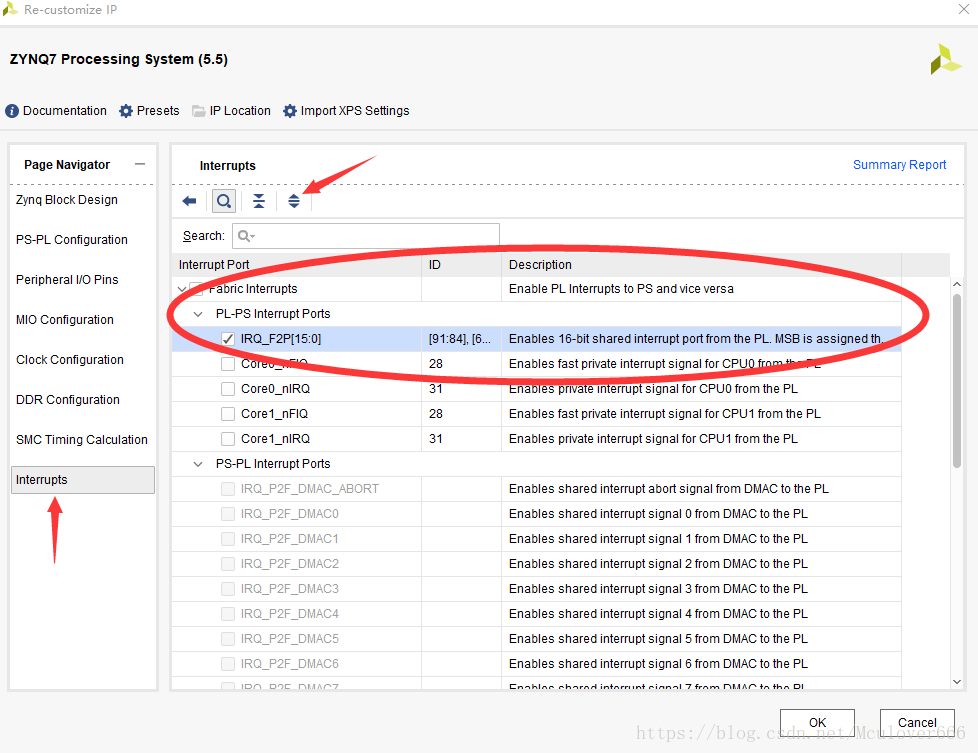

2.2.2.配置Zynq PS系统接收中断请求

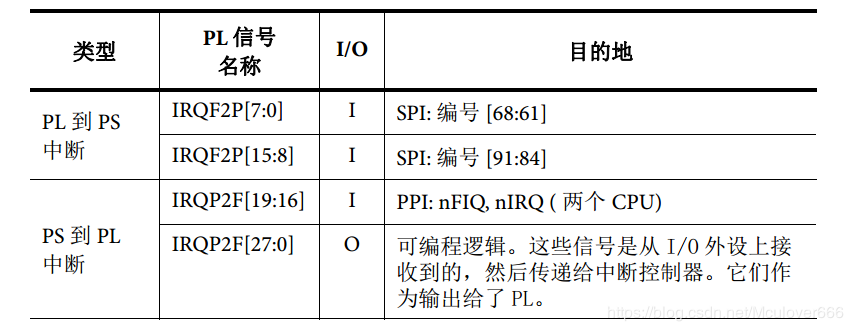

在配置之前需要对Zynq中的中断信号有个大致的了解,其中PS和PL之间的中断信号如表所示:

根据上图,双击zynq ip核进行配置,因为这里需要接收的按键中断是从PL端到PS端的,首先选中Fabric Interrupts中断组织,然后选中IRQ_F2P[15:0],使能16-bit的PL->PS共享中断端口,以便于来自PL端的中断可以连接到PS的中断控制器上:

2.2.3.连接AXI_GPIO的中断请求和PS的中断端口

手动进行连线:

2.3.验证设计,创建HDL文件,生成Bitstream,导出硬件设计文件

至此,中断信号的硬件数据通路构建完成,接下来是软件中配置中断管理单元和中断服务程序。

2.4.过渡到SDK上的软件设计

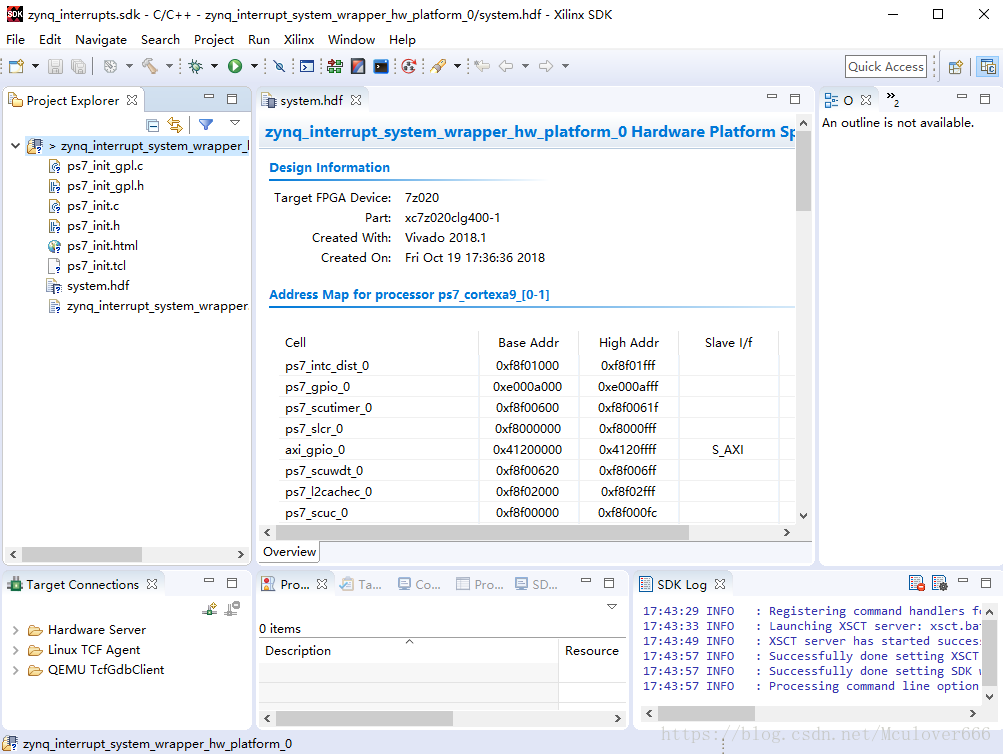

2.4.1.Launch SDK

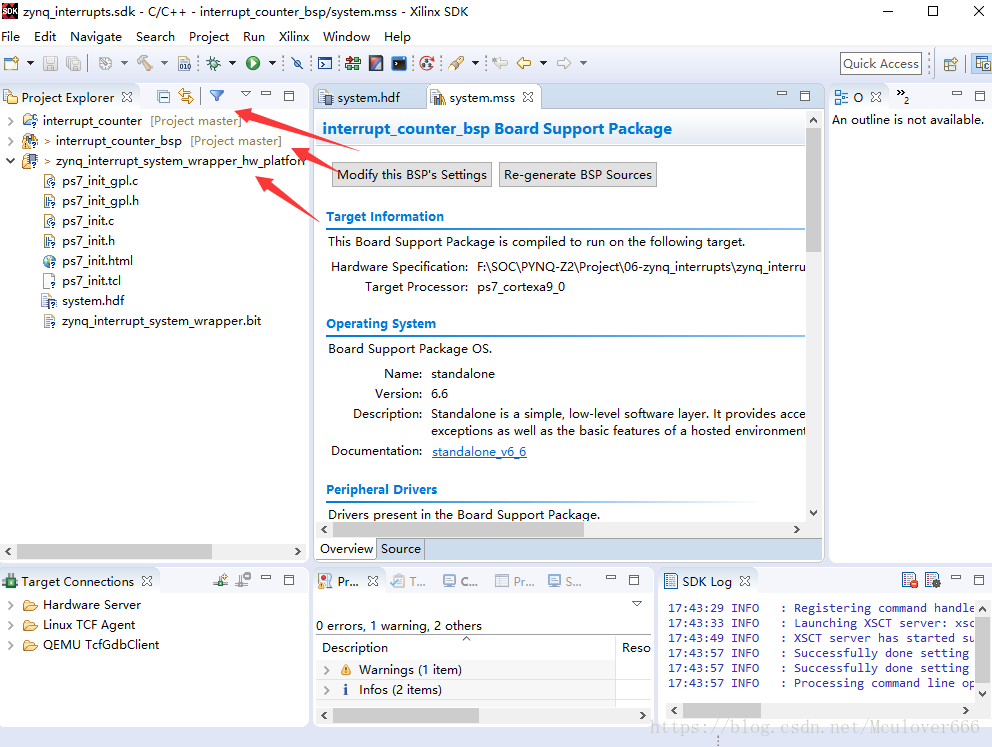

2.4.2.新建一个空的应用工程

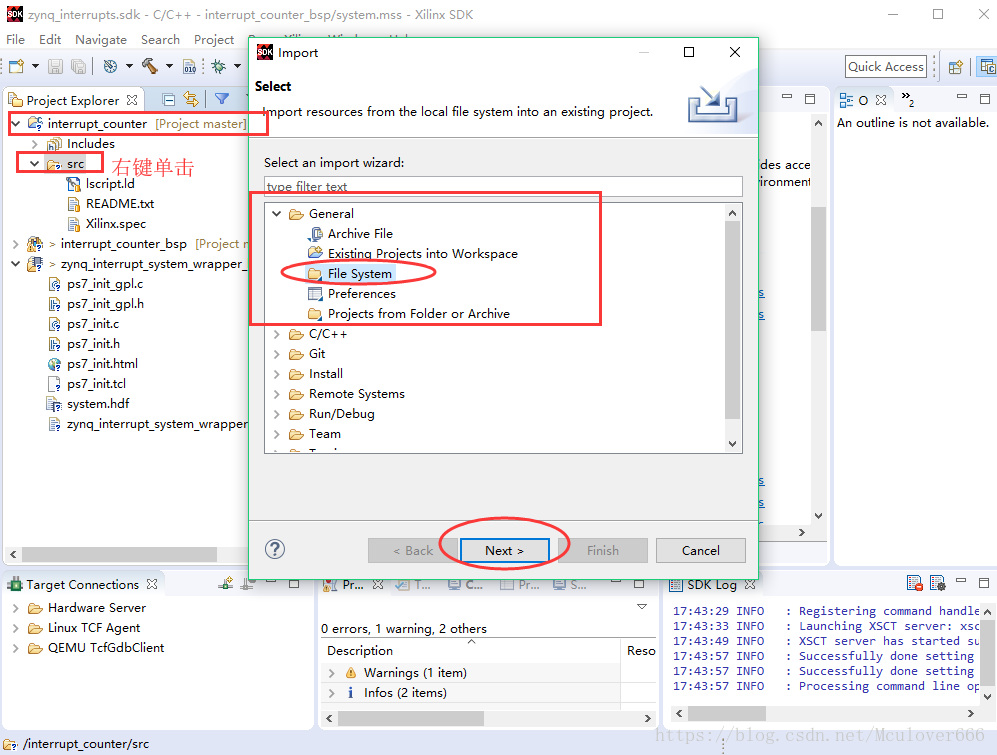

2.4.3.导入已有C文件

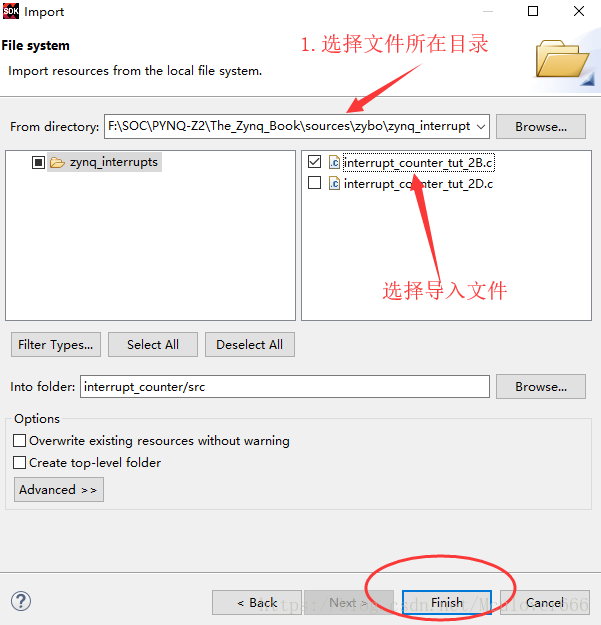

因为在实际项目中需要分工协作,所以这里选择导入随书附带的C文件:

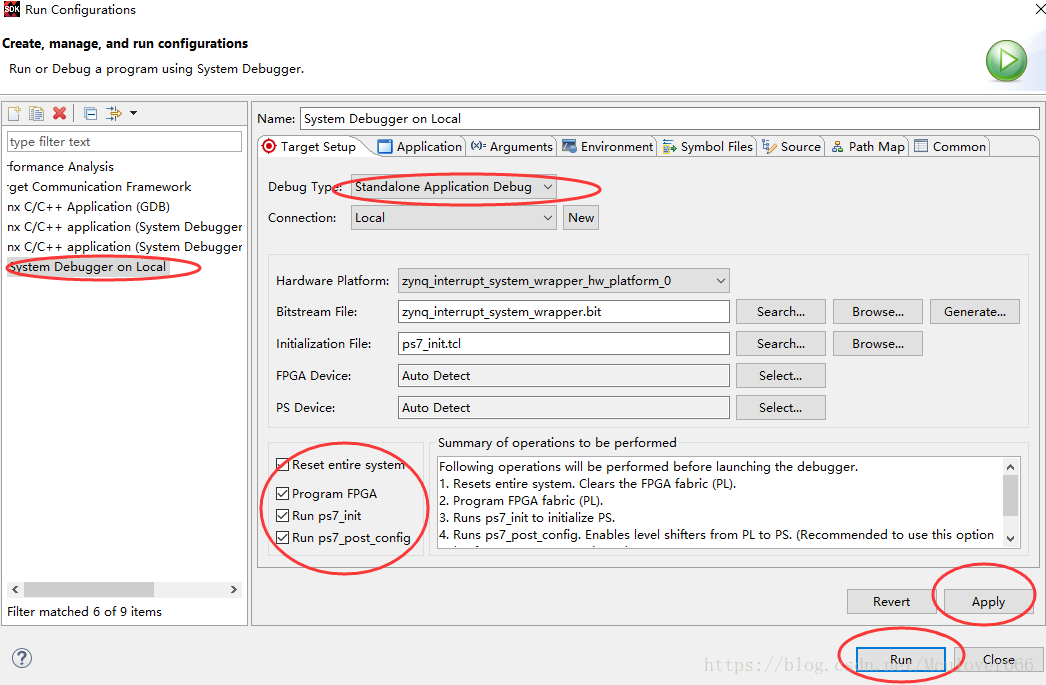

2.4.4.配置运行设置,板级验证

运行即可观察到现象。

2.添加定时器中断

2.1.实验目的

在已有一个按键中断的基础上,添加一个定时器中断,掌握添加多个中断到PS的方法。

2.2.实验步骤

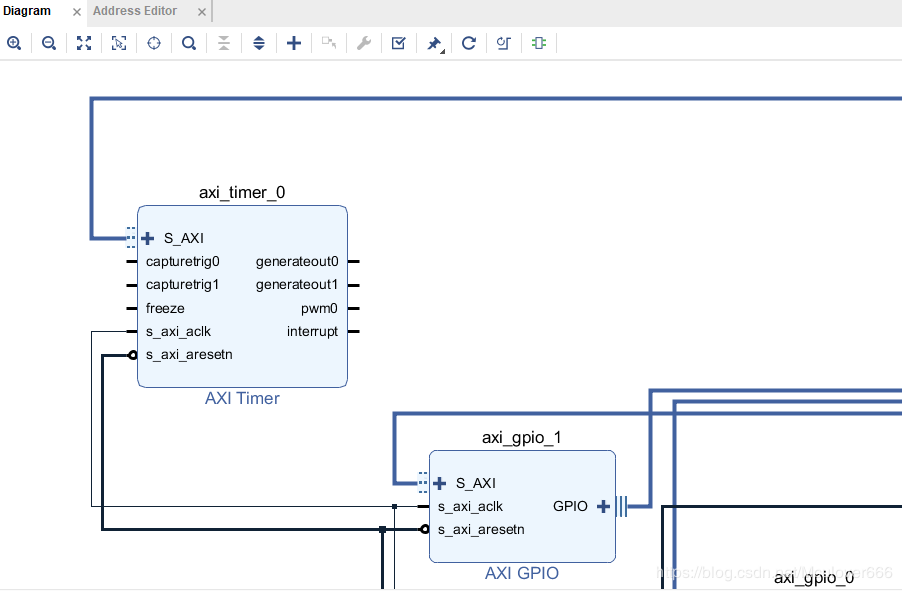

2.2.1.添加AXI Timer IP核并自动连线

添加时搜索"timer",选择AXI Timer添加,然后点击自动连线,结果如图:

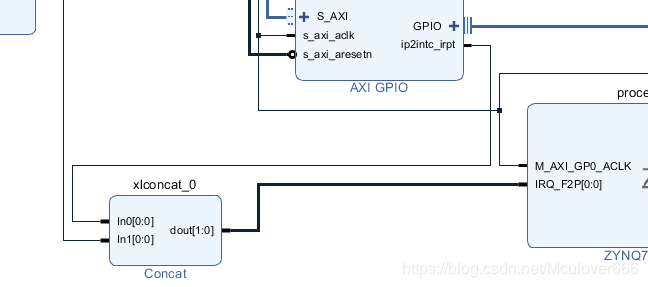

2.2.2.连接AXI Timer的中断到PS端

因为PS端的共享中断接口已经连接了一个AXI GPIO中断,所以如果要继续连接一个中断信号,要通过一个另外的ip核 —— Concat,在添加ip核时搜索添加,如图所示,将之前AXI GPIO 到ps的中断断开,然后将concat的dout信号连至PS端的IRQ_F2P[0:0],然后将AXI GPIO的中断信号连接至In0,将定时器的中断信号连接至In1,这样就完成了多个中断信号的共享。

生成Bitstream,导出硬件文件

编辑:hfy

-

基于PYNQ和机器学习探索MPSOC笔记2024-11-16 1457

-

如何为自己的ZYNQ板卡创建Pynq镜像2023-08-07 2795

-

使用Tensil和PYNQ在PYNQ Z1 FPGA板上运行机器学习2023-06-14 2082

-

什么是PYNQ?2021-02-24 4402

-

基于PYNQ-Z2开发板的PYNQ开源项目2021-01-02 8217

-

PYNQ案例(一):ZYNQ的PL与PS开发2020-12-25 10131

-

PYNQ项目——Pynq开发板启动实验2020-12-23 4887

-

通过Python 执行复杂的PYNQ 框架方案2020-12-22 5141

-

米尔PYNQ开发板来了2020-03-26 1334

-

digilent支持Python编程的Zynq开发板介绍2019-11-18 4673

-

【PYNQ-Z2试用体验】玩转PYNQ系列:一、板卡简介与资源整理2018-12-31 48198

-

【PYNQ-Z2申请】基于pynq的语音识别和新闻报道系统2018-12-19 4071

-

赛灵思PYNQ-Z2开发板免费试用2018-12-05 3729

-

PYNQ 基于Zynq架构添加了对python的支持2018-07-14 9391

全部0条评论

快来发表一下你的评论吧 !