VLSI电路中电迁移(EM)和IR下降分析

电子说

描述

互连是VLSI电路中的本地,中间和全局通信线路,其设计和物理状态对于实现IC可靠性至关重要。互连线通常由金属线制成,并且在传输电流时会暴露于电场中。电迁移(EM)和IR下降是两个不可避免的人员伤亡,这使得互连易于退化。

当经受高电流密度时,拥塞的互连在电子传播方向上传输金属离子。电迁移(EM)的过程会腐蚀并累积互连金属,分别形成孔和分支。互连的较低几何形状和EM的影响会增强电阻,从而引起IR下降问题。互连中的EM和IR下降是造成可靠性问题并缩短深亚微米VLSI电路寿命的原因。在接下来的部分中,让我们讨论互连及其设计解决方案中一些由EM驱动的问题。

EM存在时IR下降加剧

随着器件尺寸的减小,VLSI系统的速度和电流密度都有所提高。电源和时钟信号互连到EM 的脆弱性在高密度IC封装中更大。在EM的影响下,互连线在下游变窄,而上游的互连线和过孔则导致金属沉积。

这些由EM引起的通断会改变互连和过孔的电阻。通过电源互连的电流增加会导致IR下降,并影响设备性能。频繁的开关活动加剧了时钟互连中的IR下降,并降低了设备速度。如果您的IC设计包括具有不同宽度的多互连结构,则在减轻IR压降方面会稍有成功。改进的互连设计可以减少VLSI电路块之间的信号时间延迟,并很大程度地降低时钟偏斜。

EM的其他后效应及其设计解决方案

如果您得到混乱的正式文件,您会保持冷静吗?同样,信号传播中的任何串扰或错误都会使VLSI电路正常工作。EM效应始于电路逻辑中的间歇性毛刺,随后导致器件不稳定。EM的一些后遗症是:

互连延迟:互连电容和电阻的增加延长了信号传播中的RC时间延迟。互连延迟限制了IC速度及其性能特征。如果您不关心功耗,请尝试插入互连中继器以减少时间延迟。

通孔缺陷:随着金属在通孔中的衰减,会产生两种类型的缺陷:

电阻性开路(ROP)缺陷,类似于应连接的两个互连之间连接的缺陷电阻器。

卡塞开路(SOP)缺陷,这是应连接的两个互连之间的开路。

单切口通孔替代多切口通孔在ROP和SOP缺陷期间提供了备用路径。通孔的并行连接还有助于降低互连的有效电阻。

抗噪声能力差:表面不平整,杂散阻抗,阻抗不匹配以及相邻互连的邻近度是影响芯片信号完整性的一些触发因素。可以通过屏蔽互连来改善错误逻辑状态的发生,降低的噪声容限和降低的时钟速度。

寿命缩短:在深亚微米VLSI技术中,互连质量的下降在缩短EM寿命方面起着关键作用。在电磁效应的作用下,空洞的尺寸和形成致命空洞的时间降低了,因此互连死亡率很高。下列IC设计修改可以提高EM寿命。

扩大互连宽度:缩小尺寸和纳米级IC技术不切实际。

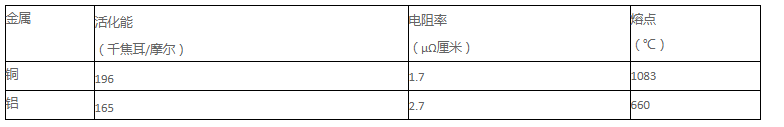

用铜(Cu)代替铝(Al)互连:Cu具有较低的电阻率,较高的电导率和较高的熔点。根据布莱克方程式,平均失效时间(MTTF)取决于激活能量,电流密度和温度。表1给出了Al和Cu在某些物理参数上的比较,并证明了Cu互连更好。

表1:在熔点估算的Cu和Al物理参数的比较

使用Al和Cu合金:通过使用Al-Cu合金互连,MTTF很高。它还可以在一定程度上防止互连结尖峰。

避免互连中的直角弯曲:因为实验证明弯曲弯曲可以实现较长的芯片寿命并承受EM应力。

层间电介质:金属互连线和低k 介电材料之间的粘附力减少了传播延迟,并降低了基板金属层中的内部电容和内部电容。

互连掺杂剂:将金,银和锰等金属作为掺杂剂引入互连金属中。它改善了EM特性,例如EM应力,电阻和附着力,并最终改善了VLSI电路的EM预期寿命。

设计互连的简便方法

在复杂的纳米级VLSI技术中,短期可靠性是无法接受的特征。主流芯片制造行业忽视了后端(BEOL)元素(尤其是互连)的过度设计和欠设计之间的平衡。这种诱杀陷阱向IC设计工程师提出了挑战,要求其在较小的占位面积内提供高性能和出色可靠性的新设计。在完成最坏情况的互连设计时,您需要进行几次设计迭代,要设计出面积,电流密度,温度,EM和IR压降限制等约束条件。如果有简单的出路,您喜欢走这条详尽的道路吗?

-

电源网格的电压下降和电迁移(EMI)效应分析2009-10-23 7392

-

如何正确模拟仿真中的VLSI电路?2021-06-17 2032

-

电子镇流器中功率因数校正电路的分析及应用 (IR2166/I2009-10-09 2454

-

电源网格的电压下降和电迁移效应分析2009-12-26 1552

-

VLSI_VLSI测试2012-05-30 11016

-

什么是电迁移 PCB中的IC电迁移分析2021-01-22 14779

-

PCB技术:电化迁移ECM失效分析2022-11-21 3069

-

oltus-XFi定制电源完整性解决方案加速EM-IR分析2023-04-20 2409

-

工艺可靠性电迁移EM测试2023-09-07 9915

-

几种优化EM的有效措施2023-11-30 3135

-

什么是EM电迁移?它带来的影响有哪些?2023-12-06 4893

-

Cu/low-k互连结构中的电迁移问题2025-03-13 2075

-

西门子mPower软件助力联华电子加速EM/IR分析2025-08-07 997

全部0条评论

快来发表一下你的评论吧 !