4bit的移位寄存器复位与不复位的实现

描述

实现一个4bit的移位寄存器如下,不带复位

module shift_reg(

input clk,

input rst,

input din,

output dout

);

reg [ 3:0] buff;

assign dout = buff[3];

always@(posedge clk) begin buff[3:0]

endmodule

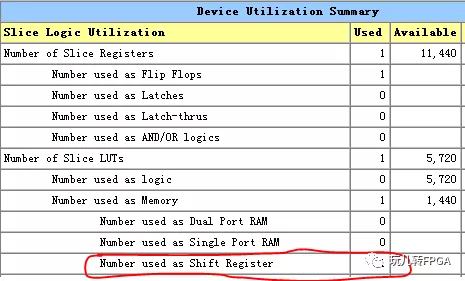

下图是ISE14.7实现后的结果如下图所示,编译器直接把他综合进了一个SRL16里面,也就是专用的移位寄存器模块,只需要一个LUT就可以实现16bit以内的移位

这是不带复位的资源,可以看到触发器只用了一个,LUT也只用了一个,并且是作为存储器用的,而且是作为存储器里面的移位寄存器使用。

下面是带有复位的移位寄存器代码

module shift_reg(

input clk,

input rst,

input din,

output dout

);

reg [ 3:0] buff;

assign dout = buff[3];

always@(posedge clk)

begin

if(rst==1) buff

end

endmodule

ISE14.7综合结果如下:

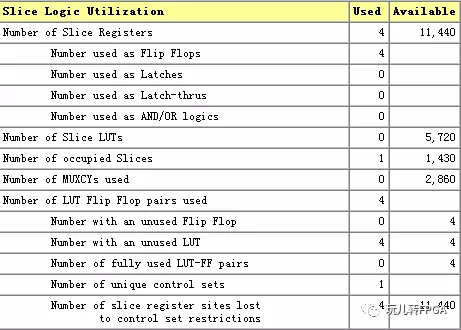

从上图可以看出,他是用了4个触发器级联构成,并且每个触发器的复位端都是接了rst端的。

下图是资源消耗,看的出来用了4个触发器和0个LUT:

综上:移位时间越长用没有复位的方式越节约资源。

那么,对于寄存器初始状态没有复位怎么设置他呢?

verilog2001的标准已经解决,ISE14.7和vivado也都支持

比如, reg [ 3:0] buff = 0;就是上电后寄存器buff为全0

而 reg [ 3:0] buff = 8'hff;就是上电后寄存器buff的值为全1

编辑:hfy

-

移位寄存器右移是怎么移位的2024-07-12 5197

-

移位寄存器的工作原理 移位寄存器左移和右移怎么算2024-01-18 14819

-

移位寄存器复位与不复位的区别在哪?2023-06-28 2550

-

移位寄存器的设计与实现2022-09-06 6526

-

移位寄存器的原理2019-07-15 77578

-

一文解析Matlab如何实现移位寄存器2018-04-26 18072

-

移位寄存器实验报告_移位寄存器原理2017-12-22 29601

-

寄存器与移位寄存器2016-05-20 1302

-

移位寄存器,移位寄存器是什么意思2010-03-08 18269

-

线性移位寄存器2010-01-12 2284

-

第二十六讲 寄存器和移位寄存器2009-03-30 10962

全部0条评论

快来发表一下你的评论吧 !