使用Vivado Simulator运行功能和时序仿真案例

描述

Vivado Simulator基本操作

Vivado Simulator是一款硬件描述语言事件驱动的仿真器,支持功能仿真和时序仿真,支持VHDL、Verilog、SystemVerilog和混合语言仿真。点击运行仿真后,工具栏中显示了控制仿真过程的常用功能按钮:

这些控制功能依次是:

- Restart:从0时刻开始重新运行仿真;

- Run All:运行仿真一直到处理完所有event或遇到指令指示停止仿真 ;

- Run For:按照设定的时间运行仿真,每点击一次都运行指定时长;

- Step:运行仿真直到下一个HDL状态;

- Break:暂停仿真运行;

- Relaunch Simulation:重新编译仿真源文件且restart仿真,当修改了源代码并且保存了文件后,只需要Relaunch即可,而不必关闭仿真再重新打开运行。

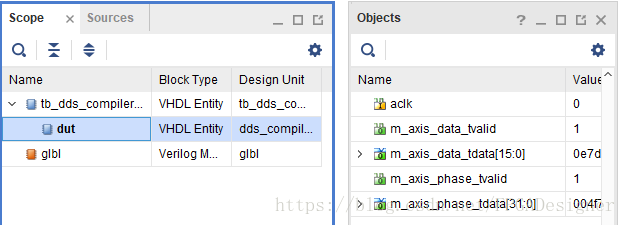

Scope窗口

Vivado Simulator中将HDL设计中的一个层次划分称作一个scope,比如实例化一个设计单元便创建了一个scope。在Scope窗口中可以看到设计结构,选中一个scope后,该scope中所有的HDL对象都会显示在Object窗口中。可以选择将Object窗口中的对象添加到波形窗口中,这样便可以观察到设计中的内部信号。

Scope窗口中可以在Settings中设置显示哪种类型的scope,但注意当某一scope被关闭显示后,其内部的所有对象(不论什么类型)都会被隐藏。对某一scope右键,弹出菜单如下:

- Add to Wave Window:将所有状态为可见的HDL对象添加到波形窗口,值从添加到仿真波形的时刻开始显示,想要显示插入之前的值,必须restart(注意不是relaunch,否则会耗费更多的时间);

- Go to Source Code:打开定义选中scope的源代码;

- Go to Instantiation Source Code:打开实例化选中实例的源代码(对于Verilog而言是module,对于VHDL而言是entity)

- Log to Wave Database:可以选中记录当前scope的对象,或者记录当前scope的对象与所有下级的scope。相关数据会存储在project_name.sim/sim_1/behav目录下的wdb文件中。

Objects窗口

该窗口中显示了当前选中的scope所包含的HDL对象,不同类型或端口的对象显示为不同的图标,在Settings中可以设置显示的类型:

Object的右键菜单中有一些新的设置功能:

- Show in Wave Window:在波形窗口中高亮选定的对象;

- Radix:设置Objects窗口中选定对象的值的显示数字格式,包括默认、2进制(Binary)、16进制(Hexadecimal)、8进制(Octal)、ASCII码、无符号10进制(Unsigned Decimal)、带符号10进制(Signed Decimal)和符号量值(Signed Magnitude)。注意此处设置不会影响到波形窗口中的显示方式;

- Defult Radix:设置Radix中Default所表示的值;

- Show as Enumeration:显示SystemVerilog枚举信号的值,不选中时,枚举对象的值按radix的设置方式显示;

- Force Constant:将选中对象的值强行定义为一个常量;

- Force Clock:将选中对象强行设定为一个来回振荡的值(像时钟一样);

- Remove Force:移除选定对象的所有Force设置。

Wave窗口

当运行仿真后,会自动打开一个波形窗口,默认显示仿真顶层模块中的HDL对象的波形配置。如果关闭了波形窗口,可以点击Window->Waveform重新打开。

窗口中的HDL对象和分组情况称作一个波形配置,可以将当前配置保存为wcfg文件,下次运行仿真时就不需要重新添加仿真对象或分组。窗口中还有游标、记号、时间尺等功能帮助设计者测量时间。右键菜单中有一些新的设置功能:

- Show in Wave Window:在Object窗口中高亮选定的对象;

- Find/Find Value:前者是搜寻某一对象,后者是搜索对象中的某一值;

- Ungroup:拆分group或虚拟总线(virtual bus);

- Rename/Name:前者设置用户自定义的对象显示名称,后者选中名称的显示方式:long(显示所处层次结构)、short(仅显示信号名称)、custom(Rename设置的名称);

- Waveform Style:设置波形显示为数字方式或模拟方式;

- Signal Color:设置波形的显示颜色;

- Divider Color:设置隔离带的颜色;

- Reverse Bit Order:将选定对象的数值bit显示顺序反转;

- New Virtual Bus:将选定对象的bit组合为一个新的逻辑向量;

- New Group:将选定对象添加到一个group中,可以像文件夹一样排列;

- New Divider:在波形窗口中添加一个隔离带,将信号分开,便于观察。

Vivado Simulator会将配置(用户接口控制和Tcl命令)保存到仿真运行目录的xsimSettings.ini文件中,下此打开仿真时就会自动恢复相关设置。使用此功能时在Simulation Settings中关闭clean up simulation files,以防止重新运行仿真时配置文件被删除。如果想要恢复默认设置,则开启clean up simulation files,或直接删除xsimSettings.ini文件即可。

本文只对Wave窗口做了简单介绍,本系列第20篇对其中的具体术语和功能使用做了详细描述。

运行功能和时序仿真

工程创建好后,便可运行行为级仿真(behavioral simulation),在成功地综合和实现之后,可以运行功能仿真(functional simulation)和时序仿真(timing simulation)。在Flow Navigator中点击Run Simulation,弹出菜单中选择需要运行的仿真:

- 综合后功能仿真:综合后,通用的逻辑转换为器件相关的原语,综合后功能仿真可以确保综合优化不会影响到设计的功能性。运行时,会生成一个功能网表,并使用UNISIM库。

- 实现后功能仿真:实现后,设计已经在硬件中完成布局和布线工作,实现后功能仿真可以确保物理优化不会影响到设计的功能性。运行时,会生成一个功能网表,并使用UNISIM库。

- 综合后时序仿真:该仿真使用器件模型中估算的时间延迟,并且不包括内部连线延迟。通用的逻辑转换为器件相关的原语后,可以使用估算的布线和组件间延迟。使用此仿真可以在实现之前查看潜在的时序严苛路径。

- 实现后时序仿真:该仿真使用真实的时间延迟。使用该仿真来检查设计功能是否能工作在设定的速度上,可以检测出设计中未约束的路径、异步路径时序错误(比如异步复位)。

添加仿真启动脚本文件

设计者可以创建一个批处理文件,添加到工程中,其中的命令将在仿真开始后运行,常用的流程步骤如下所示:

1. 创建一个包含仿真命令的Tcl脚本,比如如果想仿真运行到5μs,添加“run 5us”命令;如果想监测设计内部信号,将其添加到波形窗口中,添加“add_wave/top/I1/signalName”命令;

2. 将脚本文件命名为post.tcl并保存;

3. 将post.tcl文件以仿真源文件的形式添加到工程中,会显示在Sources窗口的Simulation文件夹下;

4. 在仿真工具栏中点击“Relaunch”重新编译运行仿真,Vivado会自动读取并执行文件中的命令。

编辑:hfy

-

vcs和vivado联合仿真2025-10-24 394

-

将vivado的仿真器改成modelsim,仿真时modelsim的transcript没法打印出e203实时运行的信息怎么解决?2023-08-11 641

-

modelsim仿真详细过程(功能仿真与时序仿真)2017-12-19 76706

-

介绍一下xilinx的开发软件vivado的仿真模式2018-05-29 9252

-

如何在在Vivado中使用Cadence IES模拟进行仿真2018-11-23 7625

-

FPGA开发Vivado的仿真设计案例分析2020-12-31 6538

-

VIVADO时序约束及STA基础2022-03-11 11443

-

如何在批模式下运行 Vivado 仿真器?2022-08-01 1508

-

SpinalHDL运行VCS+Vivado相关仿真2022-08-10 3910

-

仿真-ROHM Solution Simulator仿真电路的启动2023-02-14 1771

-

如何读懂Vivado时序报告2023-06-23 3276

-

如何在Vivado中添加时序约束呢?2023-06-26 6512

-

时序仿真与功能仿真的区别在于2023-09-08 7393

-

时序仿真与功能仿真的区别有哪些?2023-09-17 8685

-

Vivado时序问题分析2024-01-05 4364

全部0条评论

快来发表一下你的评论吧 !