以太网口信号质量测试分析 DAC驱动偏置机理的探讨

描述

一 前言

对于系统设计人员来说,模数混合电路中最困难的地方在于模拟部分的设计,其中最具代表性的就是我们经常要面对的物理层收发器(PHY)及其收发回路和匹配网络的设计。即使对于应用比较成熟的以太网物理层设计而言,DAC驱动电流的基准偏置,差分信号线对的走线,乃至于匹配电阻的位置,都有可能影响到其物理层的信号质量并通过接口技术指标测试暴露出来。

二 以太网口信号质量测试分析

1 100Base-TX接口测试环境及其设置

100Base-TX接口测试原理

100Base-TX接口的测试采用业内比较通用的诱导发包的方法来引导DUT发出扰码后的IDLE进行测试,更多细节请参考美国力科公司《Ethernet solution-QualiPHY》专项技术文档,

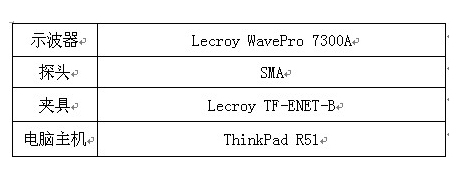

测试设备:

测试拓扑如图1:

图1 Ethernet接口指标测试连接框图

2 测试中出现的问题

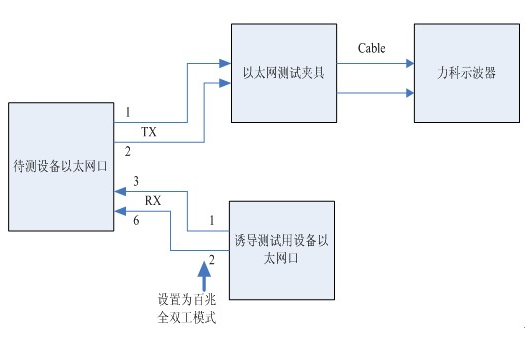

本次测试将主要验证产品上4个以太网100Base-TX接口的技术指标。对于其中比较直观的100Base-TX物理层的眼图模板,《ANSI+X3_263-1995》标准中有着明确的眼图模板定义见图2。

图2 100Base-TX 眼图模板

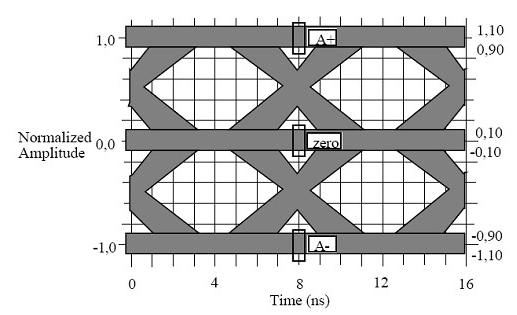

关于100Base-TX接口技术指标的测试方法,《IEEE Std 802.3-2000》标准中也有详细的说明, 工程师按照诱导发包的测试方法进行了网口眼图的测试,测试过程中发现测试网口出现了信号波形碰触模板的问题,波形见图3:

图3 以太网口测试眼图_FAIL

3 问题分析解决

从眼图初步分析来看,发送信号的幅度应该是满足要求的。但是可以明显的发现信号边沿还是比较缓,而且从单个波形来看边沿有不单调的问题。方案的原厂是一家通讯业内专注于IP宽带解决方案的国际型大公司,其以太网模块部分应该经过详细验证过。最大的可能是二次开发过程中板级系统设计时的一些关键技术参数的配合问题。工程师在进行了信号幅度以及上升下降时间等细节指标的测试之后证明了之前的判断,信号的幅度是满足要求的,但信号的上升下降时间与其他的方案相比确实大了(此方案的信号上升下降时间在4.3nS~4.6nS区间,虽然满足标准中要求的3~5nS。但根据系统容差设计原则,芯片设计人员通常会将Slew Rate调整在4nS左右,确保上下区间调整地最大容限。)。如何改进需要信号的发送接收回路进行一个系统的分析了。通过对网口技术指标的量测分析,目前最主要的问题在于信号的边沿比较缓,并且存在不单调的问题,最可能的原因是传输回路容性负载过大以及驱动不足。可以从这两个方面入手解决。

1)信号差分线对及阻抗匹配,网口的差分走线的阻抗控制和耦合处理我司在Layout这一块的应该已经很成熟了,而且此款方案采用芯片内部匹配网络,没有外部匹配元件。所以暂不进行这一块的分析。

2)传输变压器,工程师将一款测试通过的产品的Transformer与当前单板的Transformer进行互换后测试结果一致,眼图测试依然不通过。(请注意这里并没有对变压器进行变比以及差损,回损等技术指标的测试)

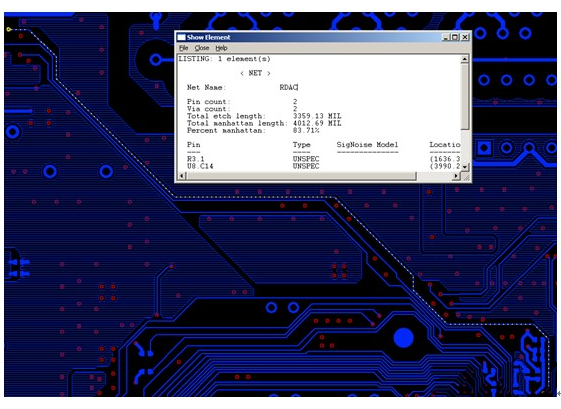

3)收发器驱动偏置电阻,也就是我们经常会看到的RDAC,也有叫RSET或其他的。这是原厂为开发人员提供的设定收发器驱动电流大小的硬配置节点,可以根据实际的单板设计和元件参数进行调整以实现对于标准的拟合。这是对信号波形影响最大的部分,在不对设计进行大的变动的情况下,通过调整驱动电流的大小可以用最小的变动来实现我们对于信号波形的调整。在查看产品PCB的同时我们还发现了另一个问题,RDAC电阻并没有放置在输入PIN附近,而是放到了远端的USB部分,之间的走线长达4000MIL。从事过PHY设计的工程师都知道,对于驱动偏置电阻的处理,应该最大限度的接近输入PIN,并保证地的干净,原厂的Layout Guide 也会进行重点说明。这也许不是造成输出信号边沿过缓的直接原因,但肯定会影响到信号波形的稳定性和单调性。是需要慎重处理的。

图4 RDAC走线连接图

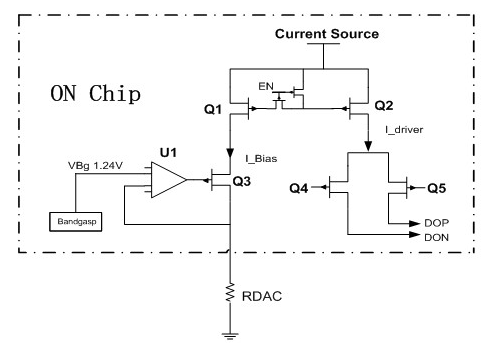

收发器驱动偏置机理分析:

系统设计人员都知道,以太网收发器的输出采用的是差分电流驱动,从收发器驱动偏置原理框图,见图5,可以进一步展开分析,收发器驱动电流可以通过带隙电压源与外部设定基准的比较来设定。收发器驱动电流(I_driver) 是从内部带隙和外部基准镜像过来。U1/Q3/RDAC/Bandgap组成了一个简单的比较控制环路实现基准单位电流的设定,例如带隙基准电压设定为Vbg=1.24V,RDAC取值为1.24K。这时通过比较器U1以及MOS管Q3反馈环路是确保稳定1mA(I_bias)的基准电流。而Q1/Q2/Current _Source组成了比例镜像电流源。可以通过设计保证I_driver=N*I_bias,N是设定的比例镜像因子。我们假定为20,通过公式可以计算I_driver=20*I_bias=20mA,这就是我们差分驱动的输出电流了。介绍到这里,大家都应该清楚了,我们可以通过调整RDAC的电阻大小实现基准单位电流的设定,进而达到调整差分驱动电流的目的。例如我们将RDAC调整为1K,则基准单位电流则变为I_Bias=1.24mA,同步的I_driver变为20*1.24mA=24.8mA,输出信号电平的幅度也会增大。实际的调测结果也是这样,可以解决信号边沿碰触模板的问题。

图5 收发器驱动偏置原理框图

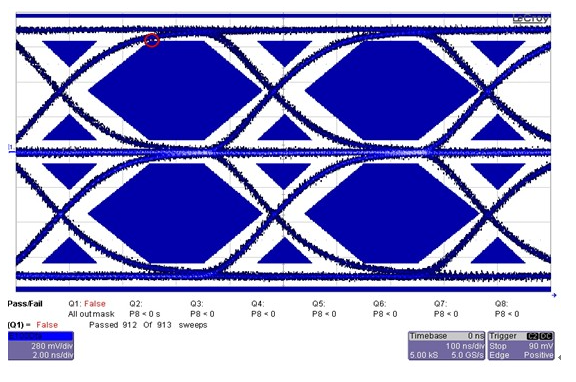

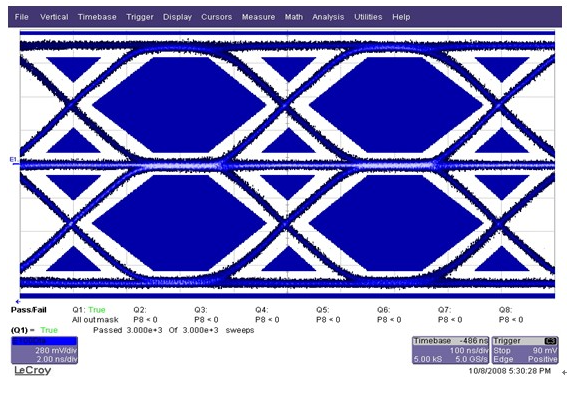

经过研发与测试工程师的讨论,在目前不改动系统设计的前提下,采用微调RDAC电阻的方法来增大信号输出电平幅度以解决信号眼图的问题。经过调整后,眼图测试通过,波形见图6。

图6 以太网口测试眼图_PASS

三 测试总结

(1) 作为系统设计人员,对子系统功能的了解以及信号回路模型的理解是我们进行系统定性分析的根本,而对于内部电路的深入研究是我们进行系统指标设计量化的基础。这对于我们的工程师提出了更高更深入的要求。

(2) 对于PHY收发器的设计,其驱动偏置电阻应尽量靠近设定管脚摆放,避免出现基准不稳定和误差的出现

以太网电路设计对于我们来说是比较常规和熟悉的设计,但我们真的理解和掌握了其内部原理以及架构吗。想要更深入,将会遇到更多的挑战,希望本文可以给到我们的系统设计人员一些启发。

[参考文献]

1:以太网收发器工作原理及其信号质量测试,ShenZhen GongJin Electronic Co.

2:Ethernet solution-QualiPHY ,LeCroy Corporation

编辑:hfy

-

车载以太网测试系统测试实例介绍#车载以太网北汇信息POLELINK 2023-09-12

-

以太网测试目前的趋势2014-01-08 0

-

探讨工业以太网技术~(二)2014-12-15 0

-

以太网的接口信号在PCB走线的时候差分可以不等长么?2023-04-07 0

-

以太网自愈环测试方法2016-12-29 678

-

以太网测试专题2017-01-21 689

-

以太网测试仪使用方法2017-12-27 11625

-

信而泰汽车以太网测试方案助力国内汽车以太网建设2020-06-11 3377

-

三种速率以太网标准的物理层编码规则及以太网一致性测试方案2021-06-24 11810

-

电信级以太网的应用场景和测试方案2021-06-26 3583

-

以太网和工业以太网有什么区别2023-01-03 1803

-

手把手教会千兆以太网一致性分析测试2023-02-24 2341

-

以太网眼图测试及整改案例分析2023-11-02 3851

-

以太网滤波器平衡测试2023-12-14 402

-

用示波器分析以太网传输机制2024-04-12 705

全部0条评论

快来发表一下你的评论吧 !