降低空载损耗提高开关电源效率DOE VI方案解析

描述

六级能效对于一些产商既充满机遇也充满挑战。而对于电源工程师而言,不增加成本就能提高效率无疑是最为理想的。本文中提出了能够提高开关电源效率还能节约成本来满足DOE VI的方案。

六级能效(DOE VI)解读

要按规则办事,首先就要了解规则,我们需要对标准有足够的认识。DOE,全称Department Of Energy,是美国能源部颁布的节能标准,主要对象为适配器、充电器等外置式电源。我们可以到其官网来了解其规则和下载最新的能效要求文件。

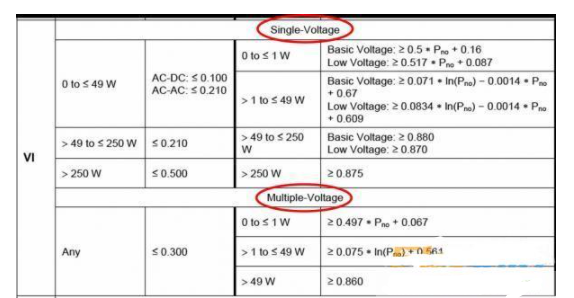

图1:能效要求

单路和多路输出的要求不同,从计算公式可以看出,多路输出的要求相对低些,没有要求那么细。对于单路输出的,对不同功率等级,要求更加细化了。空载功耗最严的是要求小功率的小于100mW。对小于0.21W、0.5W的要求,功率较大,实现也较容易。本文重点放在1W~49W这个区间,因为这个区间最有代表性。

图2:DOE新旧版的平均效率要求曲线图:(针对单路输出Vo》=6V的情况,系列1为新版VI要求,系列2为旧版要求

从曲线图可以看出,随着功率的增大,新旧版的差异越来小,相差在1%,要满足新版要求比较简单。但随着输出功率的减小,效率差值越来越大。而小功率一般对成本很敏感,不允许增加太多,这样要满足六级能效就变得比较棘手。

图3:六级能效计算公式

正确测试效率和空载功耗的方法。要注意以下三点:

1)测空载功耗的时候,电源的输出端不要接负载(电子负载会带来额外的损耗);

2)测平均效率的时候,功率分析仪的量程要注意调节,要设置在最接近实测值的那个量程;

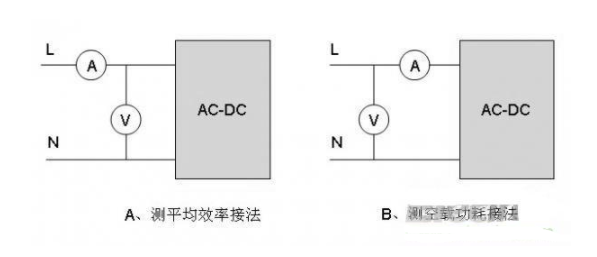

3)测试效率和空载功耗时的电压表和电流表接法是不一样的,见下图。

图4:测试效率和空载功耗时的电压表和电流表接法

以上接法可以满足大部分情况,但也不绝对。对于一些小功率的电源,如几W至十几W的,输入电流很小,电压表的分流作用始终占很大的比例,这样情况下即使测效率也要采用图B的接法,这一点容易被忽略。针对AC-DC的测试,用万用表是不行的,因为存在PF的问题,需要用到功率分析仪。如果是DC-DC的话,用万用表没有问题。

提升平均效率的方法与降低空载损耗的几个常用方法

提升平均效率的方法:先看看效率曲线,合理的设计应该是个开口向下的抛物线。

图5:效率曲线

平均效率是测试25%、50%、75%、100%这4个点的效率,求和后取平均。根据效率曲线,如果你设计的电源效率全都分布在A点的左边或者右边,那么平均效率一般都不是最高。比较优的是分布在A点两边,当50%或者75%的时候达到最高点A。由于控制策略以及特殊的设计,效率曲线可以有两个顶点。

第一个方法:优化变压器,尽量提高变压器的感量。这个一般不会增加成本,对平均效率的贡献大约有0.3%~0.6%,具体能多少基于原来的设计。但要注意低压满载以及跑峰值功率的时候变压器不要有饱和问题。但很多人都是碰到提升感量后存在变压器饱和问题就下结论增加感量行不通。变压器饱和问题不是一定要通过降感量来解决的,可以采用提升频率的方式来避免饱和。高压的时候跑低频,低压的时候升频,这样即使感量较大,在低压也可以抑制饱和。这样也可能会造成低压升频的方式需要依赖于IC,可选的不多不够灵活。那么有没有办法不依赖IC,从变压器下手呢?有没有一种方法使变压器的感量在满载的时候低,在轻载的时候高呢?轻载不用担心饱和问题,这对提升轻载效率非常有益。其实就是非线性电感了,如何去实现非线性呢?这就看各家的功力了。对于大部分来说,估计只能做到仅仅提升感量,升频和非线性电感无法导入。

第二个方法:还是变压器,用大一号的磁芯。比如空间允许,能用RM7的就不要用RM6。

用大一号的磁芯对平均效率的贡献约1%~2%,这个提升作用是非常大的。而大一号的磁芯对成本的影响很小或者还有可能下降(这个跟每家的用量和制程能力有关)。即使用大一号的磁芯会导致成本上升,那也可以通过用便宜的MOS和二极管来平衡回来。这样下来可以保持总成本不变,而换来零点几pa的提升。做过小功率的都清楚,即使用很好的MOS和二极管,对平均效率的提升作用也有限,能有个0.5%左右就很不错了,但成本需要增加较多。

第三个方法:控制IC的选择,选择轻载降频的IC。这个对轻载的效率有好处。像3842之类的无法满足,在这种应用中该淘汰了。设计的时候有个小技巧,可以设计满载刚好跑65K,载轻了马上降频。避免满载、3/4载等多个载都跑65K。

图6:轻载效率

下面把提升效率的几个常用方法列出:

提升变压器感量;变压器用大一号的磁芯;选择轻载降频的IC;增大bus电容,主要是提升低压输出时候的平均效率。这个看bus电压的波动情况,到一定值对效率影响就很有限;减小Cds电容(针对有EMI预设计的情况);优化MOS的RCD吸收,一般是减小C增大R;优化副边二极管的吸收,一般是减小C;OCP能在原边做的就不要在副边做,减少采样电阻的损耗;采用Qg小Coss小的MOS,这个不一定会贵,需要多找不同家的对比;对于低压大电流的情况,需要使用低VF的二极管,同时变压器的副边可以考虑采用多股线。这个会增加成本;采用性能更好的MOS和二极管。(此法一般不轻易用,只是作为对策的完整性列出)相信通过上面的调整设计,对提升效率到六级能效是没有问题的。

降低空载损耗的几个常用方法:

1、IC的选择,选择低工作电流的,现在一般是0.5mA左右,同时VCC电压在满足供电的前提下尽量低。

2、高压启动,启动后切断启动线路的最好。这个在早期一般是外加电路实现的,现在都集成在IC内部了,缺点是增加成本和空间。对于小功率的,启动时间在2~3S内的,用普通启动就可以实现,一般不会采用高压启动线路或者IC,出于成本和空间的考虑。

3、现在的IC,空载都是跑burst,降低burst的个数和频率。

4、降低驱动损耗,选择低Qg的MOS。

5、降低变压器的寄生电容。

6、关于RCD,这里要说明一下,合理的设计,RCD电路对空载损耗的影响几乎可以忽略不计。实测有没有RCD的差异在2mW左右。

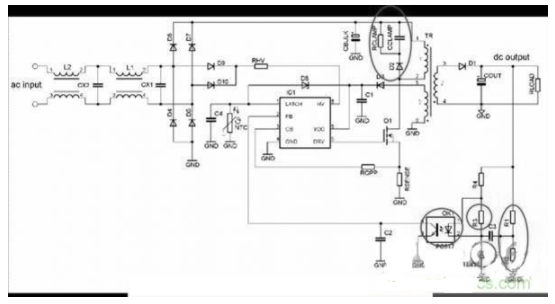

7、副边线路的优化(此部分优化前后可以有20mW~30mW的差异,影响很大。详见下图):

图7:副边线路的优化

A、选择高CTR的光耦;

B、在满足稳定的条件下,尽量提升R1、R2的值;

C、431的选型,有高低工作电流之分,典型的为1mA,也有0.5mA甚至更低。选择低工作电流的损耗低,但成本会上升,而且抗干扰能力降低,需要折中考虑;

D、选择了低工作电流的431后,可以将R3加大,甚至取消。

其实,对于降低空载损耗,最主要的算以上的第二条和第七条。在副边线路已优化的情况下,如果还要进一步降低损耗,比如30mW、10mW甚至更低的要求,此时主要看IC的解决方案,外围电路再优化也无济于事。

编辑:hfy

-

如何降低开关电源空载损耗2025-03-17 1023

-

揭秘怎样提高开关电源待机效率2011-12-14 7593

-

5种方法如何提高开关电源效率?2015-12-18 17214

-

高效率开关电源设计与制作2016-06-12 5413

-

优化低成本BJT开关方案可满足DoE和CoC新效率标准2018-10-10 1956

-

高功率因数低空载损耗AC/DC电源的研究2009-07-15 1233

-

如何提高开关电源效率2017-03-22 1555

-

开关电源内部的各种损耗的研究2019-06-20 6185

-

开关电源内部的损耗有哪些2022-03-21 5508

-

开关电源内部的损耗概述2022-08-12 1732

-

干货 | 如何降低晶体管和变压器损耗,提高开关电源效率?2023-01-05 1250

-

如何降低晶体管和变压器损耗提高开关电源效率2023-01-25 4956

-

怎样提高开关电源效率2023-08-27 4721

-

开关电源的空载电压怎么用开关电源智能测试系统测量?2024-02-02 1870

-

开关电源的效率优化方法 如何定制开关电源解决方案2024-11-29 5148

全部0条评论

快来发表一下你的评论吧 !