如何测量由于电源噪声和纹波引起的抖动

描述

低电平组件需要超稳定的电源,而高速数字信号则需要具有可重复的边沿转换时间。数字信号的两个方面是相关的,您需要抑制电源噪声的所有方面以减少数字系统中的抖动。在设计调试期间,如果要隔离和消除电源噪声源,则需要在整个电路板上收集测量结果。这是您如何隔离直流线上会引起抖动的确定性强噪声源的方法。

电源噪声和抖动源

如果您曾经覆盖过数字信号的时域轨迹,那么您就对抖动很熟悉。该术语(有时与相位噪声互换使用)是指数字信号的边沿触发和通过逻辑电路的传播延迟中的波动。抖动与电源噪声密切相关,在电源噪声中,直流电源电平的波动会导致数字信号延迟触发或延迟触发。下表显示了一般半导体器件和PCB中电源噪声的主要来源。

| 噪声源 | 噪声类型 | 描述 |

| 开关噪声 | 周期 | 产生于开关调节器中的开关元件 |

| 高斯噪声 | 随机 | 由电容电阻能级的热波动引起,这通常不是电子设备中考虑的比较大噪声源 |

| 1/f噪声 | 随机 | 这主要于你的元件中的半导体晶格缺陷有关,尽管没有1/f噪声的单一来源 |

| 漂移 | 伪随机 | 这是局限在低频率,频率成分可以随时间变化 |

| 瞬态响应确定性 | 确定的 | 当一个系统有多个时钟时,这通常看起来是随机的,但是通过一些分析,你可以确定哪些组件是这种噪声的主要驱动因素 |

该表中的最后一项是最值得关注的一项,因为它对抖动的影响很大。PDN设计和分析中经常提到〜1 ps / mV的抖动灵敏度值。对于具有高电源电平和低上升时间(例如分别为3.3 V和〜1 ns)的器件,纹波引起的抖动可能仅在5%纹波时不会上升到15%以上。但是,随着组件变得越来越小以及开关速率增加,抖动和电源电压纹波的容差也越来越严格。

降低抖动需要在两个方面抑制电源噪声的影响:

在PDN上:您需要将PDN设计为低纹波,以防止强烈的抖动。如果您可以降低到几mV RMS纹波电压,那么您的PDN设计就做得很好。

时钟抖动:所有时钟对各种噪声源都有自己的敏感性,这会影响时钟信号输出的抖动。PDN应该设计为始终具有低纹波,但是时钟信号中的抖动仍会在组件的输出上产生抖动。这是由于在其他组件中锁存和触发位转换时出错。

当您拥有多个系统时钟时,最后一点将变得更加困难,并且您需要确定对抖动影响比较大的时钟。对于系统时钟,或来自单个源的多条时钟线,您可能可以查明特定组件的抖动源。通常,多个时钟将导致PDN上的瞬态纹波,然后造成系统中其他位置的抖动。自然抖动也有一个下限,与瞬态纹波无关。这只能通过使用PLL锁定到更稳定的参考振荡器来清除。最后,一个PDN部分(例如5 V)上的噪声可能会在另一PDN部分(例如3.3 V)上产生噪声。

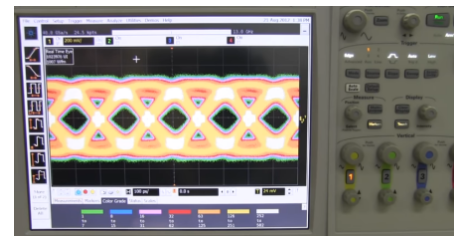

如果可以测量抖动和电源噪声,则可以确定对组件中的抖动影响比较大的噪声源。您需要的主要工具是可以收集眼图的高带宽示波器。

如何测量由于电源噪声和纹波引起的抖动

对于某些示波器来说,测量抖动非常困难,因为它在观察波形时依赖于边沿触发。从视觉上看,在观察示波器迹线时抖动并不明显,确定抖动可能需要手动平移并叠加多个信号迹线,以量化抖动。这就是为什么量化电源噪声及其抖动的标准方法是使用高质量的示波器收集眼图的原因。

眼图测量显示抖动和电平变化

收集了特定组件的眼图后,您可以将其与时域中PDN上纹波的直接测量值进行比较。应当在多种情况下执行此操作,因为瞬态纹波导致的电源噪声不会增加。在这种情况下,PDN电压波动被表示为正交相加的复数。

对于示波器对PDN纹波的任何测量,请使用衰减系数尽可能低的探头,因为这将防止探头夸大您测得的电源噪声。此外,请注意示波器的带宽。PDN上的瞬变可以具有高达〜1 GHz的频率分量。仅使用需要收集准确测量值的带宽,因为这将使您看到PDN纹波中所有可能的毛刺。

您可能希望从时域PDN纹波测量中看到FFT结果。强大的高频噪声源对背景噪声非常明显

进行时域测量后,如果有多个有源组件,您将无法查看哪个开关组件或时钟是造成纹波的主要因素。而是将数据带入频域。功率谱中的任何强峰值将对应于某些组件或时钟在指定频率下的切换。然后,您可以采取措施减少所标识组件产生的纹波,例如添加去耦/旁路电容器或确保相关PDN上的更大的平面间电容。

编辑:hfy

-

怎样去正确的测量电源纹波噪声呢2021-11-01 2535

-

分享电源纹波和电源噪声的区别2021-11-17 1451

-

电源纹波如何测量呢?2023-01-29 1133

-

开关电源的纹波和噪声2010-09-10 1039

-

开关电源产生纹波和噪声的原因和测量方法2010-12-21 9314

-

为什么不同示波器的纹波噪声测量结果总是不同2018-01-20 8947

-

示波器是测量电源纹波和电源噪声的必备工具2018-03-12 20924

-

纹波噪声的常见测量工具探头的应用介绍2020-10-30 2595

-

电源纹波和电源噪声有什么区别?2021-11-10 1204

-

电源纹波和噪声及其测量和改善方法2022-01-05 1000

-

电源纹波怎么测量,纹波和噪声的区别2022-10-27 12181

-

如何合理测量开关电源输出纹波噪声2023-06-07 5796

-

直流电源纹波噪声指标该如何测量2023-10-10 4613

-

如何测量电源的纹波噪声2023-11-06 1697

-

电源轨噪声对系统时钟抖动的影响2024-11-22 1541

全部0条评论

快来发表一下你的评论吧 !