电平触发器,脉冲触发器和边沿触发器的触发因素是什么

描述

数字时序 电路中 通常使用三种类型的触发器 :电平触发器,脉冲触发器和边沿触发器。现在让我向您介绍这三个触发因素。

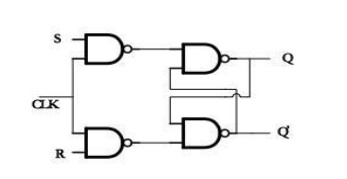

脉冲触发

如上图所示,脉冲触发器由两个相同的电平触发的SR触发器组成,其中左SR触发器成为主触发器,右手侧称为从触发器。 该 电路也称为Master-Slave SR触发器 。脉冲触发的触发方式分为两步:第一步是当CLK = 1时,主触发接收输入端的信号,并设置为对应状态,从触发不动。第二步是当CLK的下降沿到来时,根据主触发器的状态将触发器翻转。因此,Q和Q'的输出状态变化发生在CLK的下降沿。

电平触发

如上图所示,电平触发的逻辑结构图和图形符号图仅在CLK为高电平时才可以接受输入信号,并根据输入信号将触发输出设置为对应的输出。它由一个SR触发器和两个NAND门组成,也称为同步SR触发器。

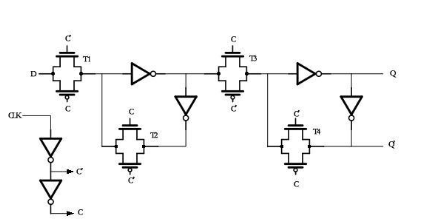

边沿触发

如上图所示,主要在COMOS集成电路中使用的边沿触发电路结构实际上是由两个CMOS传输门组成的电平触发D型触发器。

当CLK = 0时,TG1打开TG2,TG3关闭TG4。

当CLK = 1时,TG1关闭TG2,TG3打开TG4。

边沿触发器 的次级状态 仅取决于时钟信号的上升沿 或下降沿到来时输入的逻辑状态,并且输入信号在此之前或之后的变化不会影响输出状态触发器的

根据逻辑功能的不同特性,时钟控制的触发器通常可以分为SR触发器,JK触发器,T触发器和D触发器。触发器是数字设计中必不可少的时序逻辑单元, 它使电路具有 存储功能 。顺序逻辑电路和组合逻辑电路的结合使数字电路成为无限可能!

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

d触发器是电平触发还是边沿触发2024-08-22 3356

-

同步触发器和边沿触发器的区别2024-08-12 4019

-

边沿触发器的工作速度高于主从触发器的原因2024-08-11 2031

-

边沿触发器和主从触发器的区别是什么2024-08-09 3418

-

边沿触发器和脉冲触发器有什么区别2024-07-27 10215

-

脉冲触发器和边沿触发器的区别在于什么2024-02-06 7423

-

请问电平触发器和边沿触发器符号是什么?2019-10-18 2783

-

什么是边沿触发器_边沿D触发器介绍2018-01-31 73437

-

边沿触发SR触发器2010-08-10 7200

-

D触发器,D触发器是什么意思2010-03-08 5417

全部0条评论

快来发表一下你的评论吧 !