无故障高速电路设计的信号完整性分析

电子说

1.4w人已加入

描述

在高速电路设计中,元件和元件封装可能影响芯片内以及PCB的信号完整性。实际上,信号完整性包括一组确定信号质量的测量值,作为分析和减轻噪声,失真和损耗影响的一种方法。这是一组设计实践和测试,有两个常见的信号完整性电路设计问题,即信号的时序和质量。信号应按预期到达目的地吗?到达那里后状况?

在高速电路设计项目中,信号完整性(SI)是获得设计成功的必备条件。因此我司会对设计的电路板进行信号完整性分析,以确保产品完整性和无故障高速电路设计。而我们的信号完整性分析如下:

1、布线前后的高速信号完整性分析和仿真

2、28GHz +收发器和40GHz +封装级仿真

3、信号完整性驱动的层堆栈和约束生成

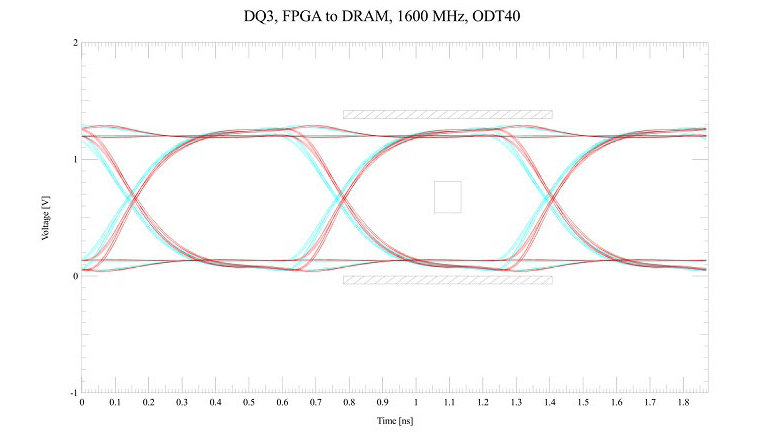

4、针对复杂拓扑的网络调度和设计优化,例如多点总线(DDR3,DDR4)

5、减少反射和串扰,以改善时序裕度和发射

6、优化去耦,实现电源完整性和较低成本

7、同时考虑开关噪声和设计策略

8、组件和系统特性,包括完整的S参数,增益和噪声系数优化

9、针对敏感信号和监管批准的屏蔽设计和分离平面优化

10、比吸收率(SAR)分析

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

高速电路设计与信号完整性分析2024-09-25 968

-

高速电路信号完整性分析与设计—端接与拓扑2022-02-10 862

-

高速电路设计中的信号完整性问题是什么?怎么解决这些问题?2021-06-03 1599

-

高速信号的电源完整性分析2012-08-02 3623

-

高速电路信号完整性分析与设计—电源完整性分析2012-05-29 3199

-

高速电路信号完整性分析与设计—高速信号完整性的基本理论2012-05-25 2121

-

高速电路信号完整性设计培训2010-04-21 4182

-

高速电路设计中信号完整性分析2009-10-14 19742

-

高速电路的信号完整性分析2008-10-15 1407

-

高速电路信号完整性分析之应用篇2006-05-28 1125

全部0条评论

快来发表一下你的评论吧 !