浙大与电子工程学院发表的研究荣获最佳论文奖

电子说

描述

近日,IEEE国际可靠性物理会议(IEEE International Reliability Physics Symposium, IRPS)公布了2020年的获奖论文。浙江大学信息与电子工程学院赵毅教授团队发表的关于超小尺寸FinFET器件自热效应的研究荣获最佳论文奖(Best Paper Award),这是来自中国的研究成果首次获此荣誉。那么接下来请随小编一起看看他们做的研究吧!

研究背景

为了进一步缩小电子器件尺寸,半导体产业界自22nm起引入三维立体结构的鳍式场效应晶体管(FinFET)制造逻辑开关器件。不同于传统平面硅基器件所具备的良好的导热性能,这一特殊结构会使晶体管工作时,沟道电流产生的热量不断积累,器件工作温度升高,从而导致器件性能退化。在FinFET应用之初,自热效应就已被认为是未来的10 nm、7nm和5 nm这些技术节点下的关键难点。而如今, FinFET已在高性能、低功耗的逻辑器件制造中有着广泛的应用,但严重的自热效应仍是影响器件稳定性和可靠性的重要因素,随着技术节点持续缩进,晶体管结构中的侧限和声子散射开始制约沟道热量散逸,其引发的温度上升不仅加快了集成电路的老化与失效,也使让电路的可靠性测试变得复杂。

近日,IEEE国际可靠性物理会议公布了2020年的获奖论文,浙江大学信息与电子工程学院赵毅教授团队在FinFET自热效应方面的研究成果论文“In-Situ Monitoring of Self-Heating Effect in Aggressively Scaled FinFETs and Its Quantitative Impact on Hot Carrier Degradation Under Dynamic Circuit Operation” 荣获最佳论文奖(Best Paper Award),该论文第一作者为课题组研究生博士研究生曲益明,通讯作者为赵毅教授。这也是来自中国的研究成果首次获此荣誉。

基本特性

赵毅教授团队曾于2017年IEEE国际电子器件会议IEDM上发表了团队自主开发的电学特性表征系统,并在此基础上运用皮秒级脉冲电流-电压扫描技术,成功捕捉了晶体管产热和散热的过程中漏极电流的变化,并评估了自热效应对电路中晶体管器件的热载流子注入效应的影响。

赵毅教授团队基于上述成果深度开发了超快速亚纳秒测试系统,国际上首次对动态电路下先进FinFET器件的自热效应进行了原位监测,将所提取的瞬态温度应用到了器件可靠性退化行为的评估与模型建立中。

研究模型

本次研究中将多鳍SOI FinFET器件作为测试模型。在有着200nm厚度SiO2层的晶圆上制造22nm栅长的FinFET晶体管,HfO2基栅介质的等效氧化层厚度为0.9nm。为了抑制关-开过程中局部自热的产生和传播,采用了脉冲发生器对待测器件的栅极进行脉冲偏置,其上升边缘仅为20皮秒。

图(a)多鳍SOI FinFET器件结构示意图;图(b)栅极脉冲波形图;图(c) 漏电流响应波形;图(d) SOI FinFET器件中单鳍的温度分布。

部分测试结果

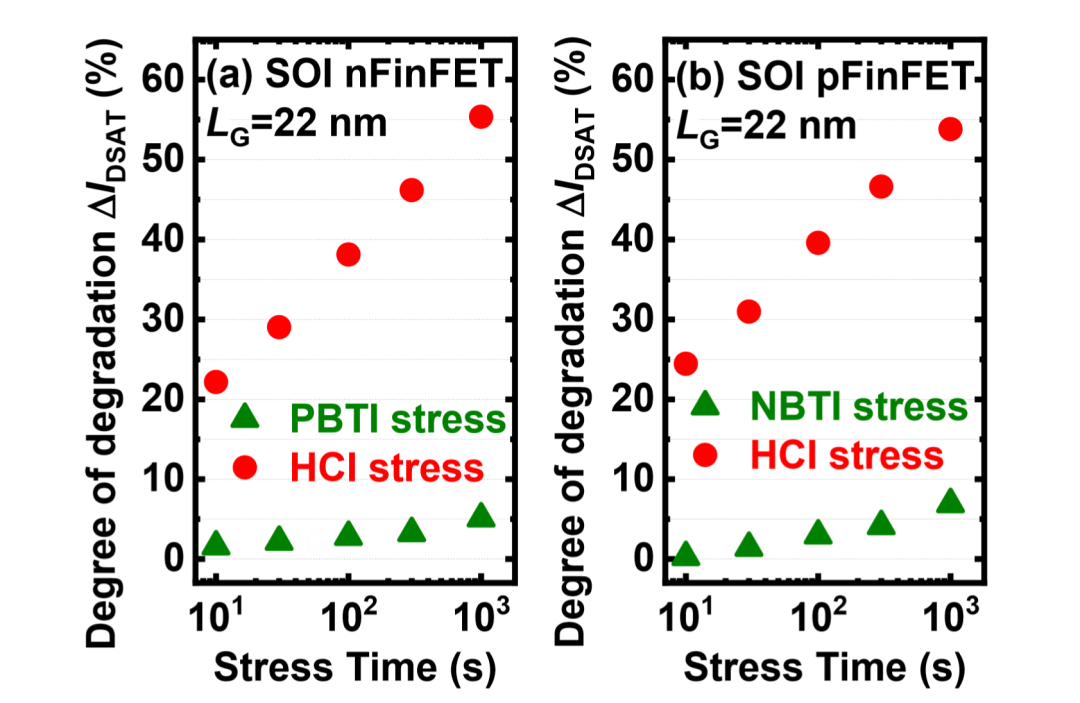

研究团队设置1.1V的应力电压以研究动态电路下的热载流子注入和偏置温度不稳定性,相关测试结果见下图:

偏压温度不稳定和热载流子退化对n型/p型FinFET器件的饱和漏极电流的影响

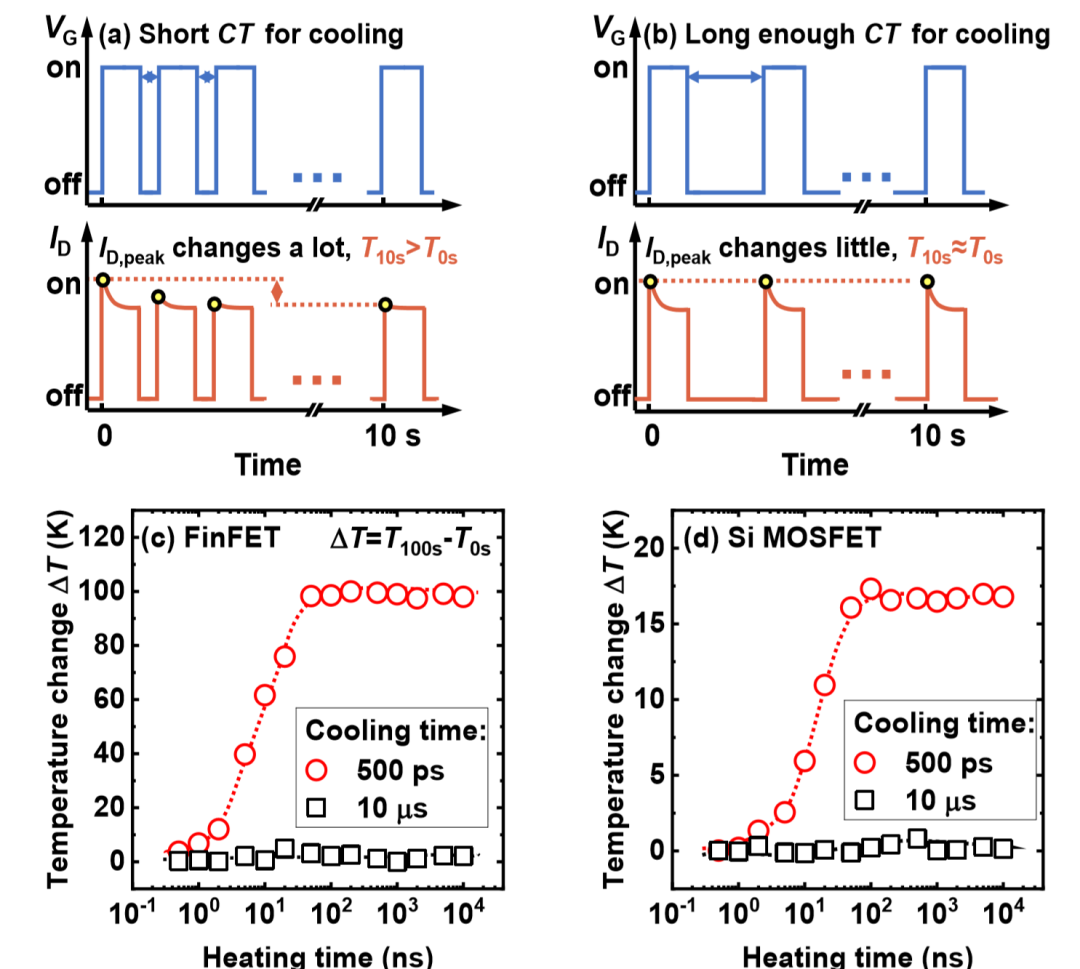

SOI FinFET与平面硅MOSFET的响应漏极电流

上图可看出,在施加栅极电压Vg后,漏电流曲线上出现了一个维持数纳秒的平峰(“peak plateau”),这表明从沟道温度上升的过程需要几个纳秒的时间来完成。因此瞬态沟道温度和漏极电流的关系可以近似看做Id与周围环境温度的关系,见下图。

组图为获得瞬态温度值的过程示意图

短冷却时间和充足冷却时间下的Vg-Id示意图

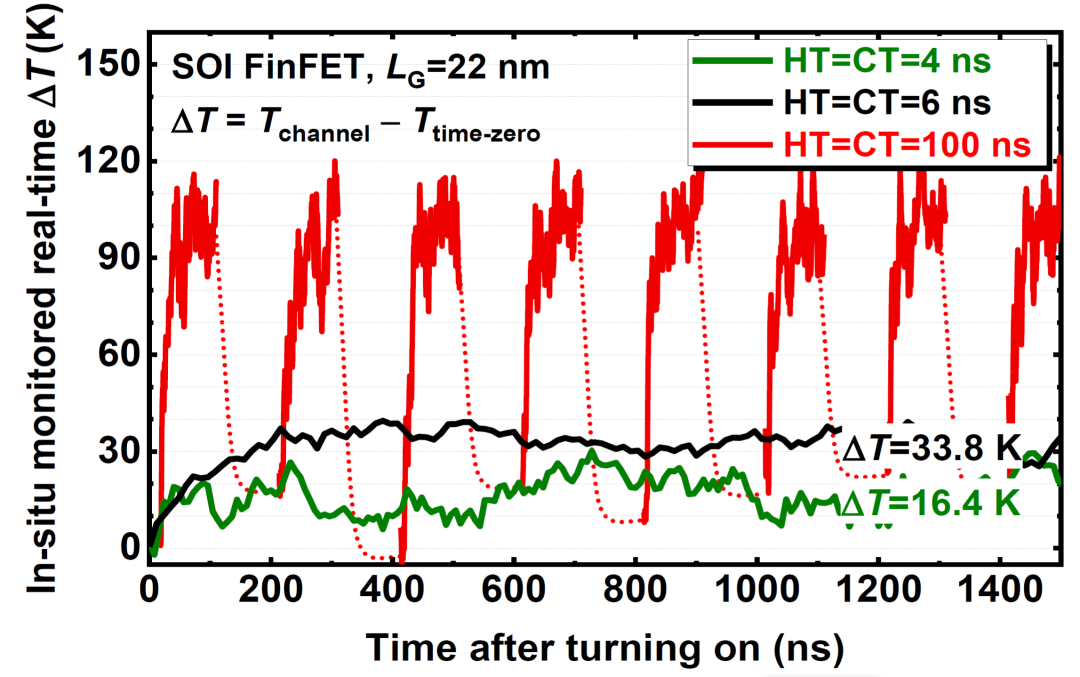

在不同电路速度的 AC 信号下,原位动态监测得到的 FinFET 晶体管沟道温度变化

应用前景

自热效应已经成为10纳米及更先进集成电路节点中最为严重和最受关注的可靠性问题,赵毅教授团队的此项研究成果不仅对于器件研发有重要意义,也为电路设计者在设计电路时钟和器件布局时提供了参考。小编也很期望看到本项成果能在未来先进集成电路制造工艺中得到应用,以提升电子器件的良率与可靠性,降低集成电路产品的生产成本,并延长其寿命。

原文标题:科研前线 |浙大赵毅团队关于超小尺寸FinFET器件自热效应研究论文首获IEEE IRPS 2020最佳论文殊荣

文章出处:【微信公众号:芯片揭秘】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

南京工程学院,电子CAD课程设计,dxp20042014-12-26 5884

-

2015 年硕士研究生招生2015-04-20 2874

-

首届“唐辉电子”杯中国智能仪器仪表设计大赛完美落幕,第二届大赛正式开始,一年一届,欢迎参加!2016-05-20 3594

-

【新闻】西电通信工程学院召开2022级通信工程卓越班新生见面会2022-12-08 916

-

MathWorks宣布吉林大学汽车工程学院采用MathWorks产品2011-02-09 971

-

科研年报 机械与动力工程学院2011-04-28 1189

-

最受欢迎工程技术人才 全球最佳50大工程学院排名(图文)2012-07-17 18914

-

决赛:智能车竞赛电磁组之电子科技大学信息工程学院2018-06-21 3283

-

洲明智慧综合杆及智能交通专项工程荣获最佳工程奖2022-08-27 2795

-

高云半导体与越南孙德胜大学电气与电子工程学院开展交流合作2024-04-24 2043

-

“仲恺农业工程学院与深圳信盈达科技有限公司”揭牌仪式举行2024-05-18 1323

-

智慧机械·创新未来 | 思看科技 X 浙大机械工程学院产教融合研讨会成功举办!2024-06-12 1148

全部0条评论

快来发表一下你的评论吧 !