西安交大在GAA晶体管自热效应研究模型取得新成果

电子说

描述

本期分享的研究成果是来自西安交大微电子学院在GAA晶体管自热效应研究模型上的成果,通过提出和验证声子边界反射等现象对自热效应和热导率的影响,研究团队建立了更加精确的物理模型,以便能更好模拟GAA晶体管的实际工作状态。接下来就请随小编一起来看看具体的研究内容吧~

研究背景

在集成电路研究领域,从实验到各种热电特性模拟的广泛研究都表明了自热效应对集成电路器件性能与可靠性的负面影响,尤其是在诸如FinFET和GAA晶体管的多门场效应晶体管管中,由于材料热导率、晶体管结构、界面热阻以及10nm以下尺寸器件的高功耗密度等因素的存在,使得先进制程芯片设计变得越来越具挑战性。

要对晶体管中自热效应引起的温度分布进行准确的描述,需要对器件的热学特性建立精密准确的分析模型。因此,作为探究器件热可靠性的基础,针对纳米尺度下的热量产生与分布的理论研究与实验广泛开展,发展出了各种不同的分析模型。

近日,西安交通大学微电子学院研究团队在全环栅(GAA)晶体管的自热效应研究上取得了新进展,其研究成果以“Study on Degradation Mechanisms of Thermal Conductivity for Confined Nanochannel in Gate-All-Around Silicon Nanowire Field-Effect Transistors”发表于IEEE Transactions on Electron Devices,博士研究生赖俊华为本文的第一作者,西安交大张国和教授与中科院微电子所卜建辉研究员为本文的共同通讯作者。

基本特性

研究团队提出了一种考虑纳米通道截面和长度的热导率分析模型,用于精确模拟GAA硅纳米线晶体管中的自热效应,并得到了实验数据的验证: 纳米通道长度引起的热导率下降通过横向声子的等效平均自由程来描述,其结果显示,相比完全耗尽型SOI(以下简称:FD-SOI)晶体管中的超薄硅,GAA硅纳米线晶体管的热导率下降幅度大得多,随着纳米通道长度的减少,热导率显著降低,这个现象在建立自热效应研究模型时需要着重考虑。

模型建立与解析

为了更准确的评估器件的自热效应,团队在建立FD-SOI场效应管模型上做了大量工作,在现有模型的基础上,进一步引入自由态和束缚态电子的散射机制以及声子边界反射等影响因子,并揭示了3D晶体管器件的热导率在纵向坐标的相关性。接下来是一些相关的结构原理图和测试结果图。

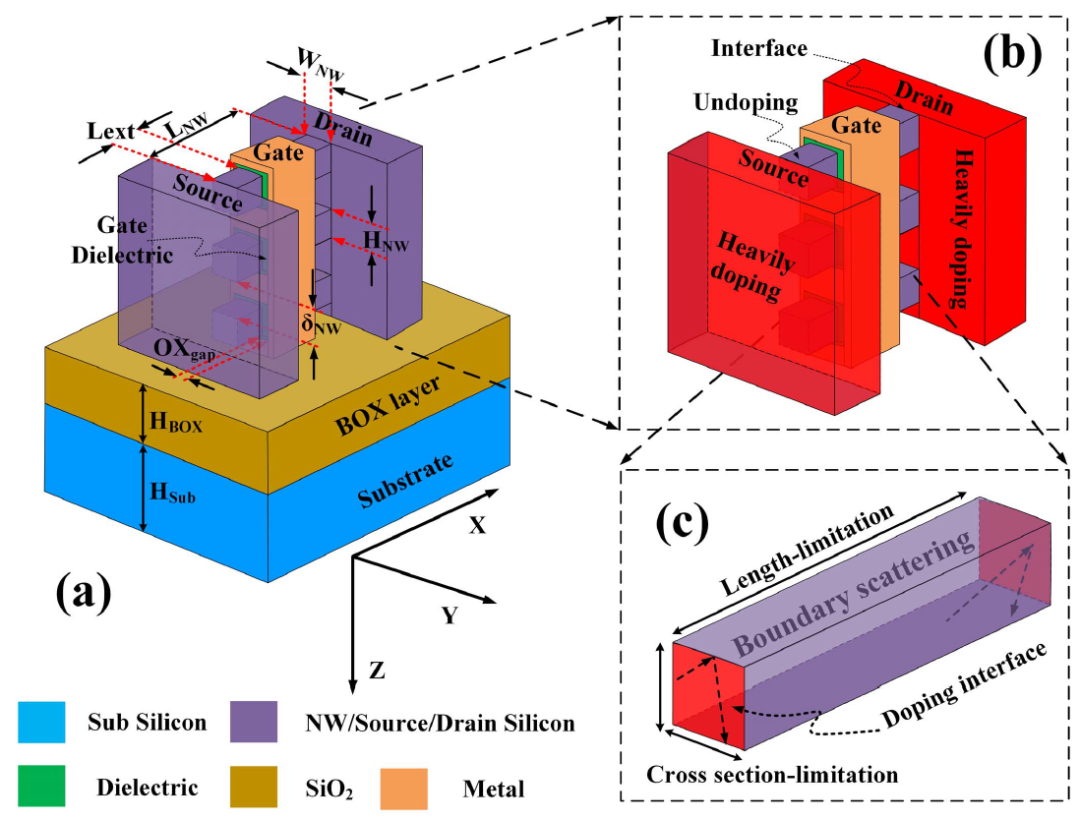

图(a)GAA纳米线晶体管原理图及对应坐标系和物理参数;图(b)掺杂剖面;图(c)受沟道限制的声子散射边界

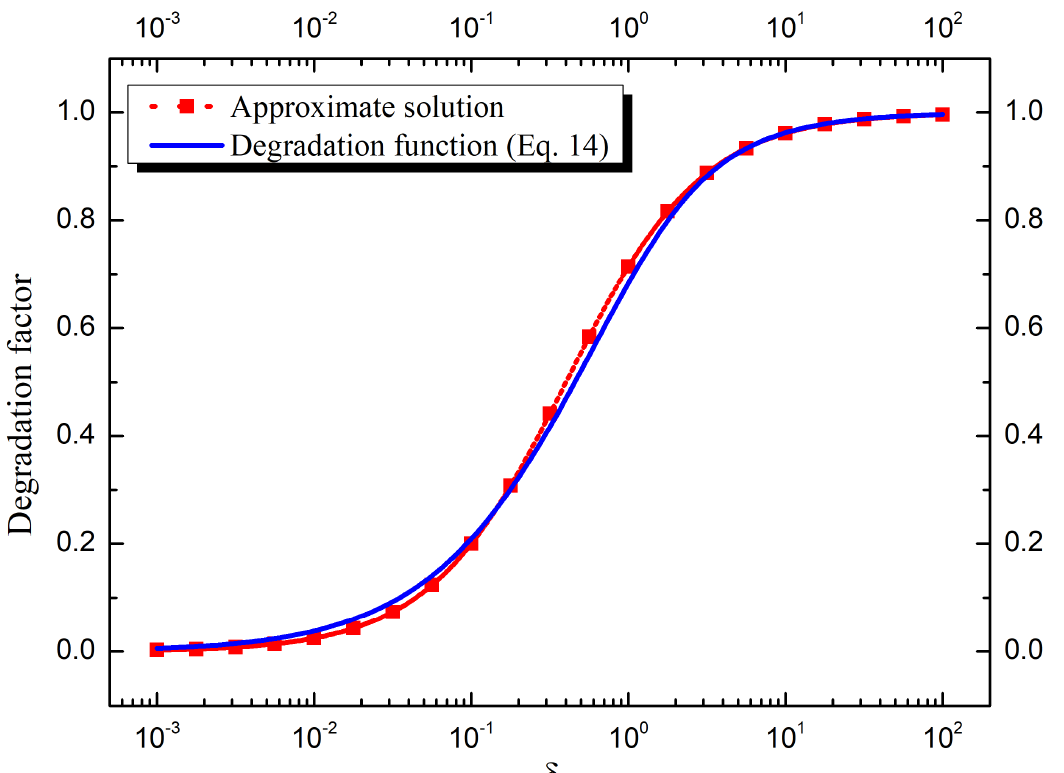

FD-SOI晶体管热导率的变化函数及其近似解

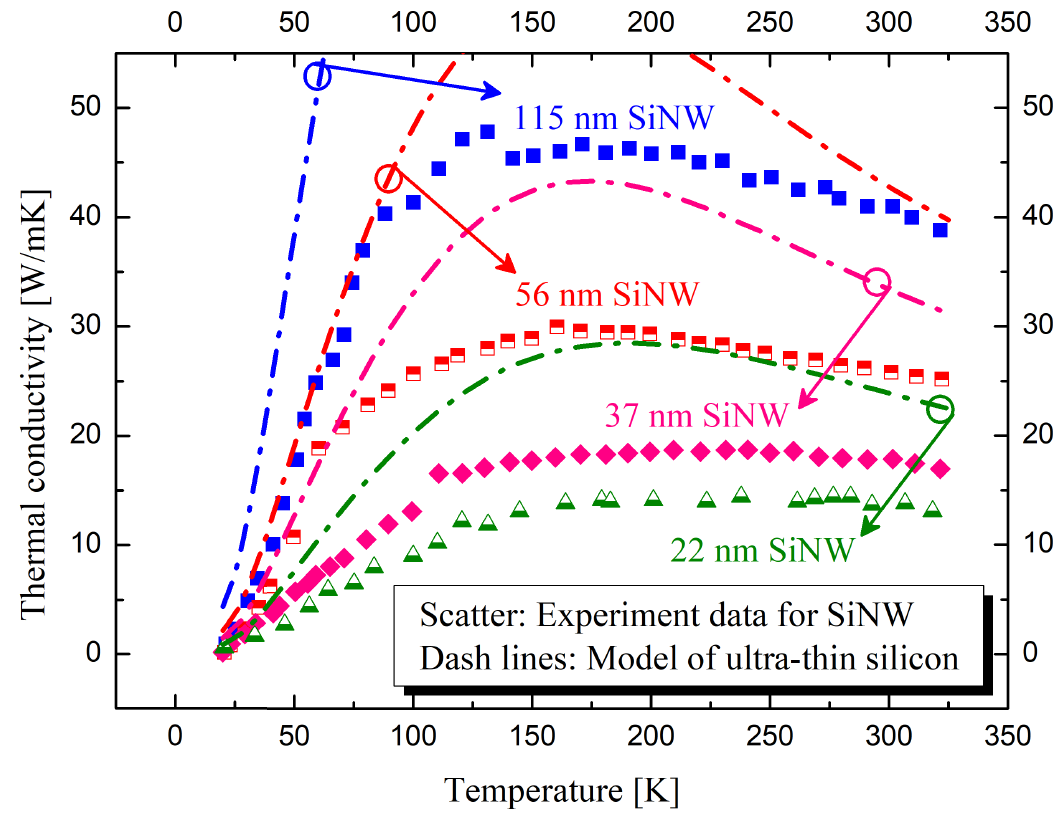

FD-SOI晶体管的超薄硅膜通道与硅纳米线通道的热导率变化曲线对比

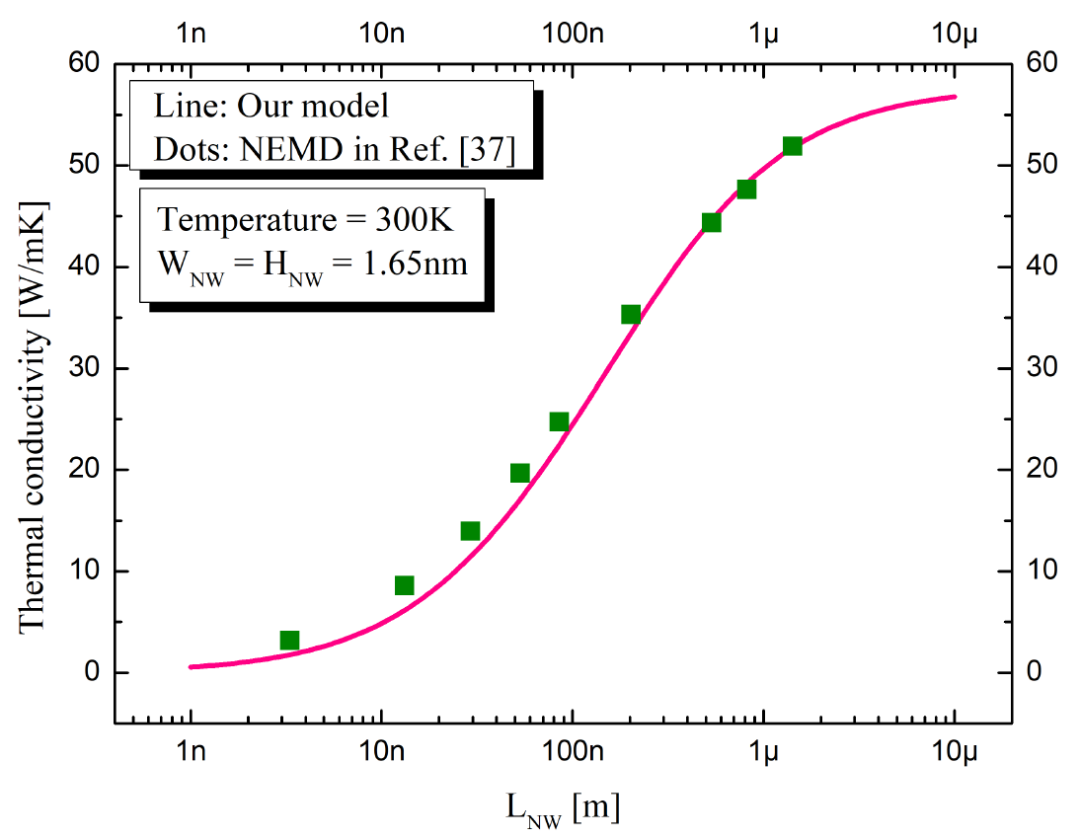

受纳米通道长度引起的纳米通道导热率变化对比:GAA纳米线测试结果与非平衡态分子动力学模拟结果对比

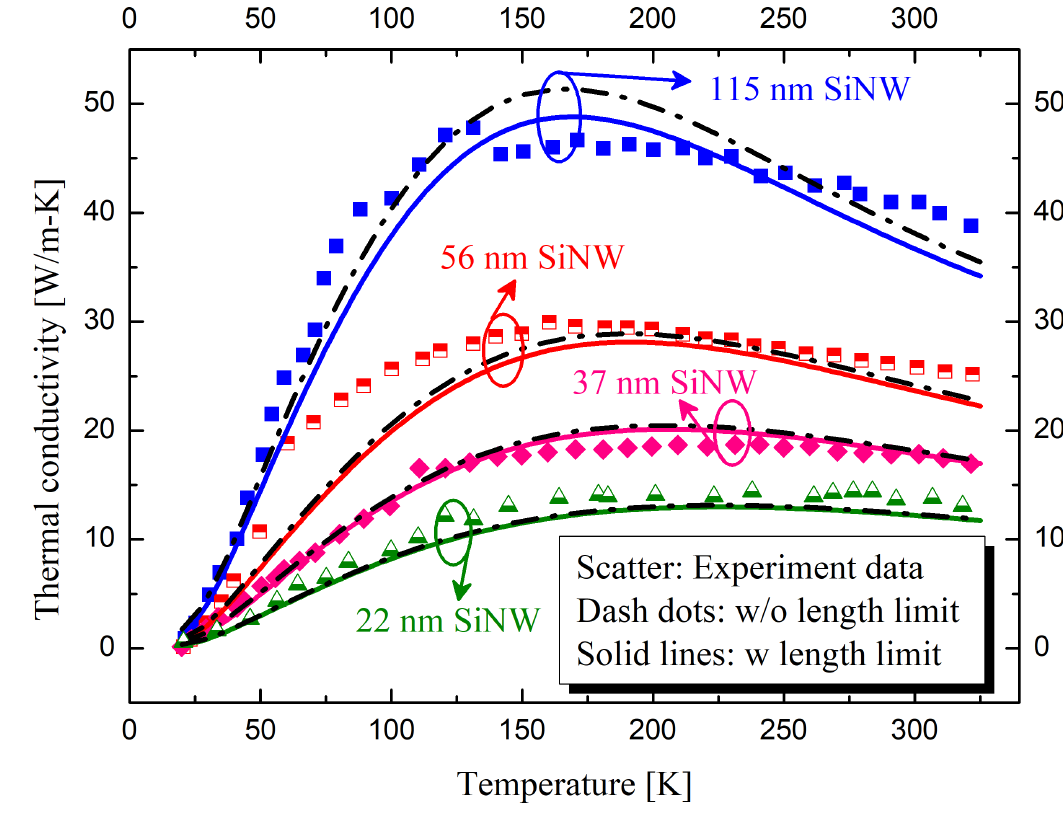

不同尺寸下的纳米通道在有/无通道长度限制影响条件下的热导率变化曲线

上图结果表明,考虑纳米通道长度限制后,导热系数的预测值整体出现降低。随着通道长度逐渐接近截面尺寸,通道长度的限制会导致热导率的大幅减小。

应用前景

作为制约摩尔定律延续因素之一的自热效应,其存在对于器件性能与寿命有着很大的影响,本成果针对GAA纳米晶体管自热效应特性模型的创新研究,完善了热导率物理模型,有望为缓解GAA纳米线晶体管工艺中的发热问题以及由此带来的热载流子注入等问题,期待该成果能够帮助芯片制造产业进一步提升工艺水准。

原文标题:科研前线 | 西安交大在GAA晶体管自热效应分析上取得新进展

文章出处:【微信公众号:芯片揭秘】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

互补场效应晶体管的结构和作用2025-01-24 4347

-

IBM与Rapidus在多阈值电压GAA晶体管技术的新突破2024-12-12 1061

-

西电郝跃院士团队在超陡垂直晶体管器件研究方面取得重要进展2024-02-20 1601

-

什么是鳍式场效应晶体管?鳍式场效应晶体管有哪些优缺点?2023-02-24 14583

-

剖析晶体管结构新变革以及GAA机遇与挑战2021-09-23 3193

-

石墨烯电路芯片的热效应研究分析2021-06-10 1295

-

Intel放弃FinFET晶体管转向GAA晶体管 GAA工艺性能提升或更明显2020-03-11 6741

-

场效应晶体管在电路中的特别应用,你未必全都清楚2019-04-16 3390

-

有机场效应晶体管研究取得重要进展2012-04-26 1373

-

热效应影响光束质量的数值模拟2012-02-22 778

-

晶体管的小信号模型2010-09-25 1239

-

晶体管自激多谐振荡器电路图2009-06-26 1923

-

场效应管与晶体管的比较2009-04-25 3672

-

低成本有机场效应晶体管研究取得新进展2008-11-26 539

全部0条评论

快来发表一下你的评论吧 !