应用通信调制解调器构建信号处理平台的系统级建模及仿真实验

描述

软件无线电或通信调制解调器等信号处理系统的质量取决于所选用的硬件平台性能。早期在设计方面的探索使设计师可以在寄存器传输级(RTL)和软件实现之前洞悉面临的挑战,了解性能与功耗改善所需的架构决策以及软硬件的划分。

另外,早期的设计探索还有助于架构方面的设计决策,从而为规划当前和未来需求提供便利。设计师还可以进一步拓展这些设计探索,以便开展故障分析,并确定进行验证的测试用例。

本文介绍的系统级建模和仿真方法,可以用来在设计流程早期为软件无线电或高速通信调制解调器设计信号处理平台的架构。

问题

先进的高速信号处理平台等大多数复杂系统都会经历昂贵的重复设计,超过70%的重复时间是由于设计决策错误或对需求的误解。此外,影响这些复杂系统的因素有很多,如低处理时延、低功耗、可配置能力和资源限制等。早期的设计探索有助于克服这些问题。

设计师和架构师有几种开展设计探索和分析的方法可供选择。虽然分析法可以提供有关最坏情况下执行时间的重要信息,但多数情况下这在实际应用中并不会发生。物理测试方法也许能提供精确的信息,但对于软件无线电或高速通信调制解调器等复杂系统来说是不可行的。

解决方案

利用离散事件仿真,设计师和架构师可在较短的时间内根据成百上千个使用案例、任务调度和系统配置,对目标系统进行评估。离散事件建模和仿真不仅有助于构建特别复杂的仿真模型,而且能够帮助架构师和设计师运行更多的用例。

此外,硬件架构组件与框架的预构建和有效库有助于软件架构的建模。它们可以提高系统模型的精度,缩短构建仿真模型的时间。

这种方法允许设计师:

● 专注于结果的分析和解释,而不用关心模型的构建;

● 采用不同的应用配置来执行仿真, 以便进行平台选择,做出软硬件决策,了解外设、性能以及目标架构上软件线程的分配,从而优化产品架构。

解决方案实现

对信号处理平台的设计进行探索,目的是为了了解处理延时、现场可编程门阵列(FPGA)缓冲器要求、数据包长度对性能的影响以及硬件平台配置的识别。进一步扩展这种探索,可以理解每个信号处理函数的资源使用情况,比如寻峰、相关器、加权乘法和累加器。

离散事件仿真模型使用以下组件:

·4个5MHz的ADC通道;

·512字节和1024字节长度的数据包;

·233MHz的FIFO;

·深度为1024的缓冲器;

·初始时钟速率为125MHz的FPGA。改变FPGA时钟速率可满足延时要求;

·运行在167MHz的外部DDR内存;

·运行在260MHz的ADSP TS201。使用VisualSim Architect的预构建可配置库以图形化的方式构建模型。使用Visual Sim的“System- Resource”库块对处理器、内存、FPGA资源、总线和互连进行建模。模数转换器(ADC)被建模为流量发生器,负责产生5MHz的数字样本。

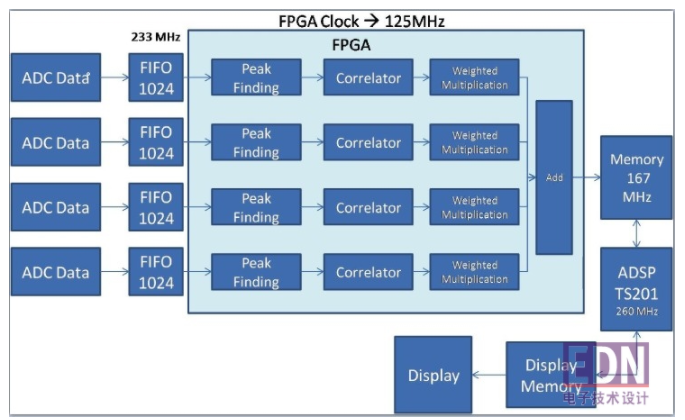

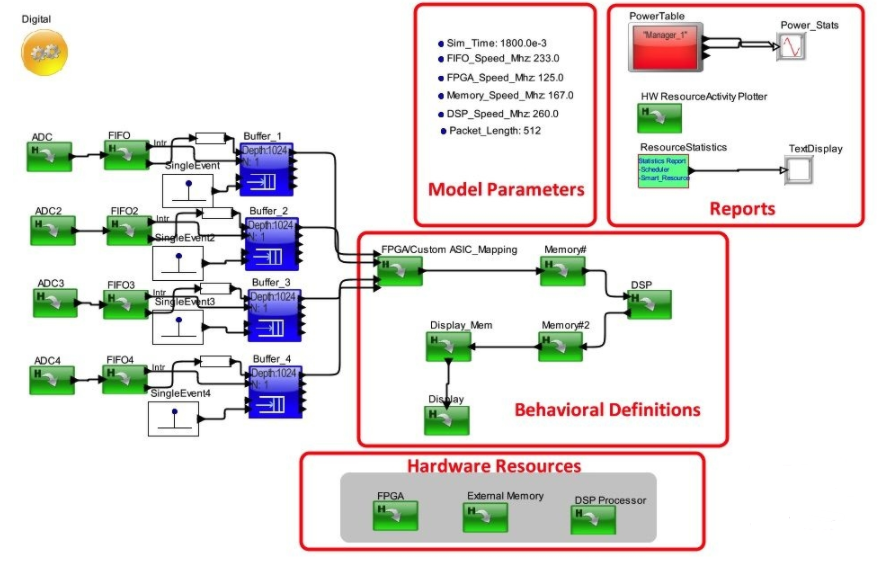

在这个系统设计中,我们为每个函数都考虑了抽象细节。利用这些细节,通过集成matlab/simulink/C/ C++模块,可以创建精细模型。对每个函数来说,我们已经考虑了运行在系统发生器中的现有Verilog代码的时序值和标准发布值。加权输入总和被转发给数字信号处理器进行显示处理和浮点FFT,处理后的结果数据被写进帧缓冲器用于显示。建议的系统平台框图如图1所示,VisualSim仿真模型如图2所示。

图1:系统框架(来源:Mirabilis设计项目报告)。

图2:信号处理平台的VisualSim模型(来源:Micabilis设计项目报告)。

分析与报告

模型的构建花了两个人时,仿真在拥有4GB RAM的2.6GHz微软Windows 10平台上执行,仿真的实际时间为900ms。VisualSim花了25s完成一次仿真。根据数据包大小得出算法处理结束的时间,并在功耗和性能之间做出折衷,是设计时要重点考虑的问题。

分析1

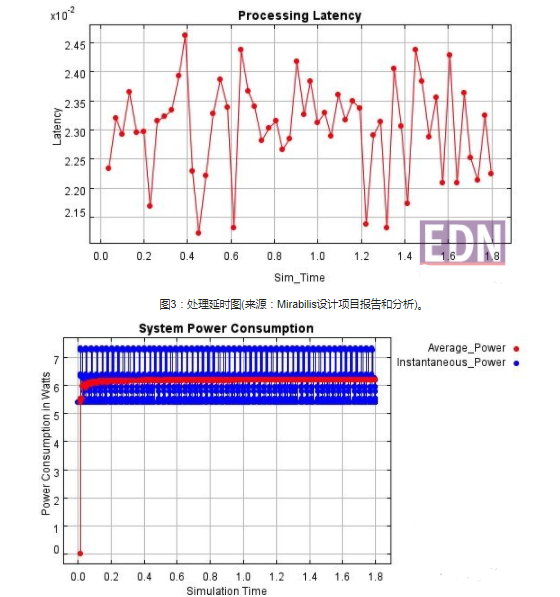

这个设计将缓冲器深度选为“数据包长度的”两倍,长度为512字节的包的信号处理时延有望在20ms以下。

图3显示的仿真报告表明,最大处理延时是24.52ms,这说明在FPGA上实现信号处理功能需要花更多的周期。克服这个挑战的解决方案是要么提高FPGA的时钟速率,要么修改算法。我们决定提高FPGA的时钟速率作为初步的解决方案。

图4:系统功耗(来源:Mirabilis设计项目报告)。

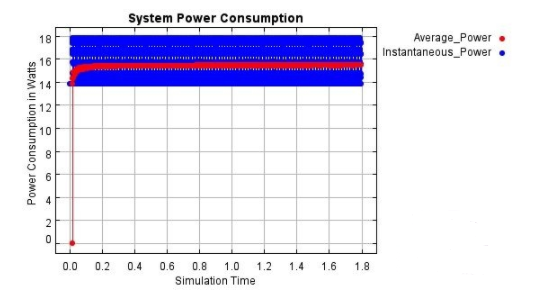

随着后续的研究,我们发现如果将FPGA的时钟速率从125MHz提高到170MHz,系统就能满足20ms的延时要求,而且我们发现平均功耗(6.2W) 只增加了1.1W。

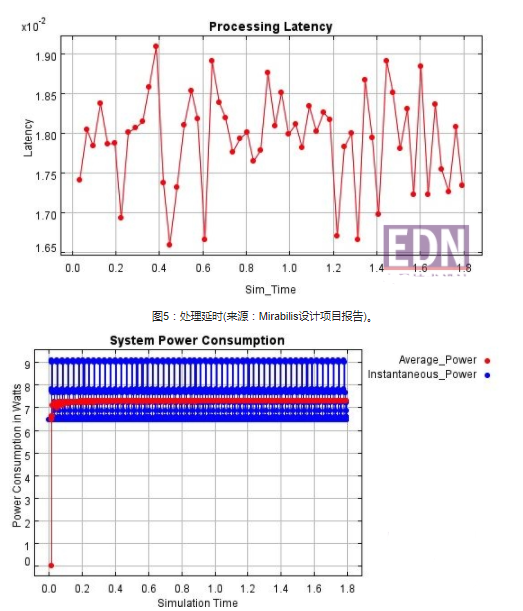

延时图形如图5所示,功耗图形如图6所示。

图6:系统功耗(来源:Mirabilis设计项目报告)。

考虑到有可能需要支持增加包长,我们将数据包长度从512字节增加到了2048字节以作进一步分析。我们发现,功耗没有明显的变化,但最大处理延时从期望的20ms左右增加到了76ms,系统的平均功耗为7.8W。

图7:处理延时(来源:Mirabilis设计项目报告)。

我们还观察了某些函数的缓冲器占用情况。表1表明,针对上述所有场景,每个函数缓冲器占用情况是一致的( 缓冲器占用以包数计量)。这意味着这种算法实现没有为了支持不同的数据包大小而进行优化,而且如果设计要求不同的包大小,这种实现也是不可行的。

表1,缓冲器要求

分析2

在这次探索中,我们为每个ADC通道的每个函数建立了专用资源模型。

我们通过查看处理延时图形和平均功耗图形来评估系统配置。

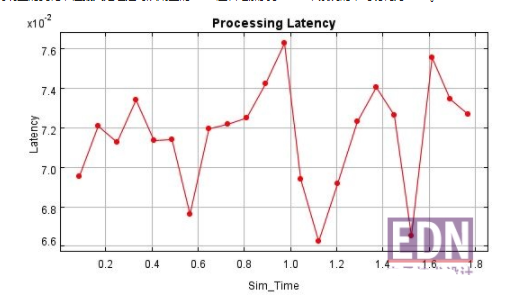

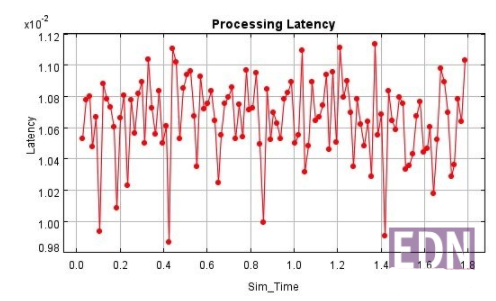

处理延时如图8所示,平均功耗如图9所示。

图8:处理延时(来源:Mirabilis设计项目报告)。

由于每个ADC通道的每个函数都有专门的FPGA资源,因此,与分析1 所示的平均系统功耗相比,这次系统的功耗增加了很多。不过平均的端到端延时小于10.8ms,寻峰延时为11.1ms。

图9:平均功耗(来源:Mirabilis设计项目报告)。

这表明,如果每个ADC 通道都考虑使用专门的FPGA资源, 即使FPGA时钟速率较低也能满足性能要求。不足之处就是FPGA资源要求更高了,而且平均功耗增加了100%。

小结

使用建模和仿真方法进行早期的设计探索可以验证实现信号处理的硬件能力和效率,从而确保所选的架构有足够的处理能力来满足系统在性能、功耗和可靠性方面的要求。利用VisualSim性能建模可以帮助我们估计资源要求、性能和功耗统计数据, 进而做出正确的设计决策。

在研究过程中我们发现,系统架构师可以通过“分析1”做出平衡系统性能和功耗的设计决策。“分析2” 则表明,即使用较低的时钟速率也可以实现系统性能,但要求更多的FPGA资源,并且功耗要求增加了几乎一倍。

通过构建硬件资源的周期精确模型并进行微架构级的研究,上述探索还能进一步扩展。

编辑:hfy

-

通信和电信>xDSL 调制解调器/DSLAM2012-12-24 2621

-

线缆调制解调器的原理是什么?2019-09-27 3166

-

嵌入式系统上的调制解调器通信该怎样去实现呢?2022-12-27 659

-

调制解调器(MODEM)介绍2009-08-01 5615

-

调制解调器(Modem)2009-12-17 1250

-

什么是Modem(调制解调器)2009-12-28 2155

-

调制解调器(Modem),调制解调器(Modem)是什么意思2010-03-19 3885

-

调制解调器(Modem)是什么_调制解调器(Modem)有什么功能?2017-10-27 60842

-

什么是手机调制解调器_调制解调器的作用是什么2020-06-11 21742

-

基于VHDL的MSK调制解调器的建模与设计2023-10-18 588

-

调制解调器是什么设备 调制解调器的主要功能是2024-01-22 14649

-

调制解调器的主要功能是 调制解调器的解调是什么意思2024-01-25 4825

-

调制解调器的工作原理 如何选择调制解调器2024-11-08 5522

-

如何提升调制解调器的信号强度2024-11-10 2039

-

调制解调器的配置与调试2025-01-21 2740

全部0条评论

快来发表一下你的评论吧 !