基于HCS12X系列单片机中的XGATE协处理器提高应用系统定时的精度

电子说

描述

μC/OS-II最多支持63个任务,并支持信号量、邮箱、消息队列等多种进程间通信机制;同时,用户可以根据需求对内核中的功能模块进行裁剪。将μC/OS-II应用到嵌入式系统中,对于提高产品的质量、缩短开发周期和降低成本都有重要的意义。

为了保证系统的实时性,μC/OS-II采用查表策略,使优先级最高的任务一旦进入就绪态就立刻可以运行。这种查表算法与应用系统的任务数目无关,执行时间是固定值,从而保证了系统的硬实时性。μC/OS-II实时内核中唯一一个执行时间受任务数目影响的函数是时钟节拍,时钟节拍的中断服务子程序需要遍历所有使用延迟函数的任务,故执行时间与任务数目有关,为非固定值。此外,时钟节拍的频率也不能太高,否则会因为CPU频繁加载中断服务子程序,导致加重了CPU负荷,影响μC/OS-II的实时性。

Freescale公司的16位HCS12X(简称“S12X”)系列单片机引入了一个协处理器,名为“XGATE”。与普通意义上的浮点协处理器不同,这个协处理器主要用来处理中断。如果采用协处理器来处理μC/OS-II时钟节拍的中断,那么主CPU无需频繁加载中断服务子程序,从而保证μC/OS-II内核的所有函数执行时间都为固定值。这样,μC/OS-II的实时性就得到了保证,还能以提高时钟节拍中断频率的方法提高应用系统定时的精度。

1 单片机中的协处理器

HCS12X系列单片机中的XGATE协处理器是精简指令集(RISC)结构的处理器,它的工作时钟频率是S12X主CPU的2倍。主CPU初始化系统时可决定使用或禁用XGATE。若使用,则XGATE在初始化后就独立地运行,并通过双端口RAM与CPU交换数据,必要时向主CPU发中断请求。

XGATE处理完所有的中断后进入休眠态,停止运行,直到下一次中断发生。XGATE比较适合响应的中断主要是加载频率高的中断,或不带通信缓冲区的I/O中断,例如SCI发送或接收中断、PWM输出中断等。而对于本身带发送、接收缓冲区的中断(如CAN中断、USB中断等),采用协处理器处理中断优势不明显。

μC/OS-II的时钟节拍中断是一个频繁发生的中断,所以很适合采用XGATE来响应。以下重点介绍如何用XGATE协处理器响应μC/0S—II的时钟节拍中断。

2 用XGATE实现μC/OS-II的时钟节拍

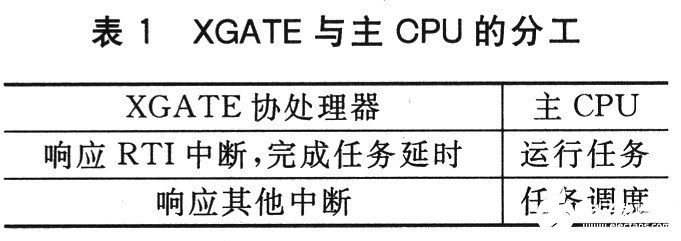

μC/0S-II的时钟节拍中断可以采用单片机的实时中断(Real-Time Interrupt,RTI)来实现。当然也可以使用定时器中的计数器来产生时钟节拍,原理相同,方法近似。使用XGATE来响应RTI中断,实现时钟节拍时,XGATE协处理器和主CPU的分工如表1所列。

XGATE负责响应RTI中断,实现时钟节拍,并完成任务延时计数;在任务延时完成后,通知CPU进行任务调度。另外,XGATE还用来响应其他中断,在需要任务调度时通知CPU。主CPU则只负责运行任务(包括系统任务)和任务调度,只有在需要任务调度时才会加载中断服务子程序。使用XGATE来实现时钟节拍的具体设置步骤如下所述。

2.1 将RTI中断的控制权交给XGATE

为了将RTI中断交由XGATE来处理,系统初始化时需要设置S12X单片机中RTI中断对应的中断控制寄存器。中断控制寄存器组成如下:

在S12X单片机中,每一个I/O中断都有一个中断控制寄存器与之对应。中断控制寄存器控制相应的中断是由S12X CPU响应还是由XGATE来响应,以及该中断的优先级。

中断控制寄存器中,RQST位为1时,中断由XGATE来响应;为0时,中断由S12X CPU响应。为了使用XGATE来响应RTI中断,需要将RTI中断对应的中断控制寄存器的RQST位置1。PRIOLVL[2:0]保存的是对应中断的优先级,值越大,对应中断的优先级越高。如果这3位均为0,那么对应中断会被禁用。

设置中断控制寄存器可以调用编译器提供的一个函数ROUTE_INTERRUPT。这个函数需要的参数是对应中断的中断向量相对中断向量表基址(0xFF00)的偏移量,以及中断控制寄存器的值。设置RTI中断控制寄存器的代码如下:

RUUTE_INTERRUPT (0xF0,0x81);

其中,0xF0是RTI中断向量相对中断向量表基址的偏移量,0x81是要设置的中断控制寄存器的值。

2.2 XGATE与S12X CPU的数据共享

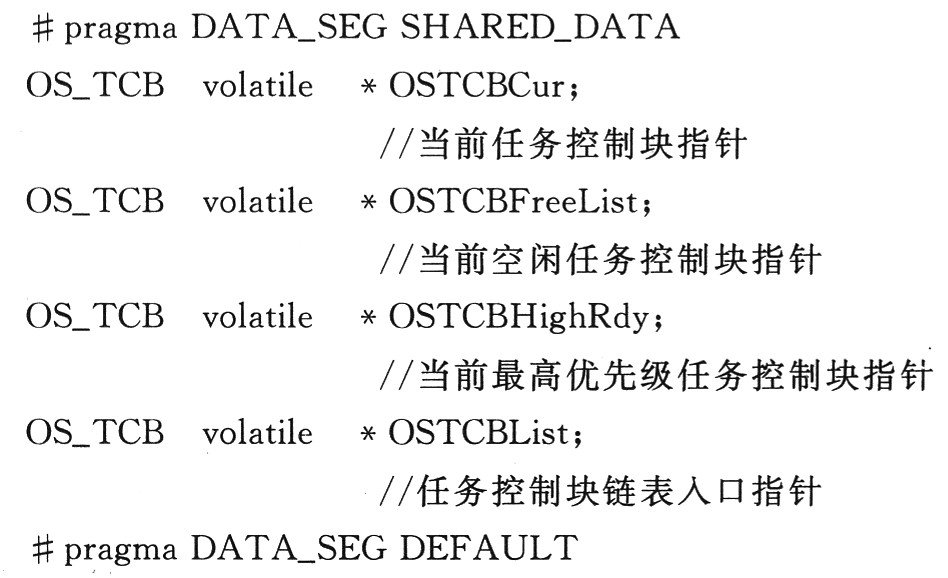

XGATE实现μC/OS-II的时钟节拍和S12X CPU实现任务调度,都需要访问与系统的任务控制块链表相关的变量,因此这些变量需要声明为XGATE和S12X CPU的共享变量。共享变量的声明需要加上“volatile”类型声明,并使用“#pragma”预处理命令将其放在共享内存中。

S12 CPU的程序中声明如下:

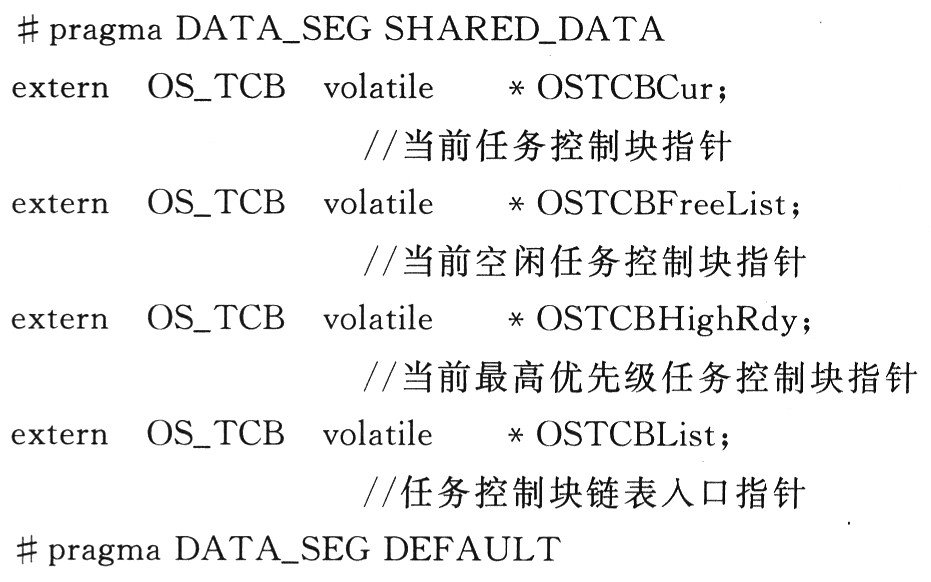

在XGATE的程序中,需要使用extern声明这些变量,具体语句如下:

2.3 XGATE与S12X CPU的指针变量变换

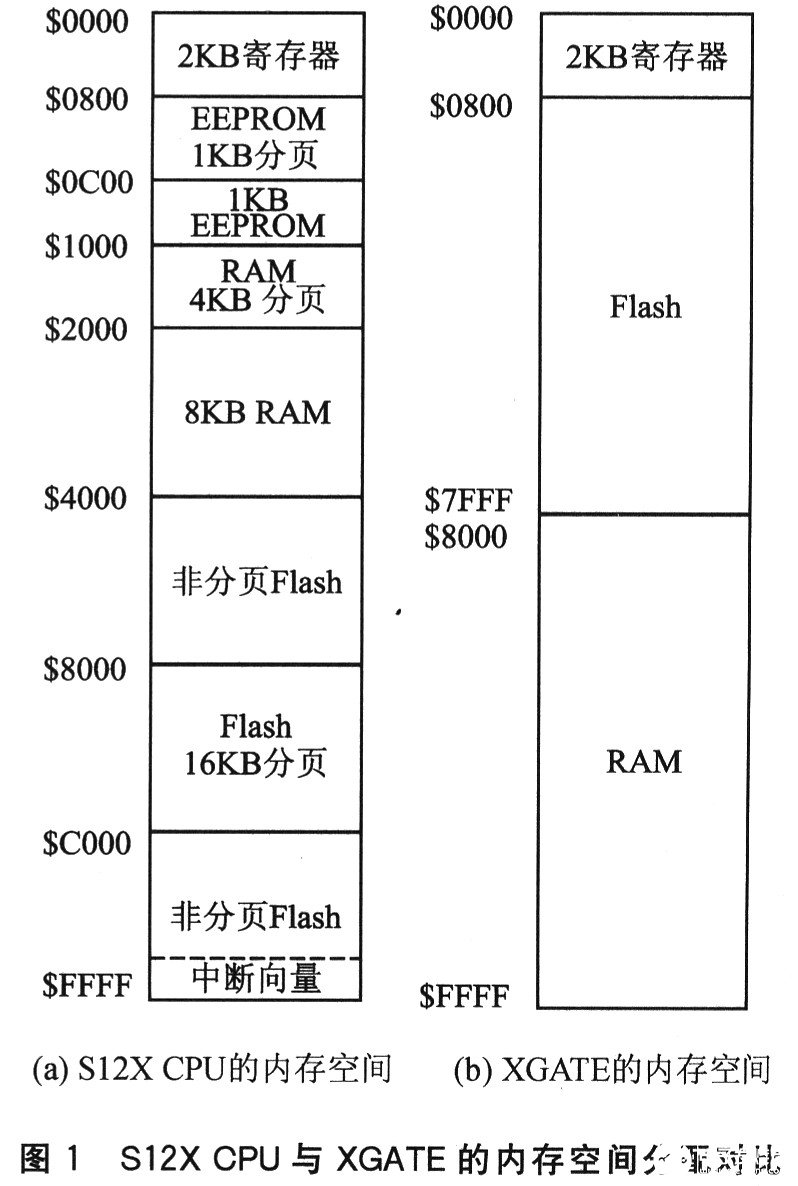

因为XGATE的内存空间编址与S12X CPU的内存空间编址不一样,所以在指针变量共享时会存在问题。CPU的内存空间和XGATE的内存空间的差别如图1所示。

从图1中可以看出,在S12X CPU的寻址空间中,0x1000~0x3FFF为RAM空间;而对XGATE来说,RAM空间的地址范围为Ox8000~0xFFFF。如果XGATE的程序直接使用CPU的指针变量,则会导致XGATE访问地址空间0x1000~0x3FFF,该区域对于XGATE是Flash,从而出错。为了正确地共享指针变量,在XGATE中使用S12x CPU的指针变量时,需要对指针变量进行变换。S12X系列中不同单片机成员的地址分配可能有所不同。以MC9S12XDT512单片机为例,其内部共有8 KB非分页RAM,可全都设为S12X CPU和XGATE的共享内存。这8 KB RAM在S12X CPU中的地址为0x2000~0x3FFF;而在XGATE中的地址为0xE000~0xFFFF,地址偏差为0xC000。因此,在XGATE使用S12X CPU的指针变量时,将指针变量的值加偏移量0xC000,就可以在XGATE程序中正常使用。

下面是XGATE程序中一个指针变量变换的代码:

在XGATE协处理器中有8个寄存器,编译器使用其中的R1来传递参数,上面程序中的R2、R3是8个寄存器中的另外2个。

2.4 XGATE与S12X CPU的通信

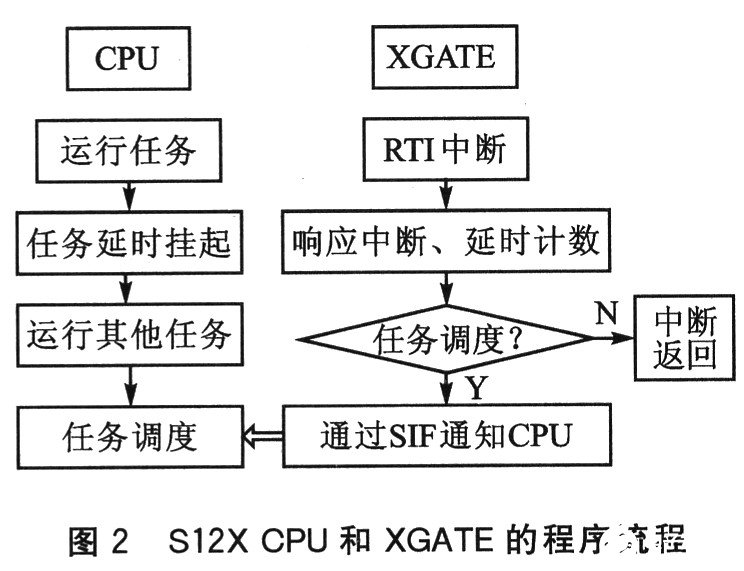

XGATE处理RTI中断时先完成指针变换,然后遍历μC/OS-II的所有任务控制块链表,对需要延时的任务进行延时计数器减1操作。若无需任务调度,则XGATE回到休眠态,直到响应下一次中断。仅当某任务延时计数器递减到零时,该任务进入就绪态,需要任务调度时才通知S12X CPU进行任务切换。

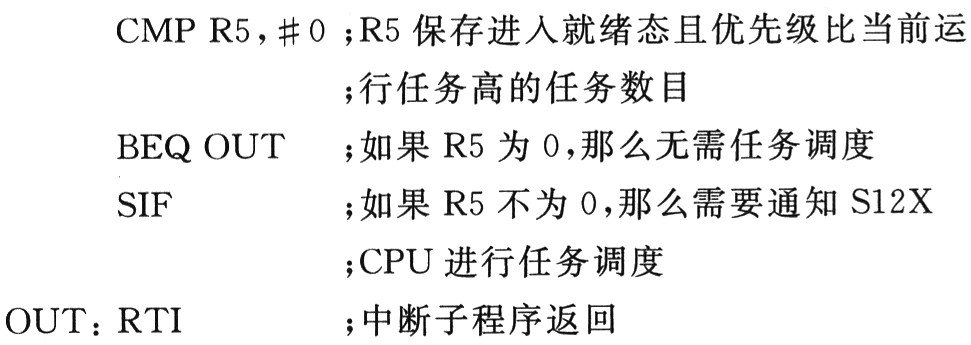

在XGATE的中断服务子程序中,中断标志指令SIF用于向S12X CPU发出中断请求。该指令置位中断标志位,请求S12X CPU继续响应本次RTI中断。在XGATE的中断服务子程序中使用SIF 指令的代码如下(其中R5是协处理器XGATE的8个寄存器之一):

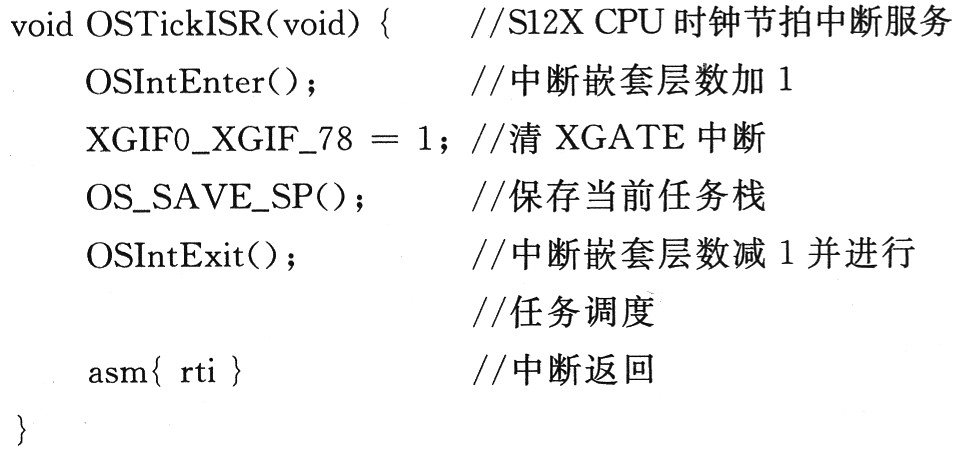

由于遍历任务控制块链表和各任务延时计数器减1的操作,以及无需任务调度的RTI中断响应都由XGATE完成了,S12X CPU只需要响应确实需要进行任务调度的RTI中断,使其中断服务子程序大大简化:

这样,CPU的RTI中断服务子程序所要执行的代码是固定的,每次的运行时间也是固定值,因而μC/OS-II的实时性得到了确切的保证。

S12X CPU和XGATE的程序流程如图2所示。

2.5 设置XGATE向量表

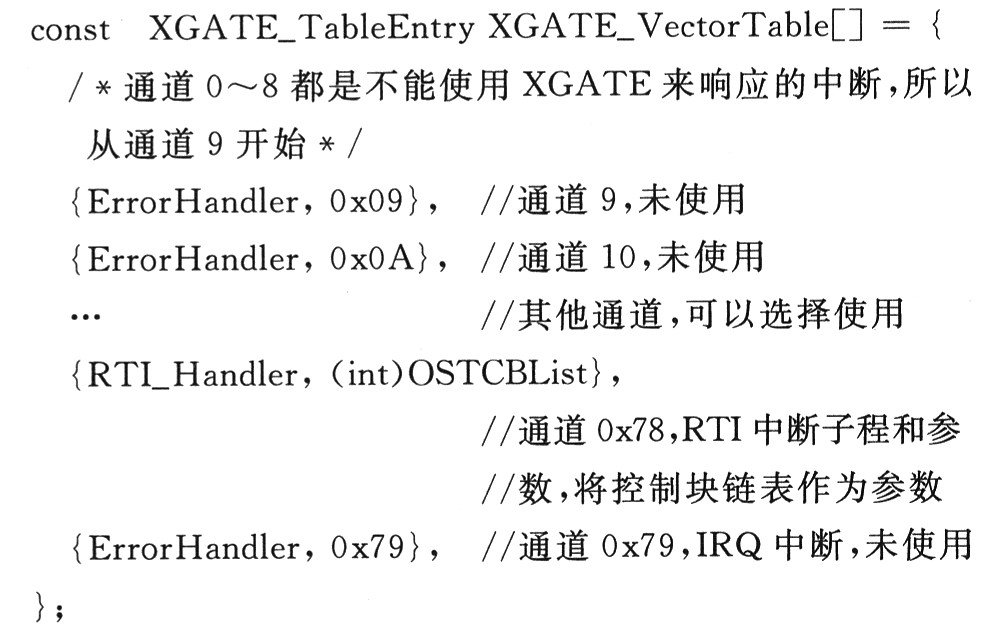

为了使XGATE正常响应中断,需要把XGATE的RTI中断服务子程序地址写到XGATE的中断向量表中。XGATE的中断向量表的写法与CPU的中断向量写法类似,只是XGATE的中断子程序可代入一个参数,需要将这个参数也写入中断向量表。

在XGATE中断向量表的确定位置,写入RTI中断服务子程序地址和参数变量,就可以使XGATE在响应RTI中断时进入RTI中断服务子程序。

XGATE的中断向量表的写法如下:

其中,OSTCBList是XGATE响应RTI中断时需要带入的参数,这里这个参数是μC/OS-II任务控制块链表的首地址;XGATE_TableEntry是一个编译器自定义的结构体变量类型;XGATE_VectorTable[]是XGATE的中断向量表。写好XGATE的中断向量表后,使用XGATE实现μC/OS-II时钟节拍的设置过程就完成了。

3 效果测试与分析

为了验证用协处理器处理时钟节拍中断的效果,进行如下测试:在同-S12x单片机上,分别使用和不使用XGATE处理μC/OS-II的时钟节拍中断。在两种情况下,建立同样的10个任务,时钟节拍中断服务子程序中同样只进行任务控制块链表遍历和延时计数器减1,不做任务调度。这样,μC/OS-II中会有一个任务总处于就绪态并一直运行,这个一直运行的任务会通过循环计数的方法在一个I/O端口上输出一个方波。在同样的总线时钟和同样频率的时钟节拍下,比较两种μC/OS-II输出的方波周期的差别。

测试的目的是,观察μC/OS-II的时钟节拍中断服务子程序的加载,对正在系统中运行的任务的影响。为了与XGATE处理任务控制块链表遍历和延时计数器减1进行对比,未使用XGATE的μC/OS-II中,S12X CPU的时钟节拍中断服务子程序只保留与XGATE同样的操作。没有任务调度,也方便对系统中正在运行的任务输出的方波进行观察。

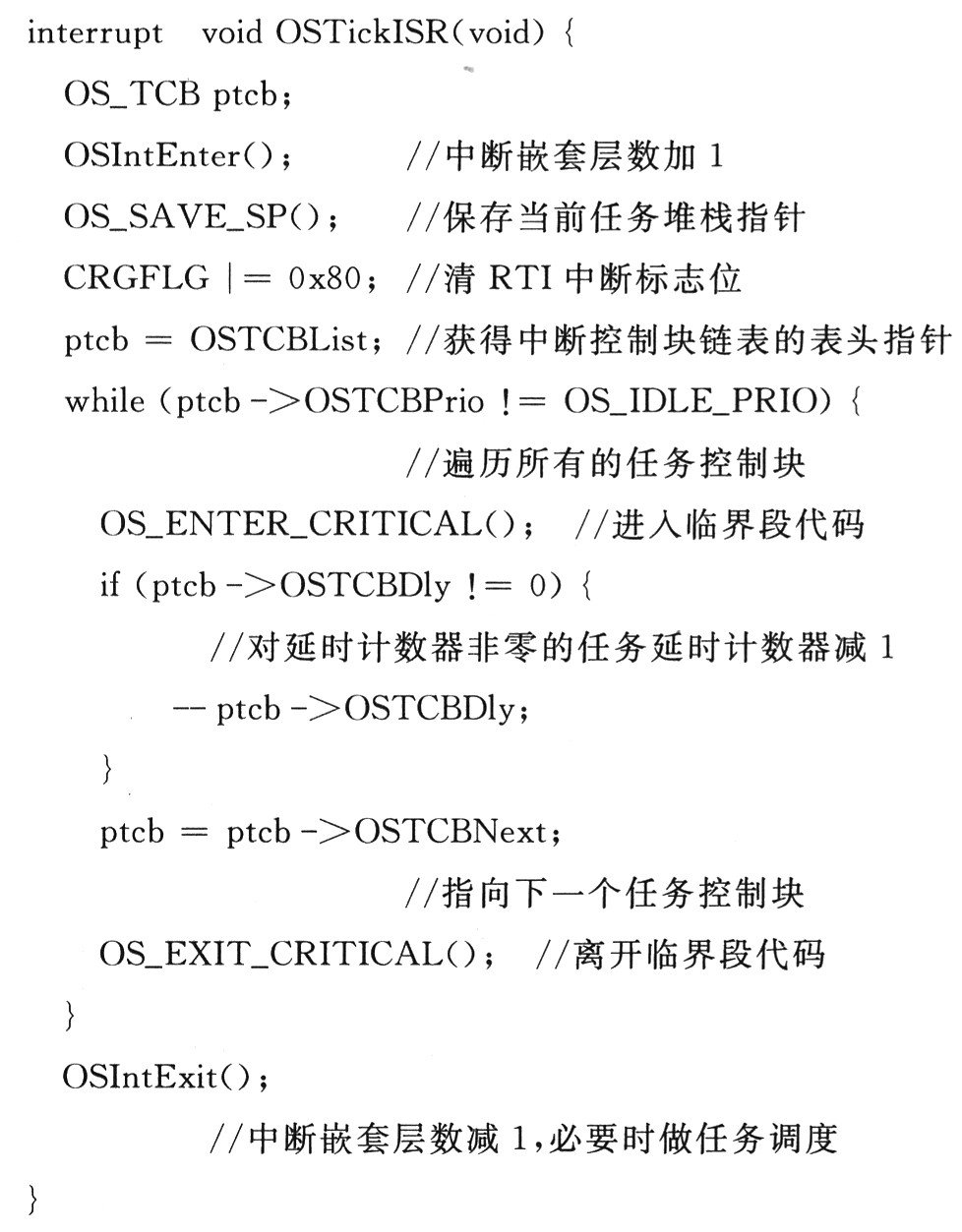

在不使用的XGATE的μC/OS-II中,S12X CPU的RTI中断的中断服务子程序代码如下:

以上S12X CPU中断服务子程序共有220条指令,需运行538个周期。测试中采用了16 MHz的总线时钟和16 kHz的μC/OS-II时钟节拍。可以估算出,每次中断服务子程序在S12X CPU中的运行时间为33.6 μs,约相当于62.5μs时钟节拍的53%,即S12X CPU需要用一多半的时间响应时钟节拍中断,这显然是不可取的。

在μC/OS-II中用XGATE处理时钟节拍中断时,当无需做任务调度时,XGATE遍历10个任务的控制块链表,执行延时计数器减1操作,共需要148条指令。由于XGATE是RISC结构的处理器,指令执行时间多为1~2个周期,故执行148条指令共需要218个周期。在32MHz时钟频率下,执行时间大约7μs,仅相当于62.5 μs时钟节拍的11%。这说明,即使使用短至62.5μs的时钟节拍,对XGATE的占用率也并不高。

通过以上测试可看出,由单一CPU运行μC/OS-II,16 kHz的时钟节拍导致S12X CPU频繁地加载中断服务子程序,占用超过了50%,严重地影响了任务的实时运行。故对于单一CPU,一般采用的时钟节拍频率不高于100 Hz,此时计时精度为±10 ms,以避免时钟节拍中断占用大量CPU运行时间。

在用XGATE处理μC/OS-II的时钟节拍时,16 kHz的时钟节拍并未对S12X CPU的任务运行产生影响,这个频率的时钟节拍使μC/OS-II的定时精度高于±62.5 μs。利用协处理器XGATE来处理μC/OS-II的时钟节拍,使主CPU的执行时间为固定值,因而保证了任务的实时运行,提升了系统实时性,高频率的时钟节拍也提高了计时精度。

4 结 论

μC/OS-II中,时钟节拍中断服务子程序需要遍历整个任务控制块链表,不同应用中任务数目不同,遍历整个任务控制块链表所花费的时间就不同。时钟节拍中断所带来的不确定性是影响μC/OS-II实时性指标的唯一因素。采用协处理器来实现μC/OS-II的时钟节拍可以很好地解决这个问题。

如果使用协处理器来响应μC/OS-II的时钟节拍中断,那么μC/OS—II任务控制块链表的遍历和延时计数器减1操作均由协处理器完成。主CPU只有在需要做任务调度时才会进入相应的中断服务子程序,因此主CPU运行中断服务子程序的时间是固定值。由于主CPU的运行时间不会被时钟节拍中断占用,因而可以采用很高频率的时钟节拍来提高μC/OS-II的计时精度。

责任编辑:gt

-

如何利用S12X单片机去实现串口空闲中断接收呢2021-12-10 715

-

单片机的处理器2021-11-19 1367

-

51单片机——定时器的原理和使用2021-11-10 1092

-

MC9S12X系列 双核MCU协处理器(Xgate) 学习笔记2021-11-06 707

-

飞思卡尔9S12X系列双核中的协处理器XGATE使用方法2011-12-22 2205

-

HCS12微控制器原理及应用_王威2011-11-30 1033

-

利用XGATE进行Manchester译码2011-11-11 945

-

如何在S12X上配置及使用XGATE2011-04-11 1193

-

HCS08系列单片机的低功耗特性2010-09-19 851

-

freescale单片机区别2010-07-07 5812

-

如何使用S12X MCU上的外设协处理器XGATE2010-04-01 1049

-

ARM处理器与单片机性能比较2010-02-09 875

-

HCS12X系列存储器配置操作指南2010-01-11 723

-

用协处理器提高μC/OS-II的实时性2009-03-29 932

全部0条评论

快来发表一下你的评论吧 !