STM32系统架构

描述

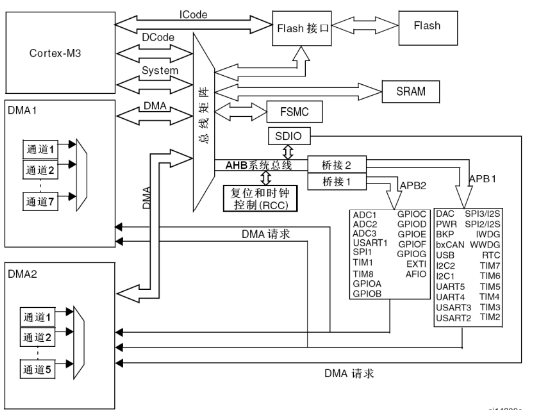

在小容量、中容量和 大容量产品中,主系统由以下部分构成:

● 四个驱动单元:

─ Cortex-M3内核DCode总线(D-bus),和系统总线(S-bus)

─ 通用DMA1和通用DMA2

● 四个被动单元

─ 内部SRAM

─ 内部闪存存储器

─ FSMC

─ AHB到APB的桥(AHB2APBx),它连接所有的APB设备

这些都是通过一个多级的AHB总线构架相互连接的,如下图所示:

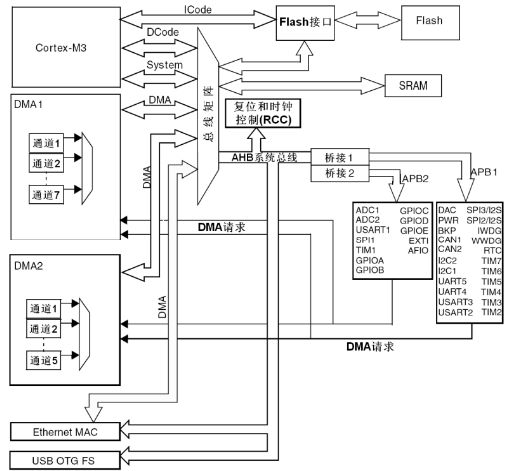

在互联型产品中,主系统由以下部分构成:

● 五个驱动单元:

─ Cortex-M3内核DCode总线(D-bus),和系统总线(S-bus)

─ 通用DMA1和通用DMA2

─ 以太网DMA

● 三个被动单元

─ 内部SRAM

─ 内部闪存存储器

─ AHB到APB的桥(AHB2APBx),它连接所有的APB设备

这些都是通过一个多级的AHB总线构架相互连接的,如下图所示:

ICode总线

该总线将Cortex-M3内核的指令总线与闪存指令接口相连接。指令预取在此总线上完成。

DCode总线

该总线将Cortex-M3内核的DCode总线与闪存存储器的数据接口相连接,常量加载和调试访问。

系统总线

此总线连接Cortex-M3内核的系统总线(外设总线)到总线矩阵,总线矩阵协调着内核和DMA间的访问。

DMA总线

此总线将DMA的AHB主控接口与总线矩阵相联,总线矩阵协调着CPU的DCode和DMA到SRAM、闪存和外设的访问。

总线矩阵

总线矩阵协调内核系统总线和DMA主控总线之间的访问仲裁,仲裁利用轮换算法。在互联型产品中,总线矩阵包含5个驱动部件(CPU的DCode、系统总线、以太网DMA、 DMA1总线和DMA2总线)和3个从部件(闪存存储器接口(FLITF)、 SRAM和AHB2APB桥)。

在其它产品中总线矩阵包含4个驱动部件(CPU的DCode、系统总线、 DMA1总线和DMA2总线)和4个被动部件(闪存存储器接口FLITF、 SRAM、 FSMC和AHB2APB桥)。

AHB外设通过总线矩阵与系统总线相连,允许DMA访问。

AHB/APB桥(APB)

两个AHB/APB桥在AHB和2个APB总线间提供同步连接。APB1操作速度限于36MHz, APB2操作于全速,最高72MHz。在每一次复位以后,所有除SRAM和FLITF以外的外设都被关闭,在使用一个外设之前,必须设置寄存器RCC_AHBENR来打开该外设的时钟。当对APB寄存器进行8位或者16位访问时,该访问会被自动转换成32位的访问:桥会自动将8位或者32位的数据扩展以配合32位的向量。

-

STM32F0产品系统架构ARCHITECTURE2023-08-01 589

-

STM32单片机系统架构。#单片机 #STM32 #系统架构 #电子技术#单片机开发 #ARM白加黑 2023-06-20

-

AN4667_STM32F7系列的系统架构和性能2022-11-21 383

-

STM32系统架构#工作原理大揭秘 #芯片笑君愁 2022-07-21

-

STM32时钟系统有哪些性能呢2021-12-14 1564

-

STM32系统架构的相关资料推荐2021-12-10 973

-

STM32WB系统有哪些硬件呢2021-11-15 2047

-

浅析ARM架构与STM32系统架构2021-10-20 2339

-

STM32f1库函数开发学习2021-09-24 860

-

STM32F1开发指南笔记3----STM32系统架构 & 时钟系统 精选资料分享2021-08-23 883

-

STM32f1库函数开发学习软件2021-08-02 1537

-

STM32系统架构2021-07-22 1753

全部0条评论

快来发表一下你的评论吧 !