采用RTL代码描述位宽相同的两个数相加或相减

描述

本文用的芯片型号为xcku115-flvd1924-1L-i,时钟频率为400MHz。

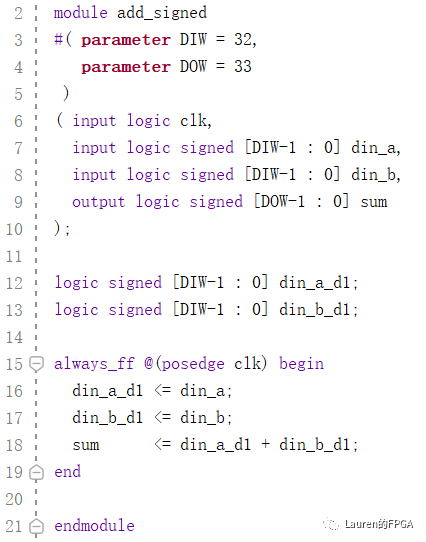

两个有符号数相加

采用RTL代码描述位宽相同的两个数相加或相减,无论是有符号数还是无符号数,Vivado综合后的结果是一致的。以32bit数据为例,相应的代码如下图所示。这里考虑到两个32bit数据相加其结果可能为33bit,同时对于高速设计(时钟频率至少400MHz)为了满足性能,对输入和输出分别添加了流水寄存器。

最终的资源利用率如下图所示。

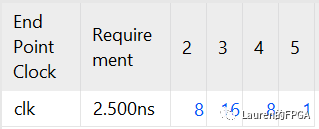

从逻辑级数的角度看,逻辑级数最大为5(有一条),大多数路径为3,如下图所示。

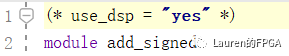

从综合属性角度看,可以通过use_dsp属性使得该加法操作映射到DSP48中,该属性的使用方法如下图所示。

采用DSP48实现时,上述代码可达到完全映射,不会消耗SLICE中的任何资源。假定时钟频率为400MHz,对比使用LUT+FF和DSP48两种实现方式,不难看出后者在时序(逻辑级数降低至1)和功耗方面均有优势。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

如何把两个数据返回给调用函数2025-01-08 958

-

labview怎么查数组中相同元素的个数2023-12-28 6608

-

python中如何交换两个数的值相加2023-11-29 1537

-

python中如何交换两个数的位置2023-11-22 4310

-

两个相同电路的电流是否相等?2023-03-10 2780

-

基于FPGA的多路选择器设计(附代码)2023-03-01 2200

-

请教大家关于两条曲线相减的问题2021-08-28 4563

-

写RTL代码时,尽可能地做到代码风格与硬件结构相匹配2020-09-24 4069

-

Labview一维数组相同元素去重及相同元素个数源代码免费下载2020-08-31 2697

-

如下图所示,请问Labview两个数相加出现了负数是为什么?如何解决?2018-07-03 4804

-

两个一维数组中相同元素的个数2016-04-07 8307

-

怎样将两个数组比较2012-04-18 3778

-

用两个全加器构成二一十进制相减器2009-04-09 1305

全部0条评论

快来发表一下你的评论吧 !