一款针对Soc开发的硬件仿真进行优化的软件VARON

电子说

描述

VARON是一款针对Soc开发的硬件仿真进行优化的软件,运行于Cent OS Linux系统,需要有一定的VCS使用基础,适用于集成度偏高的Soc开发。VARON通过自主研发的IP连接到开发系统,并监视AXI总线上的多种属性和性能,从而使开发者能够更直观的观测系统的运行情况,从而有针对性的进行优化调整。

背景

1.芯片现状:

1)许多IP嵌入

2)更复杂的交互

3)准确的性能分析至关重要

2.开发会遇到的问题

1)需要验证IP用于模拟和仿真,以及丰富的调试工具 2)学习如何使用验证IP和调试工具是一个很大的挑战 3)没有性能分析方面的专业知识,也不知道从哪里开始 4)想用运行软件调试FPGA或ASIC芯片的性能,但主要厂商不提供 5)处理大量信号级数据的速度慢 6)用于性能分析工具和工作的总成本很高

3.市面上大多数分析仪

1)性能低下: ①需要验证IP用于模拟和仿真,以及丰富的调试工具 ②不支持FPGA和ASIC ③处理大量信号级数据的耗时 ④劳动力成本高 2)难以使用: ①手动实施验证IP ②需要性能分析方面的专业知识,使用有限类型的图表和使用工具的诀窍

VARON分析仪

1.高性能:

1)一个完整的产品,带有可配置的片上验证IP和专有图形用户界面 2)支持模拟仿真、FPGA和ASIC

3)专用于事务级数据的性能分析非常快速

4)劳动成本低,实现时间短

2.易于使用:

1)自动引导验证IP的配置

2)通过丰富的图表和工具提示引导分析

VARON的优势

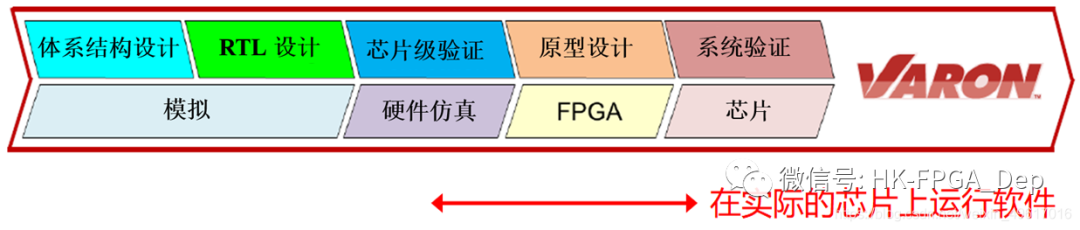

1.涵盖LSI设计验证的整个过程

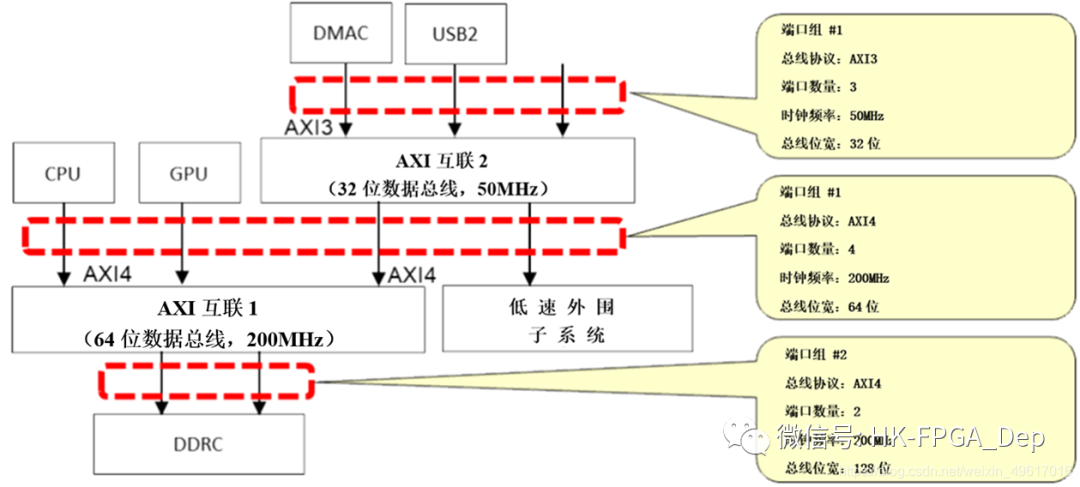

2.完全可配置的验证IP满足用户需求

1)按端口组进行独立配置 2)易于分析系统中跨总线级联的事务

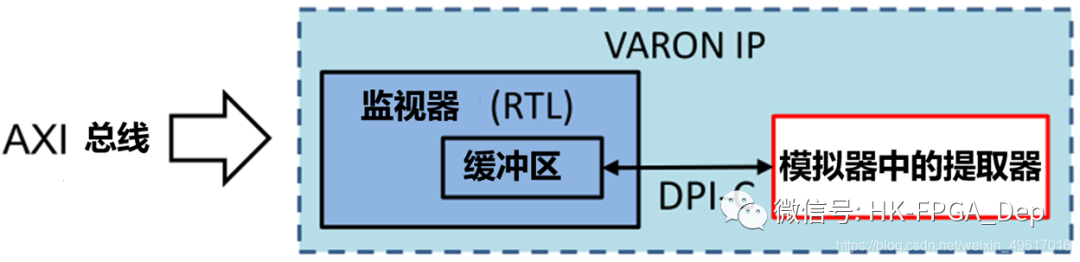

3.针对硬件仿真器进行了优化,以最大限度地提高速度

1)硬件IP将AXI数据缓冲到模拟器 2)监视器和缓冲区都是可综合的

4.分析时间短,数据处理速度快

1)在事务级别监视AXI 2)快速显示所有性能图表,不依赖于设计尺寸

| AXI周期 | 1,000,000 | 10,000,000 | |

| 分析时间(秒) | 8 | 95 | |

| 文件大小(字节) | 47,955,968 | 480,460,800 | |

| 处理数量 | 读 | 377,007 | 3,776,145 |

| 写 | 381,075 | 3,820,338 | |

| 数据传输总量(字节) | 读 | 9,186,842 | 92,111,540 |

| 写 | 9,291,924 | 93,326,480 |

5.通过丰富的性能图表组合进行非常简单的分析

1)每个端口组20个图表 2)通过6种图表类型了解2个分析目标的5个关键设计标准

| 目标 | 设计准则 | 图表类型 | 备注 |

| 响应时间 | 按端口或ID列出的延迟 | 直方图 | 延迟分布 |

| 最大值/最小值/均值 | |||

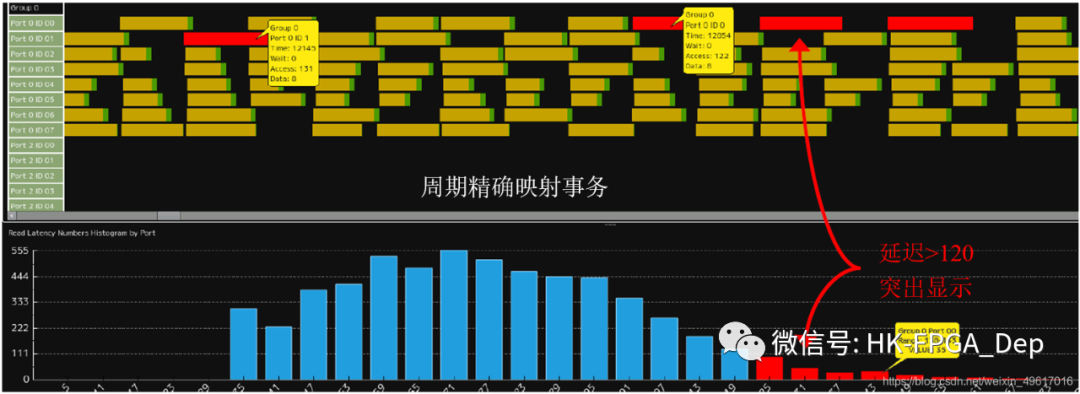

| 按端口或ID列出的事务 | 时间图 | 随着时间的推移,循环准确地映射事务 | |

| 总线使用效率 | 按端口或ID列出的数据传输总量 | 圆形分格统计图表 | 空闲周期—>总线利用率 |

| 条形图 | 端口或ID之间的比较 | ||

| 按端口或ID的突发长度 | 直方图 | 突发长度分布 | |

| 按端口或ID列出的单位时间的数据传输量 | 堆叠时序图 | 一段时间内所有端口或所有ID的总数据传输量 | |

| 条形时序图 | 每个端口或ID随时间的数据传输量 | ||

| 最大值/最小值/均值 | |||

| 直方图 | 数据传输量分布 |

6.工具帮助用户进行详细的调试

1)放大/缩小以验证整体趋势 2)放大/正常大小,跳转到时间和工具提示来检查本地数据

单位时间的数据传输量:正常大小(左)、放大(右)

3)水平能够同步显示3个时序图,以在一个时间窗口内验证相关数据

按条形图显示单位时间的数据传输量(上)

堆叠视图显示单位时间的数据传输量(中)

事务时间表(下)

4)找出超出范围来突出显示5个图表中超出预期的数据

延迟直方图、事务时序图、堆叠/条形图时序图和单位时间数据传输周期直方图

事务时间表(上)

延迟直方图(下)

5)由图表设计的工具提示,用于感兴趣的详细数据 ①左键单击出现,右键单击锁定/移动/删除 ②上图例子:

延迟直方图:在端口0有35个事务,延迟为138–143

事务时序图:端口0: ID 01事务开始于时间12和145,具有0等待、131访问(延迟)和8字传输

介绍完功能后,下篇文章我们根据实际案例来具体分析。

责任编辑:xj

原文标题:AXI总线高性能分析仪——VARON(一)

文章出处:【微信公众号:FPGA技术支持】欢迎添加关注!文章转载请注明出处。

-

这些电源常用仿真软件,你都知道吗?2024-10-25 4353

-

PCB仿真软件有哪些?PCB仿真软件是如何进行LAYOUT仿真的?2023-11-24 17997

-

介绍一款功能强大的EtherCAT网络仿真软件2023-08-09 2658

-

一款好用的仿真软件2023-02-15 1570

-

开发一款射频SOC蓝牙芯片2021-11-10 1611

-

怎样挑选一款MCU平台进行嵌入式系统开发2021-11-03 1685

-

【fpga仿真辅助工具】AXI总线性能监测&分析工具——varon2020-11-02 2979

-

VARON的设计流程2020-10-25 1599

-

VARON总线验证技术2020-09-28 3155

-

求一款针对音频的通道切换的芯片2019-05-10 6522

-

能介绍一款电路仿真软件吗2019-01-21 3076

-

【InTime试用体验】使用简易、策略选择精确度高的一款时序优化软件2017-07-05 9913

-

4nec2_一款天线仿真软件2015-10-09 1907

-

一款英国大学所用的硬件仿真小软件(特别好用)2012-06-13 29885

全部0条评论

快来发表一下你的评论吧 !