基于Virtex-5 LX110验证平台实现FPGA性能的硬件系统设计

可编程逻辑

描述

目前ASIC设计的规模在不断扩大、复杂度在不断增加,与此同时,日益激烈的竞争使得今天的电子产品市场对产品进入市场的时间极为敏感。如何提高验证的效率已成为一个巨大的挑战。当前对ASIC设计者开放的3个主要验证选择是仿真(emulation)、模拟(simulation)和FPGA原型(prototypes)开发。随着FPGA的门数越来越高,功能越来越强大,使其成为了ASIC验证的强有力工具。

Virtex-5 LX系列是Xilinx公司推出的新一代65nm工艺FPGA。它与上一代90 nm的FPGA相比,速度平均提高30%,容量增加65%;同时动态功耗降低35%,静态功耗保持同样低,使用面积减小45%。Virtex-5 LX系列还通过性能优化的IP模块拥有了550 MHz时钟技术。高性能的SelectIO特性,提供了到667 Mbps DDR2SDRAM和1 200 Mbps QDR II SRAM等外部存储器的最快连接。

本文基于Virtex-5 LX110验证平台的设计,探索了高性能FPGA硬件系统设计的一般性方法及流程,以提高FPGA的系统性能。

1 系统设计实现

利用FPGA可以很好地对ASIC的功能进行验证。通过常年对AISC原型验证平台的设计和测试发现,对于某些ASIC,特别是用于通信领域的ASIC,如果能够在原型验证阶段就可以在实际环境中对其性能进行严格的评估,对其采用的算法进行验证,便能够很好地保证芯片的性能,从而加快产品的上市时间。利用通用的FPGA验证平台,例如DiniGroup,其价格昂贵且与系统进行互联也比较困难,不满足对系统进行现场测试的高度集成性和便携性的要求。解决这一问题的最好方法就是,根据需求直接将FPGA集成到系统当中,设计出适用于现场评估测试的单板验证平台。

1.1 系统资源评估

(1)FPGA资源

Virtex-5 LX110包含17 280个Slice,110 592个log—ic cell,12个DCM和6个PLL;提供高达800个I/O引脚,23个I/O板块,其中每个I/O都可设置成差分输出。LX110支持多种I/O类型,需要根据系统不同模块的输入/输出特性选择合适的I/O类型,并将所用到的I/O进行合理的布局规划。各种不同I/0类型的电气特性约束严格限制了引脚位置的指定,同时I/O引脚的引出位置影响到BGA封装的板级走线,因此需要综合考虑以便对I/O引脚资源进行合理的划分。

(2)时钟分布

系统中的时钟信号通常是串扰和EMI问题的根源,因此需要对其进行合理的规划。时钟信号的完整性是保证系统正常工作的重要因素,在仿真中特别需要关注。利用FPGA提供的DCM资源可以减少系统所需的时钟信号器件,从而减少板级时钟网络。PCB布线时应注意将时钟信号和数据信号进行隔离,以避免串扰的产生。

(3)FPGA配置模块

设计合理、适用的FPGA配置方案。Virtex-5提供的配置模式多达8种,本设计选用Xilinx公司提供的PROM配置芯片,通过JTAG接口将配置文件写入PROM中,系统上电后FPGA和PROM按所设定的配置模式将配置文件从PROM下载到FPGA里,利用FPOA+PROM的组合可以有效地简化配置电路设计。此外还可以通过JTAG接口对FPGA进行在线配置。

(4)模数转换模块

系统集成高速双路模数转换器,支持高达105 Msps的采样速率,每路10位输出。

(5)I/O接口模块

系统为各种不同的I/O类型提供了相应的接口,支持LVCMOS33、LVCMOS25、LVDS_25类型的I/O。

(6)电源管理模块

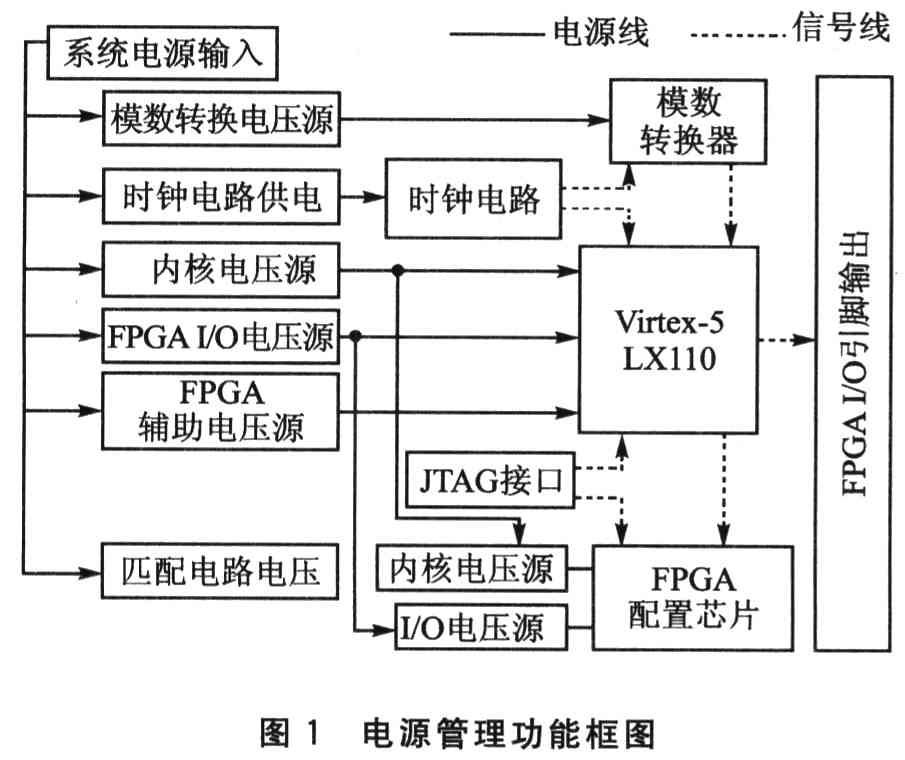

FPGA所需电源主要有3个:内核电压(VCCINT)、I/O电压(VCCO)、辅助电路电压(VCCAUX)。其他如A/D电压、FPGA配置芯片电源(内核电压和I/O电压)、板级所需的时钟电路供电及指示灯供电电压,总共需提供8个电源。系统功能框图如图1所示。

1.2 原理图符号生成

FPGA的可定制特性需要按特定应用进行原理图符号生成。首先,从特殊用途引脚的指定开始,例如电源、地引脚、参考电压引脚以及配置引脚等。只有对这些引脚的正确指定才能保证PCB布板及走线的正确连接。下一步是将逻辑I/0和封装形式连接起来,可以利用FPGA的设计开发环境来指定,然后导入到PCB布板环境中。在FPGA的设计开发环境中,用户可以利用图形界面对引脚进行指定,然后在实现过程中,FPGA布局布线工具能自动地对引脚进行指定。在FPGA的设计开发环境中,能够进行DRC检验以保证引脚的合法性。

接下来为FPGA创建结构化的原理图符号。由于FPGA本身I/0的复杂性和可配置性,将整个FPGA分割为多个子模块能够有效地减轻设计的复杂度,也便于管理和检查。图2显示了利用Mentor Dxdesigner’原理图符号生成向导生成模块化原理图符号的设计过程。原理图符号生成之后就可以在原理图设计环境进行原理图的设计,指定各个模块的连接关系。

1.3 PCB叠层定义

对。PCB叠层、材料和尺寸的设计需要考虑以下因素:

◆走线层的数量需要考虑到封装特性、设计所用的I/()数目以及间距;

◆芯片互联线的数据传输速率,信号的上升、下降时间对PCB材料、尺寸以及走线方式和制板工艺的限制;

◆元件所需的不同供电和参考电压,对电源层的规划和设计;

◆成本问题(利用盲孔、盲埋孔、微通孔等工艺能有效地减少叠层数目,以达到降低成本的目的)。

该设计中,与FPGA互联的信号线约为130条,包括配置电路信号线、时钟信号线及其他I/O信号。选用上下两个走线层。考虑到多个电源供电,设置2个电源平面、2个地平面。整个PCB采用6层板结构设计,信号层目标阻抗50 Q。

利用HyperLnyx叠层设计如图3所示。

1.4 散热管理

FPGA支持的速率越高,本身的资源密度越大,因此要关注应用中的散热管理问题。对FPGA的功率消耗进行估计,以决定是否需要散热系统。

XPower Estimater是一款基于Excel的软件,通过对设计资源的利用,包括逻辑资源、DCM、PLL、I/0类型、触发率(toggling rate),以及其他与FPGA设计密切相关的信息,对FPGA的功耗进行估算。图4为利用XPE进行设计功耗估算的截图。

1.5 信号完整性分析

在时域和频域对设计的连接拓扑结构(PCB叠层、驱动端、接收端、连接器、通孔等等)进行信号完整性分析,目的是要评估和减小信号从驱动端到接收端的反射、串扰以及EMI/EMC等问题。通过仿真分析得到的约束形式能有效指导PCB布局布线工具进行layout设计。进行信号完整性分析,首先要确定与FPGA相接的外围器件的I/O特性及其约束,进而对FPGA采用何种I/0类型以及端接匹配机制有一个大致的了解,然后是通过仿真对采用的I/O类型及端接电路的各个参数进行定义及优化。

(1)前仿真

S1分析一般主要从高速信号、对时序要求较高的信号、走线最长的信号、负载最多的信号开始,因为这些信号线通常最容易引起SI问题。确定关键信号在仿真环境中建立起相应的拓扑模型。

通过仿真能定义出最长连接走线以及其他满足噪声裕量(匹配电路、端接方式等)的网络属性。确定FPGA驱动缓冲特性,例如I/O标准、驱动能力以及回转率,使信号完整性问题、EMI/EMC问题最小化,同样也对接收端I/0属性进行定义。进行串扰仿真以保证相邻走线不会引起串扰问题。定义端节匹配方式。

图5、6是对时钟网络匹配前和匹配后进行的仿真图形对比。

通过前期的大量仿真分析可以很好地保证设计的成功率。

(2)后仿真

在PCB Layout完成之后还需要对整个布好的PCB板进行仿真,后仿真更强调对串扰和EMI的分析,如图7所示。只要任何一个网络不满足设计需求,就需要对该网络进行修改,设计新的走线路径,直至满足设计需求。

1.6 电源分布系统(PDS)设计

PDS分析的目的,是要评估数字器件所需的瞬态电流,以提供一条良好的供电路径。电流路径中的寄生电感是导致供电网络设计失败的根源(例如地弹噪声)。一种可能的情况是,IC信号应当发生翻转时却没有翻转;另一种更常见的情况是引起系统抖动(Jitter)变大,从而导致时序错误。在两种情况中,都将造成系统工作不正常或者超出设计规范定义的范围。

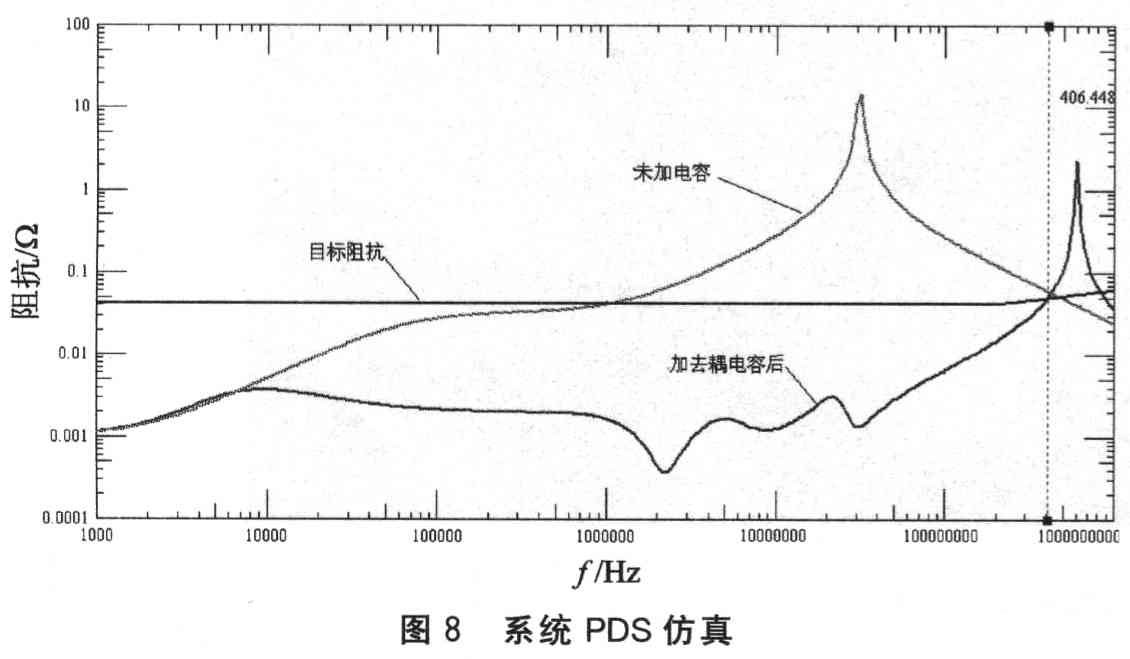

首先检验FPGA的静态和瞬态电流需求,瞬态电流由设计的时钟域、DCM利用率、开关逻辑数目以及同时翻转输出(SimuItaneous Switch Output,SSO)等因素决定,静态和瞬态电流的大小可以利用XPE或XPower来取得。设计满足需求的电源去耦网络,并通过仿真确定所需电容值及其数量,同样,电容在板上的摆放位置对PDS的影响也很重要。图8表明了调整前后电源层阻抗的仿真结果。通过对电源去耦网络的悉心设计,可以有效降低FPGA工作频率范围内的电源阻抗。阻抗越低,意味着系统对瞬态电流的需求越能及时做出反应,因此也越能减小电源的供电噪声。

图8是对电源VCCO对地的频率一阻抗曲线的仿真图。通过对电源去耦网络的设计,可以保证在400 MHz的范围内,电源阻抗值是小于目标阻抗的。

1.7 可测试性设计

随着布线密度的增加,很难对PCB的每个信号都进行物理连接检测,特别是对于BGA封装的芯片。另外,对高速信号添加测试点还会导致信号路径阻抗不连续,引起反射,从而使信号完整性降低。为解决这一矛盾,在设计中首先对FPGA和与其相连的外围电路的每个信号连接生成了一个测试设计,利用FPGA的逻辑资源对FPGA获取到的输入信号与期望的信号值进行比较,对所得的结果通过JTAG端口或者其他外围显示电路(如LED)显示输出。

2 结 论

本文对验证平台硬件设计中的FPGA相关分析进行了详尽描述。目的是通过设计流程前期的大量分析和仿真,将FPGA在整个设计系统的工作特性以及系统环境对FPGA的影响作用进行模拟,得出的结果转化为设计约束导人至PCB Layout的环境中,能有效地提高一次设计成功的机率。按照此流程设计的Virtex-5验证平台工作正常,达到了预期的设计目的。

责任编辑:gt

-

基于直流和开关特性的Virtex-5 FPGA产品介绍2021-07-12 898

-

基于Virtex-5 RocketI0TM GTP收发器实现串行高速接口的开发应用2021-06-24 4108

-

Stratix III FPGA与Xilinx Virtex-5之间有什么不同?2021-05-07 2272

-

如何提高FPGA的系统性能2021-04-26 2474

-

FPGA的硬件电路设计教程和FPGA平台资料简介2020-07-06 2412

-

digilent XUPV5 LX110T开发板介绍2019-11-14 5690

-

如何进行Virtex-5 XC5VLX110T引脚排列?2019-10-25 1670

-

使用ISE处理Virtex 5 LX110T FPGA为什么ISE WebPack中没有可用的选项?2018-12-11 3095

-

WP245 - 使用Virtex-5系列FPGA获得更高系统性能2012-02-17 1363

-

利用Virtex-5 SXT 的高性能DSP解决方案2011-08-20 8527

-

基于Virtex-5 FPGA的音视频监视系统设计2010-11-12 1362

-

Virtex 5LXl10 的ASlC原型开发平台设计2010-02-08 710

-

赛灵思推出高性能DSP平台VIRTEX-5 SXT FPGA2009-11-28 503

-

Xilinx Virtex-5 FXT FPGA开发方案2009-11-24 546

全部0条评论

快来发表一下你的评论吧 !