为嵌入式MRAM选择合适的内存测试和修复解决方案

今日头条

描述

嵌入式内存测试和修复的挑战是众所周知的,包括最大程度地扩大故障覆盖范围以防止测试失败以及使用备用元件来最大程度地提高制造良率。随着有前途的非易失性存储器架构的可用性不断增加,以增加并潜在地替代传统的易失性存储器,新的SoC级存储器测试和修复挑战不断涌现。通过将自旋转移扭矩MRAM(STT-MRAM)作为嵌入式MRAM技术的领先趋势来增强动力,同时考虑了汽车应用的需求。要为嵌入式MRAM选择合适的内存测试和修复解决方案,设计人员需要考虑一些因素,例如在生产测试期间进行修整的特殊需求。

除了在传统存储器中观察到的常规卡死,过渡,耦合,地址解码器和数百种其他故障类型之外,测试嵌入式STT-MRAM存储器IP还需要考虑特定于体系结构的故障,例如编程/擦除掩码和扇区/芯片清除故障。因此,需要通过扩展的基于March的算法类来检测嵌入式STT-MRAM特定的故障,该算法具有用户灵活性,可以指定多个背景图案(例如,实心,棋盘格)以及各种寻址模式(例如,快速列,快速行)来确保最高的测试覆盖率。由于嵌入式MRAM宏的大小很大,因此BIST引擎中需要使用具有较低复杂度的快速算法,以具有可接受的ATE生产/制造诊断测试时间。

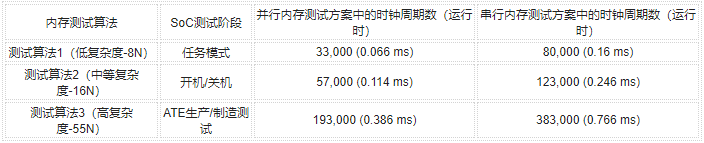

对于汽车环境,SoC设计人员将需要具有灵活性,以在现场运行其他可自定义算法,以匹配系统操作约束。表1显示了如何在复杂的测试阶段中需要执行不同复杂程度的不同算法以匹配系统约束的示例。

表1:选择存储器测试算法的能力对于汽车等应用很重要

*资料来源ITC :汽车SoC中用于嵌入式内存和IP的高级功能安全机制

因此,BIST引擎必须支持扩展的算法类别,以测试特定于MRAM的故障类型,提供灵活性以运行不同的背景模式和寻址模式,并允许用户配置为在SoC的多个测试阶段中执行不同的算法。

fqj

-

嵌入式软件测试与专业测试工具的必要性深度解析2025-09-28 4686

-

低功耗嵌入式计算解决方案:选择处理器的几个关键因素2023-12-04 1460

-

萌新求助,求一个基于嵌入式STT-MRAM的架构方案2021-10-25 957

-

请问怎么设计一种面向嵌入式存储器测试和修复的IIP?2021-04-15 1657

-

单芯片FRAM存储解决方案是嵌入式设计的理想选择2021-03-04 1972

-

嵌入式MRAM的关键应用与制造商2021-01-08 1784

-

MRAM独特功能替换现有内存2020-08-12 2750

-

嵌入式AI解决方案中内存驱动的设计介绍2020-01-27 1875

-

怎样为嵌入式应用选择合适的处理器2019-09-16 1356

-

嵌入式内存测试方案2019-06-27 3232

-

如何为设计应用选择合适的嵌入式MCU2019-02-11 3292

-

怎么选择合适的嵌入式设计软件?2015-05-06 2974

-

最新嵌入式系统数字逻辑测试解决方案2010-12-17 710

-

泰克嵌入式系统及混合信号电路测试解决方案2010-07-26 904

全部0条评论

快来发表一下你的评论吧 !